Processor-specific workflows

This chapter describes the steps to successfully boot up the device to the required security level. It describes the creation of the bootable image, connecting your device, setting up your boot preferences, and writing the image into the selected boot memory. Common steps are described first, followed by device family-specific content. It is assumed that the image is executed on an NXP evaluation board.

This chapter addresses image preparation for the following toolchains:

MCUXpresso IDE 11

Keil Microcontroller Development Kit (MDK) 5 μVision

IAR Embedded Workbench 8

CodeWarrior Development Studio

MCUXpresso for Visual Studio Code (VS Code)

On the following pages, you will learn how to:

Get MCUXpresso SDK with an example project for a processor

Open an example project for the processor in the toolchain

Start with the SEC Tool

Prepare asymmetric keys for the authenticated image

Build a plain image in the selected toolchain

Build a bootable image by SEC Tool

Connect the NXP evaluation board

Write a bootable image into the processor and (optionally) secure the processor and advance the life cycle

Common steps

This section provides common steps of the process.

Downloading MCUXpresso SDK

The MCUXpresso SDK offers open source drivers, middleware, and reference example applications to speed your software development. In this section, you can find information about downloading MCUXpresso SDK as a ZIP package or as a CMSIS pack and how to open an example project from the package. It is recommended to start with iled_blinky example. This example offers a simple check whether the resulting application is working - LED flashes with a 1 sec period.

Downloading MCUXpresso SDK package for MCUXpresso IDE, VS Code or CodeWarrior Development Studio

Select your board.

Build an SDK package for the selected toolchain and download it. Note: Starting with MCUXpresso IDE v11.1.0, you can download and install the MCUXpresso SDK package directly in the tool.

Downloading MCUXpresso SDK CMSIS pack

Alternatively, for the MDK µVision and IAR Embedded Workbench you can download CMSIS packs for the selected processor and board:

Device Family Pack (DFP): NXP.{processor}_DFP.#.#.#.pack

Board Support Pack (BSP): NXP.EVK-{processor}_BSP.#.#.#.pack

Downloading an example project for Keil MDK or IAR Embedded Workbench

For Keil MDK or IAR Embedded Workbench, it is possible to download a single example project. Once you have the SDK build available on MCUXpresso SDK Builder on NXP.com, click the download link and select Download Standalone Example Project. This project contains all sources and project files needed for the build.

Opening example project

MCUXpresso IDE

Drag-and-drop the downloaded MCUXpresso SDK package into the Installed SDKs view to install the package.

Select File > New > Import SDK examples….

Select your processor and board and on the next page select the iled_blinky example.

Keil MDK 5 + Example package

Unpack the SDK package into the selected folder and open boards\evkmimxrt10##\demo_apps\led_blinky\mdk\iled_blinky.uvmpw.

If you have downloaded a single example project only, unzip it into the selected folder and open the workspace file.

Go to Project > Options > Output to ensure the option Create HEX File is selected.

Keil MDK 5 + CMSIS packs

Select Project > Manage > Pack Installer.

In the Devices view, select All Devices > NXP > MIMXRT10##.

In the Packs view, ensure that the following device-specific packs are installed: NXP::{processor}#_DFP and NXP::EVK-{processor}_BSP.

Select the BSP pack

In the Examples view, copy the iled_blinky example project into the selected folder.

Go to Project > Options > Output to ensure the option Create HEX File is selected.

IAR Embedded Workbench + MCUXpresso SDK package

Unpack the SDK package into the selected folder and open boards\evkmimxrt10##\demo_apps\led_blinky\iar\iled_blinky.eww.

If you have downloaded a single example project only, unzip it into the selected folder and open the workspace file.

CodeWarrior Development Studio

Unpack the SDK package into the selected folder and import project in the Commander pane.

If the MCUXpresso Config Tools was used to create a project template, import this project template as described in point 1.

MCUXpresso for Visual Studio Code

Unpack the SDK package into the selected folder.

Use command

> MCUXpresso for VSCode: Import Local/Remote repository; select local and select the path of the SDK folder.Use command

> MCUXpresso for VSCode: Import Example Application from Installed Repository; fill all the items and confirm by clicking the Create button.

Building example project

Detailed information about project configuration and build is in the processor-specific sections below. For a quick evaluation, there are prebuilt application images from SDK examples for NXP evaluation boards provided in the installation layout. For details, refer to the installation subfolder <SEC>sample_data/targets/{processor}/source_images.

Setting up Secure Provisioning Tool

Start Secure Provisioning Tool:

Windows: Double-click the desktop shortcut, or use the Windows Start menu to locate the tool.

MacOS: Click the shortcut in the Dock, or use the Launchpad to locate the tool.

Linux: Click the shortcut in the Launcher, or use the Dash to locate the tool.

Create a new workspace by selecting File > New Workspace … from the menu bar. Select the path to the new workspace. Then select the target processor and click Create.

Connect the device to the host through USB, UART, SPI, or I2C.

Confirm that the connection is working by selecting Target > Connection … from the menu bar and clicking the Test button. Tweak if necessary.

Preparing secure keys

This section describes the generation of asymmetric keys necessary for authenticated or encrypted image creation. This operation is done only once and the keys can be used for all use-cases.

Select the PKI management view.

Ensure it does not already contain keys.

Click Generate keys.

In the Generate keys dialog, confirm the default settings and click Generate.

Note: The generated keys are located in the keys/ subfolder and certificates (if any) in the crts/ subfolder. It is recommended to back up generated keys before they are burned into fuses in the processor.

Build and write

The steps to build and write a bootable image are processor-specific, and will be listed below in the chapter for each processor. In this workflow, it is recommended to write the image prepared on the build; the SEC Tool also supports writing image built externally, but the configuration might require additional configuring and deeper experience.

BCA and FCF pages

This section applies only to processors that contain pages Bootloader Configuration Area (BCA) and Flash Configuration Field (FCF), for example MCXC series.

The BCA and FCF configuration blocks are stored in flash memory and are part of the bootable image. These blocks can be configured using the BCA/FCF configuration dialog through the BCA and FCF pages.

The BCA and FCF pages are not set into the bootable image, and the original content remains unchanged, unless there is any user requirement set to the page. If any requirement is set, the whole page is written, fields that have no user value are set to the default value. In that case, make sure that any value that was set in the source image is not unintentionally overwritten with the default values.

Note: When the life cycle is set to secured flash state, FCF is set into the bootable image even if there are no user requirements.

In the BCA/FCF configuration dialog, the current field values can be read from two sources:

From the flash of the connected processor.

From the source image selected on the Build tab.

i.MX 9x device workflow

This section describes the i.MX 93 and i.MX 95 device workflow in detail.

In the i.MX 9x workflow, the bootable image generated by the SEC Tool is typically the AHAB bootloader image (U‑Boot SPL, U‑Boot, BL31, optional M33/M7 firmware). The resulting flash.bin produced by the SEC Tool represents the signed/unsigned bootloader image.

Preparing images for build for i.MX 9x devices

In this step, select the target memory where the image(s) is to be executed.

i.MX 9x devices have the following cores where image(s) can be executed:

i.MX 93:

Cortex-M33, boot core

Cortex-A55, boot core

i.MX 95:

Cortex-M33, boot core

Cortex-M7

Cortex-A55

The following target memories are supported for i.MX 9x devices:

Image running in RAM

This image can be on an SD card/eMMC/FlexSPI, will be copied into RAM and executed from there during the boot. The following RAM types are supported:

internal RAM

SDRAM (DDR SDRAM)

Several images are required to build the resulting bootable image containing the AHAB container set.

i.MX 93 images:

Primary image container set:

ELE firmware

LPDDR4 firmware files with U-Boot SPL

[Optional] Cortex-M33 application

Secondary image container set:

ARM Trusted Firmware (bl31 binary)

U-Boot

[Optional] TEE binary

i.MX 95 images:

Primary image container set:

ELE firmware

DDR (LPDDR4 or LPDDR5) firmware files with the OEI DDR firmware

CM33 OEI TCM

CM33 System manager

U-Boot SPL

[Optional] Cortex-M7 application

Secondary image container set:

ARM Trusted Firmware (bl31 binary)

U-Boot

TEE binary

For the image with Cortex-M7 and Cortex-M33 application, use the MCUXpresso SDK example. There is no need to modify the default configuration. This image is built to run in internal RAM.

DDR firmware files and ELE firmware can be downloaded from the Yocto Project:

Example of ELE firmware: ELE firmware

Example of DDR firmware files: DDR firmware

For details regarding the latest packages, see i.MX Linux Release Notes document RN00210.

The rest of the images are built from source code. Use the following repos on NXP i.MX main repository

OEI DDR firmware, CM33 OEI TCM: OEI DDR firmware

CM33 System manager: CM33 system manager repository

U-Boot SPL, U-Boot: U-Boot SPL, U-Boot repository, see Build U-Boot with AHAB secure boot features for details.

ARM Trusted Firmware (bl31 binary): ARM trusted firmware

TEE binary: TEE Binary Repository

For additional Linux release materials, see Embedded Linux for i.MX Applications Processors

For example details, see main menu > Help > SPSDK Documentation:

Examples - AHAB - i.MX 95 signed AHAB with U-Boot

Examples - AHAB - i.MX 93 signed and encrypted AHAB image.

Connecting the board for i.MX 9x devices

This section contains information about configuring the evaluation board and connecting it to the SEC Tool:

IMX95LPD5EVK-19 (IMX95LPD5BB-19 base board with IMX95LP5CPU-19 CPU board)

FRDM-IMX95

MCIMX93-EVK (MCIMX93-BB base board with MCIMX93-SOM CPU board)

MCIMX93-QSB

Boot mode/ Device |

Serial bootloader (ISP mode) |

eMMC |

SD card |

FlexSPI NOR |

|---|---|---|---|---|

IMX95LPD5EVK-19 |

SW7: 1001 |

SW7: 1010 |

SW7: 1011 |

SW7: 1100 (N/A) |

FRDM-IMX95 |

SW1: 10 |

SW1: 01 |

SW1: 11 |

N/A |

MCIMX93-EVK |

SW1301: 1101 |

SW1301: 0001 |

SW1301: 0101 |

SW1301: 1011 (N/A) |

MCIMX93-QSB |

SW601: 1001 |

SW601: 1010 |

SW601: 1011 |

SW601: 1100 (N/A) |

Boot mode/ Device |

Serial bootloader (ISP mode) |

eMMC |

SD card |

FlexSPI NOR |

|---|---|---|---|---|

MCIMX93-EVK |

SW1301: 1100 |

SW1301: 0000 |

SW1301: 0100 |

SW1301: 1010 (N/A) |

MCIMX93-QSB |

SW601: 0001 |

SW601: 0010 |

SW601: 0011 |

SW601: 0100 (N/A) |

Step-by-step process:

See Table 7. Boot mode selection for board for i.MX 9x Cortex-M33 core or Table 8. Boot mode selection for board for i.MX 9x Cortex-A55 core for instructions on how to set boot mode using DIP switches.

Connect to the USB1/USB port with the USB cable to your PC for the download link.

Connect to the DBG port with the USB cable to your PC for console output.

Power the board to POWER JACK/USB PD and power on the POWER SWITCH.

Ensure that the SEC Tool is already running with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Open the Connection dialog and test the board connection.

Booting from SD card

For booting from an SD card, do the following:

Insert a micro SDHC card into the board.

Select SD card, SDHC SD-card 64 GB in the Boot Memory Configuration.

Booting from eMMC

For booting from an eMMC, do the following:

Check that the connected board already contains eMMC 64 GB.

Select eMMC: SDHC eMMC 64 GB in the Boot Memory Configuration.

Booting images for i.MX 9x devices

This section describes the building and writing process of bootable images.

i.MX 93 bootable image examples

A container set with the Cortex-M33 application. It is written to on-chip RAM by the nxpuuu utility during write and then started from there.

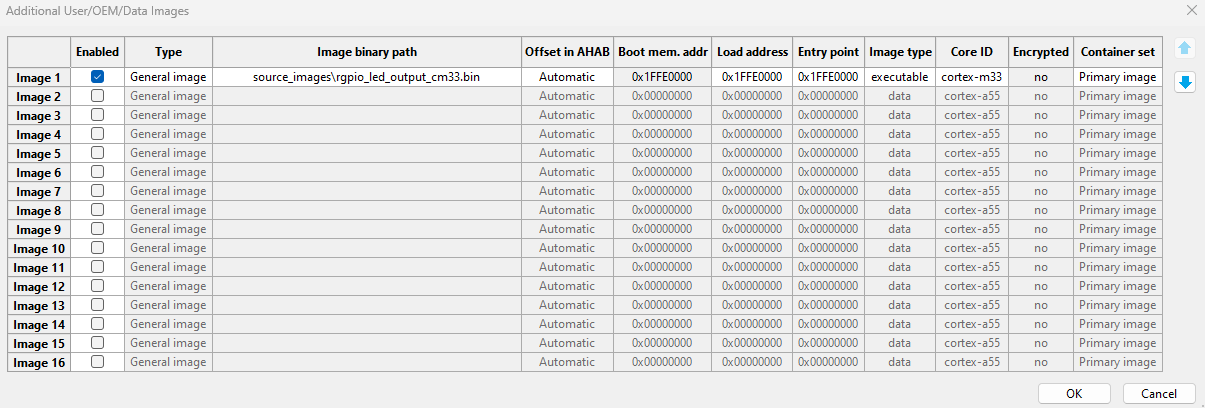

Fig. 50 Bootloader images for Container set with Cortex-M33 application

A container set with Cortex-A55 U-Boot (bootloader). It is written to the eMMC/SD card by the nxpuuu utility during write. During the boot, this bootloader is used to boot the Linux kernel image.

Fig. 51 Bootloader images for Container set with Cortex-A55 U-Boot

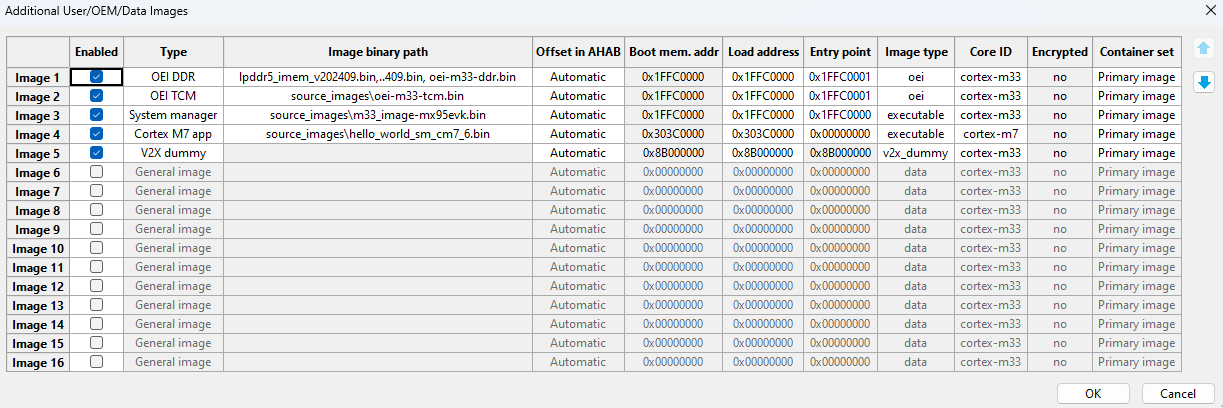

i.MX 95 bootable image examples

A container set with the Cortex-M7 application. It is written to on-chip RAM by the nxpuuu utility during write and then started from there.

Fig. 52 Bootloader images for Container set with Cortex-M7 application

A container set with Cortex-A55 U-Boot (bootloader). It is written to the eMMC/SD card by the nxpuuu utility during write. During the boot, this bootloader is used to boot the Linux kernel image.

Fig. 53 Bootloader images for Container set with Cortex-A55 U-Boot

Booting/loading unsigned image

First, build a bootable image:

Select the Unsigned boot type in the Toolbar.

Select boot device in the Toolbar.

Switch to the Build image

Open the Bootloader images dialog by clicking the Bootloader images button.

Configure the images for the image container, see i.MX 93 bootable image examples or i.MX 95 bootable image examples. Select the prepared images from Preparing images for build for i.MX 9x devices.

Enable the image in the Enabled column.

Select the image entry using Type

Select the binary(s) in the Image binary path.

Select Container set, it should be either Primary image or Secondary image.

All other parameters are preset with default values for the selected image entry type. These parameters can be customized.

Close the dialog by clicking the OK button.

Click the Build image button to build a bootable image,

flash.bin.

When the bootable image has been successfully built:

Make sure that the board is in Serial bootloader (ISP) mode.

Switch to the Write image view.

Click the Write image button.

The nxpuuu utility is used to load the bootable image to the device.

If the write operation was successful:

For eMMC or SD card, switch boot mode (see Table 7. Boot mode selection for board for i.MX 9x Cortex-M33 core or Table 8. Boot mode selection for board for i.MX 9x Cortex-A55 core ) and reset the board. The applications shall run:

hello_worldin Cortex-M7 and/or U-Boot in Cortex-A55.For Serial downloader, the Cortex-M7/Cortex-M33 application runs after it is written.

Booting signed bootloader image from Cortex-M33 or Cortex-A55

This section describes the building and writing of a signed image - either for booting from Cortex‑A55 on i.MX 93 or from Cortex‑M33 on i.MX 95. Keys generated in the PKI management view are needed in this step. For more information about generating keys, see Generate keys.

First, build a bootable image (bootloader for Cortex-A55):

In the Toolbar set Boot type to Signed.

Select boot device in the Toolbar.

Switch to the Build image

Open the Bootloader images dialog and configure the images for the bootloader. See the example for container set with Cortex-A55 U-Boot (bootloader) in i.MX 93 bootable image examples or i.MX 95 bootable image examples and Build U-Boot with AHAB secure boot features.

For Authentication key select any key, for example, SRK1.

Select the OEM Open or OEM Closed life cycle. See chapter Get ELE events with nxpele utility how to verify the application in the OEM Open life cycle.

Click the Build image button.

Check that the bootable image was built successfully.

When the bootable image has been successfully built:

Make sure that the board is in Serial bootloader (ISP) mode.

Switch to the Write image view.

Make sure that the Use built image checkbox is selected. This will write the built bootloader to the selected boot device.

Note: To write another prepared bootable image, another bootloader or a complete image with Linux kernel, unselect the checkbox and select your image. The bootloader built on Build image is still used during write to write fuses and to update the life cycle with the nxpele utility.

Click the Write image button.

The nxpuuu utility is used to load the bootloader, with U-Boot, to RAM.

The nxpele utility is used to write fuses and to update life cycle.

The nxpuuu utility is used to load the bootloader/your prepared bootable image to the boot device.

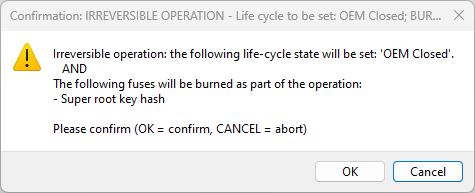

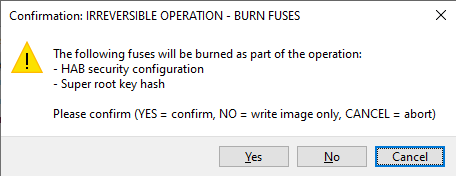

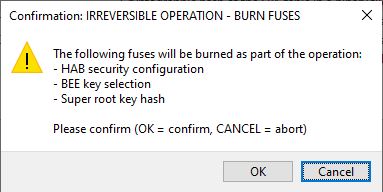

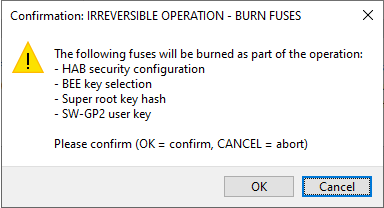

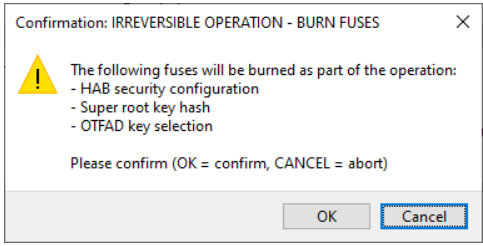

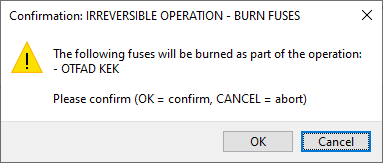

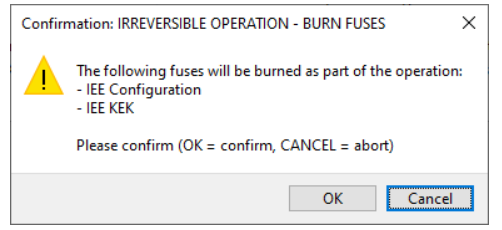

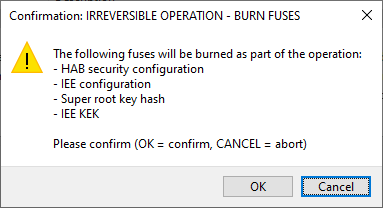

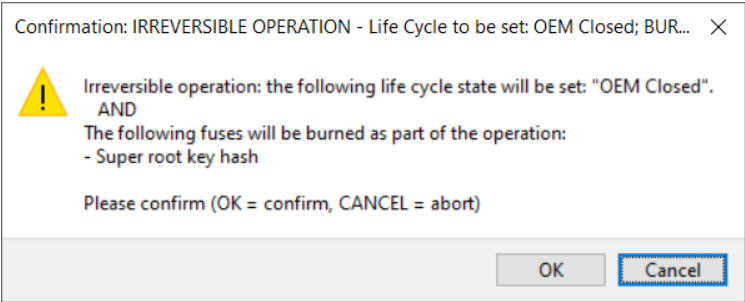

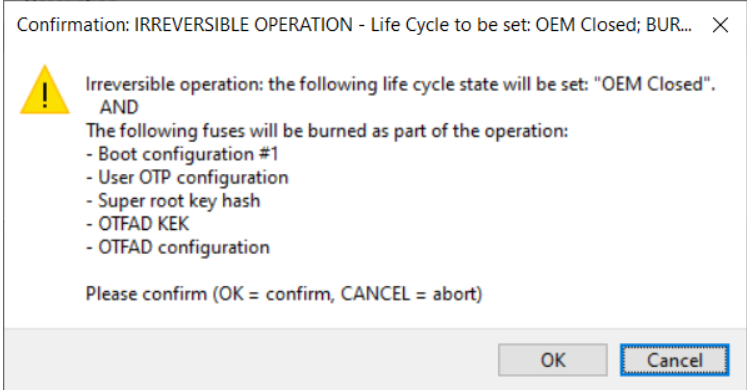

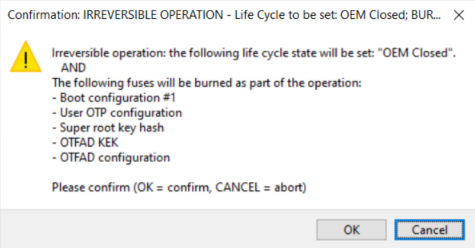

In the following window, confirm to write fuses and update the life cycle:

OK - Continue writing the image and burning fuses.

Cancel - Abort writing the image and burning fuses.

Fig. 54 Burn fuses on i.MX 93

If the write operation was successful, switch the boot mode (see Table 7. Boot mode selection for board for i.MX 9x Cortex-M33 core or Table 8. Boot mode selection for board for i.MX 9x Cortex-A55 core in) and reset the board. The applications shall run U-Boot/your prepared bootable image in Cortex-A55.

Write fuses and update life cycle with nxpele over U-Boot

The nxpele utility is used during provisioning to write fuses or to update life cycle. It is also used to read fuses in the OTP Configuration dialog. The nxpele utility communicates with EdgeLock Enclave over U-Boot, which must be running on the target.

In these cases, the bootable image configured in the Bootloader images dialog is used as a bootloader with the U-Boot. The U-Boot must be built with AHAB features, see Build U-Boot with AHAB secure boot features for details. During the device provisioning, the bootloader is loaded to the target and started.

Life cycle for i.MX 9x devices

In the current tool version, there is a limitation when advancing the life cycle on clean i.MX 9x devices. The life cycle must be advanced in separate steps:

Perform the Booting signed bootloader image from Cortex-M33 or Cortex-A55 while selecting the OEM Open life cycle. During this step, the SRK fuses are programmed.

Keep the board in Serial bootloader (ISP) mode and reset the board.

Select the OEM Closed life cycle and do build and write again. For i.MX 93 devices, the life cycle can be advanced directly to OEM Locked at this step.

For i.MX 95 devices, if the OEM Locked life cycle is needed, keep the board in Serial bootloader (ISP) mode and reset the board. Otherwise, proceed to step 6.

Select the OEM Locked life cycle and do build and write again.

Switch the boot mode (see Table 7. Boot mode selection for board for i.MX 9x Cortex-M33 core or Table 8. Boot mode selection for board for i.MX 9x Cortex-A55 core in) and reset the board. The applications shall run U-Boot/your prepared bootable image in the selected life cycle.

Build U-Boot with AHAB secure boot features

The U-Boot/SPL https://github.com/nxp-imx/uboot-imx provides extra secure boot features. The features enable the nxpele utility to communicate with EdgeLock Enclave. The support is enabled by setting CONFIG_AHAB_BOOT=y in the build.

If the nxpele utility over fastboot is used, multiplexing of the console output to fastboot must be enabled by setting CONFIG_CONSOLE_MUX=y.

Get ELE events with nxpele utility

The nxpele get-event command can retrieve stored events in EdgeLock Enclave. The nxpele utility communicates with ELE over U-Boot, which must be running on the target.

Thanks to this, we can, for example, check the container authentication status in the OEM Open life cycle:

See Booting signed bootloader image from Cortex-M33 or Cortex-A55. In this procedure, keep the life cycle in OEM Open. In the OEM Open life cycle, the authentication result is ignored.

Connect the DBG port to your PC.

Switch to boot mode and reset the board.

Check what serial COM port is the U-Boot console output.

Close the serial connection session if opened in a terminal.

Execute

nxpele get-events

Example when authentication succeeds:

C:\nxp\SEC_Provi_25.09\bin\_internal\tools\spsdk>nxpele -f mimx9352 -p COM21 get-events

ELE get events ends successfully.

Event count: 0

Example when authentication fails:

C:\nxp\SEC_Provi_25.09\bin\_internal\tools\spsdk>nxpele -f mimx9352 -p COM21 get-events

ELE get events ends successfully.

Event count: 2

Event[0]: 0x0287FAD6

IPC ID: Application Processor message unit

Command: OEM Container authenticate

Indication: The key hash verification does not match OTP

Status: The request was successful

Event[1]: 0x0287FAD6

IPC ID: Application Processor message unit

Command: OEM Container authenticate

Indication: The key hash verification does not match OTP

Status: The request was successful

KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx device workflow

This chapter describes workflow for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx processors.

Preparing source image for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx devices

In this step, select the target memory where the image is executed. The following options are available for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx devices:

Image running from an internal flash (XIP image)

There is no need to modify the default configuration, build the MCUXpresso SDK example as it is.

Connecting the board for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx devices

This section contains information about configuring the following evaluation boards and connecting them to SEC Tool:

KW45B41Z-EVK

K32W148-EVK

MCXW71-FRDM

MCXW71-EVK

KW47-EVK

It is assumed that the SEC Tool is already running with a workspace created for an KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx device. For more information, see Setting up Secure Provisioning Tool.

For the KW45B41Z-EVK and K32W148-EVK development boards:

Connect the J14 port to your PC with a USB cable.

Set the JP25 jumper to enable the SW4 button.

Enable the ISP boot mode by holding the SW4 button and reset.

In the Connection dialog, test the connection to the processor.

For the MCXW71-FRDM development board:

Connect the J10 port to your PC with a USB cable.

Enable the ISP boot mode by holding the SW3 button and reset.

In the Connection dialog, test the connection to the processor.

For the MCXW71-EVK development board:

Connect the J14 port to your PC with a USB cable.

Enable the ISP boot mode by holding the SW4 button and reset.

In the Connection dialog, test the connection to the processor.

For the KW47-EVK development board:

Connect the J14 port to your PC with a USB cable.

Enable the ISP boot mode by holding the SW4 button and reset.

In the Connection dialog, test the connection to the processor.

Booting images for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx devices

This section describes the building and writing of bootable images. For KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx, the SEC Tool supports XIP images only.

Booting plain or CRC image

Plain images are typically used for development. Start with this boot type before working with secured images to verify that the executable image works properly. Dual image boot is supported only for secure boot types.

First, build a bootable image:

Make sure that you have selected the Plain unsigned or Plain with CRC boot type is selected in the toolbar.

Switch to the Build image view.

Select an application image built in Building example project as a Source executable image.

If there is a binary image, set the start address to 0x0.

Click the Build image button to build a bootable image. The result is a binary bootable image.

When the bootable image is built, upload it to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

If the write operation was successful, reset the board.

Booting signed image

This section describes building and writing a signed image.

Build a bootable image:

Select the Plain signed boot type in the toolbar.

Switch to the Build image view.

Select an application image built in Building example project as a Source executable image.

Ensure that you have the keys on the PKI management tab. Evaluation boards KW45B41Z-EVK, K32W148-EVK, MCXW71-FRDM, and KW47-EVK are produced with preprogrammed ROKTH and SB3KDK keys in the fuses

CUST_PROD_OEMFW_AUTH_PUKandCUST_PROD_OEMFW_ENC_SK. These keys are also distributed in the SEC Tool and can be imported from the tool foldersample_data\targets\<processor>\board_example_keys. See Import/Export keys. These keys are intended for evaluation purposes only and must not be used for production.For Authentication key select any key, for example ROT1: IMG1_1

Use an imported value or create your own (random) one for SB3KDK symmetric key.

If needed, open Dual image boot and configure. Image must be linked to the Flash Logical Window.

Keep OEM Open in the life cycle.

Click the Build image button to build a bootable image. The result is an SB3 capsule for installation into the processor.

When the bootable image and SB3 capsule have been successfully built, you can upload to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Keep OEM Open in the life cycle.

Make sure that the IFR fields written in otp_config.sb are not burned already. All IFR fields are one time programmable.

Click the Write image button.

Note: If IFR fields are written in the otp_config.sb, it is not possible to receive otp_config.sb multiple times.

Booting PRINCE encrypted image

Encrypted unsigned images, images with CRC or signed images are supported. The process of creating an encrypted image is similar to a signed image. In addition, configure encrypted regions in the Build image view. Use the PRINCE regions button to configure encrypted regions. In combination with the dual boot, set one region for image0 and one for image1. Setting a region only for image0 does not encrypt image1.

Image encryption is performed when the image is written to the target memory.

The regions configuration is included into the ROMCFG page.

Note: Open OTP/IFR configuration to review the PRINCE settings in the ROMCFG block(s) as the block must be specified and can be written only once. It is an irreversible operation.

Life cycle for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx devices

The default life cycle, which should be used for development, is OEM Open. Before you deploy the application, set the OEM Closed or OEM Locked life cycle (see documentation for the target processor for detailed description).

Note: Change of the life cycle is irreversible.

Once the processor is in “OEM Closed” or “OEM Locked” mode, the tool does not allow initializing the ROMCFG page. The application can still be updated via the SB file.

OEM OPEN |

OEM CLOSED/LOCKED |

|

|---|---|---|

Plain unsigned or CRC boot type |

- Only user fuses burnt |

- life cycle fuse burnt |

Plain signed boot type |

- RKTH and SB3KDK burnt in write script |

- RKTH and SB3KDK burnt in write script |

Encrypted boot type |

- RKTH and SB3KDK burnt in write script |

- RKTH and SB3KDK burnt in write script |

Open life cycle, no trust provisioning |

Closed life cycle, no trust provisioning |

Open life cycle, EdgeLock 2GO |

Closed life cycle, EdgeLock 2GO |

|

|---|---|---|---|---|

SB3KDK |

Write script |

Write script |

sb3kdk.asc |

sb3kdk.asc |

RKTH fuses |

Write script |

Write script |

rkth.bin |

rkth.bin |

Other custom fuses and IFR |

Write script or otp_config.sb |

otp_config.sb |

otp_config.sb |

otp_config.sb |

EdgeLock 2GO

EdgeLock 2GO is described in EdgeLock 2GO trust provisioning workflow. Below are KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx specific comments:

The life cycle is set to the life cycle set to the secure objects. The RKTH and SB3KDK fuses are always burned during provisioning, even in the development life cycle.

Address for secure objects must be in internal flash, provisioning firmware erases the area before writing the secure objects.

For KW47 and MCXW72, the OEM_SEC_BOOT_EN fuse is burned by the provisioning firmware if the secure object is set to either “OEM Closed” or “OEM Locked” life cycle.

NXP keys for KW45xx/K32W1xx/MCXW71xx boards

Some EVK and FRDM boards are pre-programmed with NXP keys. Therefore, any signed scenario must use these keys. SEC tools distribute the keys in the following folder: data\sample_data\targets\<processor>\board_example_keys. It is possible to import the keys using the Import keys function in the PKI management tab. Alternatively, you can create a workspace with these keys by selecting a profile that includes board keys in its name, for example: Plain signed image running on on-chip flash — KW45B41Z-EVK keys.

Update NBU firmware

This feature is available only for processors with radio. The NBU firmware is distributed within the MCUXpresso SDK as an SB3 file, as an NXP-signed binary file (*.xip) or as a binary file (*.bin), in folder middleware\wireless\ble_controller\bin.

The NBU firmware can be updated via an SB file. This chapter describes the step-by-step process of:

how to create an SB file using custom keys.

how to use an SB file from the MCUXpresso SDK on the EVK/FRDM boards with NXP keys,

how to create an SB file using custom keys with a custom-signed NBU firmware.

Note: SDK Bluetooth examples for KW47xx boot only once when signed. This issue is caused by the example application, which erases a flash region during execution for future use. However, the erased region contains the signature required for subsequent boots.

Update NBU firmware using custom SB file

Open a workspace for KW45xx/K32W1xx/MCXW71xx/KW47xx/MCXW72xx with the custom keys that were provisioned to the device.

Copy the NBU firmware (xip or bin image from SDK) into the workspace as

source_images\nbu_firmware.xipIn the menu bar, select Tools > SB Editor.

Fill the Properties tab or import a setting from the SB file created on the Build tab.

Switch to the Commands tab.

Select high-level command update-nbu-firmware

Prepare the final SB file by clicking the Generate button.

Click the To Manufacturing tool button to switch to the manufacturing window with the preselected Apply SB file operation and the preselected SB file.

Detect a connected device by clicking the Auto detect button.

Load the SB file by clicking the Start button.

Update NBU firmware using SB file with NXP keys on KW45xx/K32W1xx/MCXW71xx devices

Note: The following steps apply only to boards manufactured with NXP keys. See NXP keys for KW45xx/K32W1xx/MCXW71xx boards.

Create a new workspace with the NXP keys as described in NXP keys for KW45xx/K32W1xx/MCXW71xx boards.

In the menu bar, select Tools > Manufacturing Tool.

Select the Apply SB file operation.

Provide the SB file.

Detect a connected device by clicking the Auto detect button.

Load the SB file by clicking the Start button.

Update signed NBU firmware using custom SB file on KW47xx/MCXW72xx devices

Note: Ensure that the OTP fuse NBU_SEC_BOOT_EN is set to enable verification of the NBU signature during boot.

Open a workspace for KW47xx/MCXW72xx configured with the custom keys provisioned on the device.

Create a copy of

configs/mbi_config.yaml, for exampleconfigs/mbi_config_nbu.yamlIn the new configuration file, modify the following parameters:

Set

inputImageFileto the path of the NBU firmware .bin.Set

masterBootOutputFileto../source_images/nbu_firmware.xipSet

outputImageAuthenticationTypetonbu-signed

Build the signed image by executing:

nxpimage mbi export -c configs\mbi_config_nbu.yamlIn the menu bar, select Tools > SB Editor.

Fill in the Properties tab, or import a setting from the SB file created on the Build tab.

Switch to the Commands tab.

Select high-level command update-nbu-firmware

Generate the final SB file by clicking the Generate button.

Click the To Manufacturing tool button to switch to the manufacturing window with Apply SB file preselected, along with the generated SB file.

Detect a connected device by clicking the Auto detect button.

Load the SB file by clicking the Start button.

LPC55(S)0x/1x/2x/6x device workflow

This chapter describes workflow for LPC55(S)0x/1x/2x/6x, NHS52S04, and MCXW236 processors.

Preparing source image for LPC55(S)0x/1x/2x/6x devices

In this step, you must select the target memory where the image is executed. The following option is available for LPC55Sxx devices:

Image running from an internal flash (XIP image)

Image running from internal flash

MCUXpresso IDE

Build the project.

Open the debug folder.

Right-click the named <your.project>.axf file.

Select Binary Utilities > Create binary.

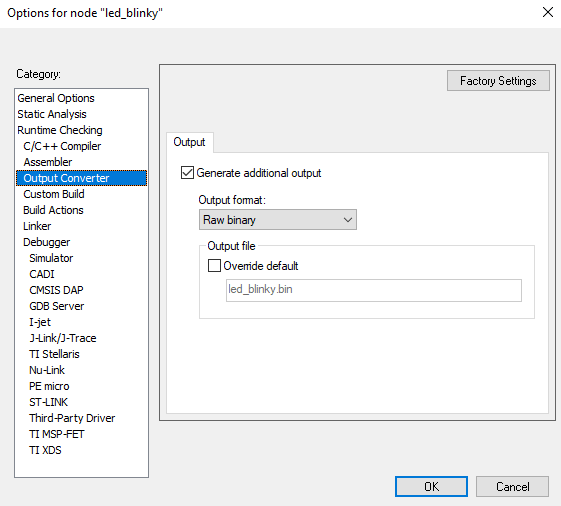

IAR

In Project > Options > Output Converter, check Generate additional output and select Raw binary output format.

Fig. 55 IAR options

Build the project. You find the output image built as

boards\\lpc55s\#\#\\demo\_apps\\led\_blinky\\iar\\led\_blinky\\led\_blinky.bin.

Keil MDK 5

In Project > Options > User > After Build/Rebuild, check the Run #1 option.

Enter the following in the User Command path (where myprog is the project’s Name of Executable):

C:\Keil\ARM\ARMCC\bin\fromelf.exe --bin --output=myprog.bin myprog.axf.Build the image. You find the output image built as

boards\lpc55s\#\#\\demo\_apps\led\_blinky\mdk\led\_blinky\led\_blinky.bin.

Connecting the board for LPC55(S)0x/1x/2x/6x devices

This section contains information about configuring the following LPC5Sxx evaluation boards and connecting them to SEC:

LPCexpresso55S69

LPCexpresso55S66

LPCexpresso55S28

LPCexpresso55S26

LPCexpresso55S16

LPCexpresso55S14

LPCexpresso55S06

LPCexpresso55S04

NHS52Sxx-EVK

FRDM-MCXW236B

It is assumed that the SEC Tool is already running with a workspace created for an LPC device. For more information, see Setting up Secure Provisioning Tool.

To communicate via UART, connect USB cable to P6 connector, for USB communication use P9 connector.

Enable the ISP boot mode by holding the ISP button and reset.

Ensure that you have selected the Unsigned boot type in the Toolbar.

In the Connection dialog, set the connection to USB or UART according to the selected port and test the connection to the processor.

Booting images for LPC55(S)0x/1x/2x/6x devices

This section describes the building and writing of images.

Security levels

The following security levels are supported in SEC:

Unsigned boot types : Default processor configuration that does not provide any security. It is recommended to start with the unsigned boot type to ensure the bootable image works on the processor. Unsigned boot types are intended for development only.

Signed or encrypted boot types - unsealed : Unsealed boot types are also designed to be used during development to ensure the selected boot type works well. In the KeyStore, CFPA, and CMPA pages are written into the processor. CMPA page is not sealed and can be updated or erased.

Signed or encrypted boot types - sealed : A sealed CMPA page is recommended for production. Select the Deployment life cycle in the Write image view to seal the CMPA page. Once sealed, it cannot be changed or erased.

Booting Plain/Plain with CRC image

This section describes the building and writing of plain/plain with CRC image.

In the Toolbar, set Boot Type to Plain unsigned or Plain with CRC.

As a Source executable image, use the image from Preparing source image for LPC55(S)0x/1x/2x/6x devices as a Source executable image.

In the case of a binary image, set the start address to 0x0.

If needed, open Dual image boot and configure.

Click the Build image button.

Check that the bootable image was built successfully.

Once the image has been successfully built, do the following:

Make sure that the board is in ISP mode.

Click the Write image view.

Click the Write image button.

If the write operation was successful, reset the board.

Booting plain signed or PRINCE encrypted image

This section describes the building and writing of an authenticated or PRINCE encrypted image. Keys generated in the PKI management view are needed in this step. For more information about generating keys, see Generate keys.

Note: The keys are also used for Encrypted (PRINCE) Plain and with CRC boot type because the bootable image is updated using SB capsule, which must be signed.

In the Toolbar, set Boot type to Plain signed, Encrypted (PRINCE) unsigned, Encrypted (PRINCE) with CRC, or Encrypted (PRINCE) signed.

In the Build image view, use the image from Preparing source image for LPC55(S)0x/1x/2x/6x devices as a source executable image.

For Authentication key, select any keychain, for example, ROT1: IMG1_1_1.

Open the PRINCE configuration and check the configuration. Set the size of the PRINCE region based on the size of the bootable image.

If needed, open Dual image boot and configure. For a PRINCE encrypted image, set one region for image0 and one for image1. Setting a region only for image0 does not encrypt image1.

Click the Build image button.

Check that the bootable image was built successfully.

To write the image, do the following:

Select the Write image view.

Make sure that the board is connected and the ISP mode is enabled (See Connecting the board for LPC55(S)0x/1x/2x/6x devices )

Click the Write image button.

If the write operation was successful, reset the board.

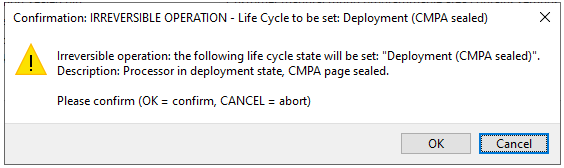

Once the image can be successfully executed in the processor, select the Deployment life cycle to permanently seal the device security with sha256 signature of the CMPA page. If the option remains unselected the security can be reconfigured. After you select the Deployment life cycle, click the Build image button in the Build image view. Then click the Write image button again and confirm the following message box:

Fig. 56 Confirm write

If the write operation was successful, reset the board.

Note: It is necessary to completely erase the entire processor before returning from PRINCE encryption to a non-encrypted image.

PFR and PUF KeyStore

This section provides information about PFR and PUF KeyStore.

PUF KeyStore initialization

SEC initializes KeyStore on LPC55Sxx devices only once in the device life cycle.

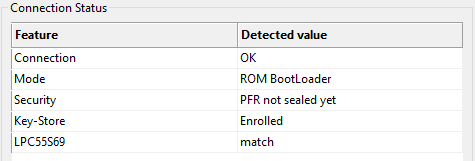

KeyStore enrollment status for the device is reported in the Connection dialog, using the Test button.

Fig. 57 KeyStore connection

It is possible to update the keys in the KeyStore, so it should not be needed to re-initialize KeyStore. In case of unexpected troubles, you can try to erase KeyStore, however, it is not recommended. With the KeyStore, it is recommended to also clear the CFPA page, as PRINCE IV fields in CFPA depend on the KeyStore. The device does not boot if you enroll the KeyStore and try to use it with previous IV fields.

How to erase KeyStore (example for LPC55S69)

bin/tools/blhost/win/blhost -u 0x1FC9,0x0021 -j -- set-property 29 1

bin/tools/blhost/win/blhost -u 0x1FC9,0x0021 -j -- write-memory 0x9E600 zero_1536.bin

zero_1536.bin is a file that contains zeros, and the file size is 3*512 bytes.

How to update CFPA page (example for LPC55S69)

Increment the version in

cfpa.json: it is recommended to add at least 0x10 from the last known version as the version is also incremented during PRINCE IV updates.Run the following commands to update the CFPA page into the processor:

bin/tools/spsdk/pfr generate -c cfpa.json -o cfpa.bin bin/tools/spsdk/blhost -u 0x1FC9,0x0021 -j -- write-memory 0x0009DE00 cfpa.bin

DCFG_CC_SOCU problem on LPC55Sxx

LPC55S0x/1x/2x/6x processors do not support the DCFG_CC_SOCU field configured in CFPA, while DCFG_CC_SOCU in CMPA is zero (not configured yet) and the processor may stop work (lock) if the configuration happens. It is recommended to always configure CMPA first and erase CFPA (+reset) in case erasing of CMPA is needed.

LPC55(S)3x device workflow

Preparing source image for LPC55(S)3x devices

In this step, select the target memory where the image is executed. The following options are available for LPC55(S)3x devices:

Image running from internal FLASH - XIP (eXecution In Place) image, which means that the image is executed directly from the memory where it is located.

It is the default option for almost all SDK examples. There is no need to modify the default configuration, build the example as it is.

Image running from external FLASH - XIP (eXecution In Place) image, which means that the image is executed directly from the memory where it is located.

The image must start at address 0x8001000. The other locations are not supported now. There is no need to modify the default configuration.

For custom external FLASH, the configuration of external FLASH for booting can be adjusted in CMPA.

Connecting the board for LPC55(S)3x devices

This section contains information about configuring the evaluation board LPC55S36-EVK and connecting it to SEC.

Select ISP boot mode, see Table 11. Boot mode selection for LPC55S36 EVK board below.

Connect the J3 port to your PC with a USB cable.

Ensure SEC runs with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Make sure that the boot memory in the toolbar matches NOR FLASH used on EVK board (for example, flex-spi-nor/ISxxxx) or internal flash.

Set the connection to USB and test the board connection.

Board |

In-System Programming (ISP) Boot |

Boot from internal FLASH |

Boot from external FLASH |

|---|---|---|---|

LPC55S36-EVK |

J43: 1-2 open, 3-4 closed |

J43: 1-2 closed, 3-4 closed |

J43: 1-2 closed, 3-4 open |

Booting images for LPC55(S)3x devices

This section describes the building and writing of bootable images. For LPC55S3x, the SEC Tool supports XIP images only.

Booting plain unsigned or CRC image

A plain image is typically used for development. Start with this boot type before working with secured images to verify that the executable image works properly.

First, build a bootable image:

Make sure that you have selected the Plain unsigned or Plain with CRC boot type in the toolbar.

Switch to the Build image view.

Select image built in Preparing source image for LPC55(S)3x devices as a Source executable image.

If there is a binary image, set the start address to 0x0 for internal flash, or 0x8001000 for external flash.

If needed, open Dual image boot and configure.

Click the Build image button to build a bootable image. The result is a binary bootable image.

When the bootable image is built, upload it to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, switch boot mode (see Table 11. Boot mode selection for LPC55S36 EVK board ) and reset the board.

Booting plain signed image

This section describes building and writing a plain signed image.

Build a bootable image:

Select the Plain signed boot type in the toolbar.

Switch to the Build image view.

Select image built in Preparing source image for LPC55(S)3x devices as a Source executable image.

For Authentication key select any key, for example ROT1: IMG1_1

Use random value for “CUST_MK_SK” and “OEM seed” symmetric keys.

If needed, open Dual image boot and configure.

Open the PFR configuration and on the CMPA page check, that the bit-field

SEC_BOOT_ENin theSECURE_BOOT_CFGfield is configured. It is necessary to select any type of image check.Make sure that the board is connected and the processor is in ISP mode. During building processes, provisioning SB file for installation of

CUST_MK_SKinto processor is prepared.Note: The processor is reset after the SB file is built.

Keep Develop in life cycle

Click the Build image button to build a bootable image. The result is a binary bootable image and SB3 capsule for installation of the image into the processor.

When the bootable image has been successfully built, you can upload to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

Booting encrypted image

Encrypted images with CRC or signed images are supported. The process of creation an encrypted image is similar to a signed image. In addition, configure encrypted regions in the Build image view:

Use the PRINCE Regions button to configure encrypted regions for internal FLASH

Use the IPED Regions button to configure encrypted regions for external FLASH

In both cases, the whole image is encrypted by default. For clock limitations when using encrypted images, see documentation for the target processor. With the dual boot, set one region for image0 and one for image1. Setting a region only for image0 does not encrypt image1.

Image encryption is performed when the image is written to the target memory. The encrypted region is configured in the SB file. The decrypted regions are configured in the CMPA page, so make sure these two are aligned.

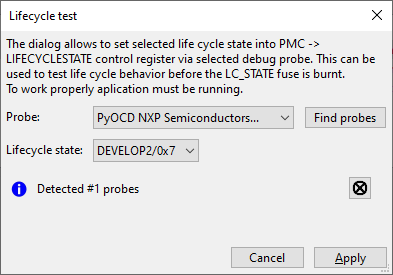

Test life cycle

To test processor behavior in the advanced life cycle, it is possible to temporarily change the life cycle to some higher level by setting control register PMC->LIFECYCLESTATE to the required level. This life-cycle state is valid until HW is reset.

Required steps:

Prepare the image and generate keys.

Set access control in SOCU registers.

Build the image

Execute write operation.

Run the application.

Connect a debug probe.

On the write tab, click the Test life cycle button and in the displayed dialog set the required life cycle state.

Click Apply to move the processor into the selected life cycle. Now, it is possible to test the processor behavior.

Fig. 58 Lifecycle test

Life cycle for LPC55(S)3x devices

The default life cycle, which should be used for development, is Develop. Before you deploy the application, set the “In Field” or “In Field Locked” life cycle (see documentation for the target processor for detailed description).

Note: Change of the life cycle is irreversible.

When changing to In Field life cycle, CMPA and CFPA pages are installed in the dev_hsm_provi.sb file. It is supposed that in this mode, the pages are installed into an empty processor, so there are not any failures (the page update may fail, so in development mode, these pages are updated in write script, where the progress and error report are much better). Once the processor is in In Field state, the SEC Tool supports only update of the application image; updates of CMPA and CFPA are not supported.

LPC865 workflow

This section describes the LPC865 device workflow in detail.

Preparing images for build for LPC865

The processor supports only images executed from internal flash (XIP). Use the default toolchain settings to build the application image.

Connecting the LPCXpresso860-MAX board for LPC865

This section contains information about configuring the evaluation board LPCXpresso860-MAX and connecting it to the SEC Tool.

To power the board, connect the J4 USB port with the USB cable to your power adapter or PC.

Connect pins 2(RX) and 4(TX) at the J2 connector to the UART converter and connect to your PC.

To switch the processor into ISP mode, hold the ISP(SW1) button and press RESET(SW3).

Ensure that the SEC Tool is already running with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Open the Connection dialog and test the board connection. Mind the first board synchronization take a longer time.

Booting images for LPC865

This chapter describes the building and writing of plain bootable image.

Booting unsigned plain image

Plain unsigned is the only boot mode supported by this processor.

First, build a bootable image:

Switch to the Build image view.

Select an image built in Preparing source image for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices as a Source executable image.

If there is a binary image, set the start address to 0x0.

Click the Build image button to build a bootable image. During this operation, the following changes are applied to the image: life cycle (=code read protection) and CRC.

When the bootable image is built, upload it to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, reset the board. The processor will boot after several seconds.

Life cycles

The processor does not support real-life cycles, so the code read protection can be configured instead of life cycle.

MC56F818xx/7xx/6xx and MWCT2xD2/12 devices workflow

This chapter describes workflow for MC56F818xx/7xx/6xx and MWCT2xD2/12 processors.

Preparing source image for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices

In this step, select the target memory where the image is executed. The following options are available for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices:

Image running from an internal flash - XIP (eXecution In Place) image, which means that the image is executed directly from the internal flash memory. There is no need to modify the default configuration, build the MCUXpresso SDK example as it is.

Connecting the board for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices

This section contains information about configuring the evaluation boards and connecting it to SEC:

MC56F81868-EVK

MC56F81000-EVK

WCT-QI2

Power the board from USB_TYPE_C port (WCT-QI2).

Connect the J4 1-TX, 3-RX, 5-GND port (WCT-QI2) via the MCU-Link to your PC.

In the Connection dialog, set the connection to UART

To get to ISP boot mode, send a blhost command to the processor within 5 seconds after the board startup, for example click the Test connection button in the Connection dialog.

Note: The processor boots from internal flash when there is no blhost command sent within 5 seconds after the startup.

Booting images for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices

This chapter describes the building and writing of plain and signed bootable images.

Booting plain unsigned or CRC image

Plain images are typically used for development. Start with this boot type before working with secured images to verify that the executable image works properly.

First, build a bootable image:

Make sure that you have selected the Plain unsigned or Plain with CRC boot type in the toolbar.

Switch to the Build image view.

Select an image built in Preparing source image for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices as a Source executable image.

If there is a binary image, set the start address to 0x0.

If needed, open BCA/FCF configure.

Click the Build image button to build a bootable image. The result is a binary bootable image. For secure processors there are also separated boot headers binary (BCA, FCF) and binary with application. This is due to the DUKB area in the internal flash that must stay untouched during the write.

When the bootable image is built, upload it to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, reset the board. The processor will boot after 5 seconds.

Booting plain signed image

This section describes building and writing a plain signed image.

Build a bootable image:

Select the Plain signed boot type in the toolbar.

Switch to the Build image view.

Select an image built in Preparing source image for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices as a Source executable image.

For Authentication key, select ROT1.

Make sure that the board is connected and the processor is in ISP mode. During building processes, an SBx file is prepared. The processor is used as HSM to create an encrypted SBx file.

Keep OEM Open in the life cycle. See Life cycle and device HSM trust provisioning for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices for OEM Closed life cycle.

Click the Build image button to build a bootable image. The result is a binary bootable image, boot headers binary (BCA, FCF), and SBx capsule for installation of the image into the processor.

When the bootable image has been successfully built, you can upload to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

Life cycle and device HSM trust provisioning for MC56F818xx/7xx/6xx and MWCT2xD2/12 devices

The default life cycle used for development is OEM Open. Before you deploy the application, set the OEM Closed life cycle (see documentation for the target processor for a detailed description).

When the OEM Closed life cycle and Device HSM are set in the toolbar, the trust provisioning SBx file is created during the build. The IFR ISK_CERT_HASH fields are written to IFR by the dev_hsm_provi.sbx file. It is supposed that in this mode, the IFR fields have default values in the processor.

Warning:

Writing of IFR fields is irreversible.

WPC provisioning must be done before advancing the life cycle. Once the board was moved into the advanced life cycle, the provisioning command is not available.

It is possible to reset the life cycle into an OEM Open state if needed. There are two possibilities:

Keep the Plain signed boot type, set the OEM Open life cycle, disable trust provisioning and do build and write. With this, the application is updated and the life cycle is set to OEM Open. Fields in IFR remain unchanged.

Set Plain unsigned boot type, OEM Open life cycle, disable trust provisioning and do build and write. For some devices, it may be necessary to disable flash security before executing the write operation (to enable the FlashEraseAllUnsecure command). With this, the entire flash memory is erased and the life cycle is set to OEM Open. Fields in IFR remain unchanged.

The blhost flash-erase-all command erases the entire memory, which also affects the life cycle state. After flash-erase-all and device reset, the life cycle is in the Closed state.

ISK_CERT_HASH |

SBx file |

|

|---|---|---|

OEM Open lifecycle, Signed boot type |

Included in FCB |

SBx used to write/update the application image |

OEM Closed life cycle, Signed boot type |

Irreversibly written to IFR in trust provisioning SBx file |

SBx used to write/update the application image |

EdgeLock 2GO WPC workflow

The EdgeLock 2GO platform provides provisioning of the Wireless Power Consortium (WPC) Certificate chain needed for WPC Qi authentication. The SEC Tool supports a WPC provisioning scenario where NXP serves as WPC Manufacturing CA Service Provider. For the workflow, it is supposed that the NXP example project is used. Contact NXP sales to get the example.

EdgeLock 2GO WPC flow, step by step

To configure WPC Certificate provisioning, do the following steps:

Turn on secure boot mode and verify that the application works properly.

On the EdgeLock 2GO server, create Qi Manufacturer CAs and Product Unit Certificates

Create an API key. For details, see the API key to access the EdgeLock 2GO server.

In the main menu > Target > Trust Provisioning Mode, check the enable WPC and fill the EdgeLock2GO parameters; use Qi ID for Qi PUC Public Key.

Upload the unsigned ISK block binary

<workspace>/keys/ROT1_cert_block_wpc_signing.binto EdgeLock 2GO server for signing. After signing, download the signed block and save it as<workspace>/keys/isk_nxp_signed.bin.On the write tab, click the Extract WPC certificate button to obtain the manufacturer CA certificate in form of C array

<workspace>/el2go/mfg_ca_cert_array.c. The board must be connected in ISP mode.Use this array to replace WpcMfgCaCert[] in

systemAuthentication.c; certificate is placed in memory at address 0x600-0x7FF. It is expected that the application contains the WPC root CA cert hash at address 0x5E0-0x5FF.Rebuild the project in Codewarrior.

With an updated source file, do the build operation in the SEC Tool.

Write the image into the board. As part of the write operation, the board is provisioned with the WPC PU certificate.

MCX A1/A2/A3/L2 device workflow

This chapter describes workflow for A13x/A14x/A15x/A16x/A17x/A25x/A26x/A34x/A35x/36x/L25x processors.

Preparing source image for MCX A1/A2/A3/L2 devices

Image running from internal FLASH is the default option for almost all SDK examples. There is no need to modify the default configuration, build the example as it is.

Image running from internal RAM; when creating this example, select the link application to RAM. (not supported for MCX L2)

Connecting the board

This section contains information about configuring the boards in the table below connecting to the SEC Tool.

Board |

In-System Programming (ISP) Boot |

Boot from internal FLASH |

|---|---|---|

FRDM-MCXA153 |

SW2/JP8 |

By default |

FRDM-MCXA156 |

SW3 |

By default |

FRDM-MCXA266 |

SW3 |

By default |

FRDM-MCXA344 |

SW2 |

By default |

FRDM-MCXA346 |

SW3 |

By default |

FRDM-MCXA366 |

SW3 |

By default |

FRDM-MCXL255 |

SW3 |

By default |

To connect the board, follow the steps below:

Select ISP boot mode, see the table above.

Connect the UART/USB port to your PC with a USB cable.

Ensure SEC runs with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Go to main menu > Target > Connection, select UART/USB and test the connection.

Booting images MCX A1/A2/A3/L2 devices

Booting plain unsigned and plain with CRC image is the same as for the MCXN devices. For details, see Booting plain or CRC image for MCX N devices.

Setting CMPA flash access control

The CMPA configuration includes flash access control fields labeled FLASH_ACL_#_#. These fields are used to initialize the Memory Block Checker (MBC) configuration registers. The values defined in CMPA are loaded during boot and can be modified later, if they are not locked.

Processors are shipped with an empty flash memory, meaning the CMPA (Customer Manufacturing Programming Area) page is initially invalid. In this default state, the flash is fully accessible—allowing read, write, and execute operations.

Once CMPA is configured on the chip, access permissions must be explicitly defined based on the intended use case. Improperly set access rights may cause the application to malfunction.

By default, the SEC Tool sets access permissions to “read + execute”. However, when configuring the application image, the SEC Tool does not accept this default setting. Instead, it requires the user to explicitly define the access rights, ensuring that the configuration is intentional and verified.

It is important to note that any other memory region that may be accessed during runtime must be configured with the correct access rights. Failure to do so can result in access violations or runtime errors.

Provisioning with device HSM for MCXA25x/MCXA26x/MCXA36x

This section describes building and writing a plain and plain with CRC image provisioned by the device HSM sb file.

Build a bootable image:

Select the desired boot type in the toolbar.

Switch to the Build image view.

Select an image as a Source executable image.

Use a random value for “OEM seed” symmetric keys.

If needed, open Dual image boot and configure.

Ensure that the board is properly connected and the processor is in ISP mode before starting the build process. During the build, a provisioning SB3 file is prepared. The provisioning file contains the CMPA, an executable image, and additional images. If no board is connected, the build fails when preparing the provisioning SB3 file.

Click the Build Image button to generate a bootable image. This process creates a device HSM SB3 capsule for installation of the image into the processor.

Note: In any advanced ROP state, CMPA is configured to remove the Secure Installer (SI), since SI is not supported in the advanced life cycle.

When the bootable image is successfully built, upload it to the processor:

Make sure that the processor is in ISP mode.

Switch to the Write image view.

Click the Write image button.

Life cycle for MCX A1/A2/A3/L2 devices

The default life cycle that should be used for development is OEM Open. Before you deploy the application, set the “In Field ROP 1”, “In Field ROP 2”, or “In Field ROP 3” life cycle (see the documentation for the target processor for a detailed description). For devices that have CMPA in the internal flash, it is possible to revert the life cycle by executing a mass erase command.

Note: In Field ROP 3, the life cycle cannot be reverted, ISP commands are not available.

Reverting life cycle

To revert the life cycle, execute the mass erase command.

For devices with Secure Installer (SI), the SI firmware must be removed first, otherwise the mass erase command fails. This is because the memory region containing the SI is protected and cannot be accessed. Once the SI is erased and the ERASE_TOKEN[x] registers are set in the CMPA, flash protection is disabled. Note: The mass erase operation also erases the CMPA and the erase token registers. Therefore, save the erase token value before executing the mass erase, so it can be restored afterward to regain access to the flash region where the SI was located.

Erasing SI in development

The tool does not natively support erasing the SI during the development lifecycle, but it can be done manually by following these steps:

Prepare a CMPA configuration that sets the DELETE_INSTALLER register to 0x4027FF65 and the ERASE_TOKEN[x] registers to 0xFFFFFFFF.

Write this CMPA into the device and restart it.

After the reset, read the CMPA from the device and set Current values to the Required values for ERASE_TOKEN[x] registers. This value is device‑specific and must be used only with this particular device. Using it on another device together with the DELETE_INSTALLER register will brick the device and make it unrecoverable.

The internal flash region previously allocated for the SI is now free and can be used freely.

MCUboot for MCX A1/A2/A3/L2 devices

MCUboot is described in MCUboot workflow. Below are MCX-specific comments:

The flash access field settings in CMPA, where MCUboot is managing the application, must be set to any “unlocked” rule. An unlocked rule must be set because MCUboot modifies the region rule by setting it to a “write” rule during the application updates and to an “execute” rule when running the application.

MCX A2/A4/A5 devices workflow

This chapter describes workflow for A28x/A45x/A53x/A55x/A56x/A57x processors.

Preparing source image for MCX A2/A4/A5 devices

Image running from internal FLASH is the default option for almost all SDK examples. There is no need to modify the default configuration; build the example as provided.

Image running from internal RAM: when creating this type of example, select the option to link the application to RAM.

Booting images MCX A2/A4/A5 devices

Booting plain unsigned and plain with CRC image is the same as for the MCXN devices. For details, see Booting plain or CRC image for MCX N devices.

Extended PFR regions

The processor supports extended CFPA and CMPA regions. In the SEC Tool, the content of these regions can be specified in binary format in the Required files table on Build page. By default, these regions are empty.

Import ext. CMPA binary by selecting

Extended CMPAinRequired filestable. The SEC Tool validates its size and sets the EXT_CMPA_32B_SIZE field in the CMPA page.Import ext. CFPA binary by selecting

Extended CFPAinRequired filestable. The SEC Tool validates its size; the conditionext_cfpa_size <= ext_pfr_region_size - ext_cmpa_sizemust be satisfied.The extended CFPA and extended CMPA binaries are included in the

unpdate_cfpa_cmpa.yamlconfiguration file. After build, the resultingupdate_cfpa_cmpa.binincludes all four pages.

In the PFR configuration dialog, when writing the CFPA page, the extended CFPA page is also written if it is specified. The extended CFPA is written at an offset that is calculated based on the value of the EXT_CMPA_32B_SIZE field in the CMPA page.

In the PFR configuration dialog, when writing the CMPA page, the CFPA page and, if specified, the extended CMPA and extended CFPA pages are also written. These PFR pages must always be written together due to the PFR page update flow in ROM. For more information, see the processor reference manual.

Setting CFPA flash access control

The CFPA configuration includes flash access control fields labeled FLASH_ACL_#_#. These fields are used to initialize the Memory Block Checker (MBC) configuration registers. The values defined in CFPA are loaded during boot and can be modified later, if they are not locked.

Once CFPA is configured on the chip, access permissions must be explicitly defined based on the intended use case. Improperly set access rights may cause the application to malfunction.

By default, the SEC Tool sets access permissions to “read + execute”. However, when configuring the application image, the SEC Tool does not accept this default setting. Instead, it requires the user to explicitly define the access rights, ensuring that the configuration is intentional and verified.

It is important to note that any other memory region that may be accessed during runtime must be configured with the correct access rights. Failure to do so can result in access violations or runtime errors.

Life cycle for MCX A2/A4/A5 devices

The default life cycle that should be used for development is Develop. Before you deploy the application, set the In Field or In Field Locked life cycle (see documentation for the target processor for a detailed description).

Note: Change of the life cycle is irreversible.

MCX C041/C242/C444 device workflow

This chapter describes the workflow for Cx4x processors.

Preparing source image for MCX C041/C242/C444 devices

An image running from the internal FLASH is the default option for almost all SDK examples. There is no need to modify the default configuration, build the example as it is.

An image runs from internal RAM when this example is created. Select the link application to RAM. The option is not supported on MCXC041.

Connecting the board for MCX C041/C242/C444 devices

This section contains information about configuring the evaluation boards FRDM-MCXC041, FRDM-MCXC242, FRDM-MCXC444, and connecting them to SEC.

Board |

In-System Programming (ISP) Boot |

Boot from internal FLASH |

|---|---|---|

FRDM-MCXC041 |

SW3 |

By default |

FRDM-MCXC242 |

SW3 |

By default |

FRDM-MCXC444 |

SW3 |

By default |

Select ISP boot mode. For details, see the table above.

Connect the UART/USB port to your PC with a USB cable.

Ensure SEC runs with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Go to main menu > Target > Connection, select UART and test the connection.

Booting images for MCX C041/C242/C444 devices

This section describes building and writing of bootable images into the internal flash and booting.

Booting plain unsigned image

First, build a bootable image:

Switch to the Build image view.

Select an image built in Preparing source image for LPC55(S)0x/1x/2x/6x devices as a Source executable image.

If there is a binary image, set the start address to 0x00000000.

If needed, open BCA/FCF configure.

To build a bootable image, click the Build image button. The result is a binary bootable image.

When the bootable image is built, upload it to the processor:

Make sure that the processor is in the ISP mode.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, reset the board to boot the image.

Life cycle for MCX C041/C242/C444 devices

The default life cycle that should be used for development is Flash unsecured. Before deploying the application, set the Flash secured (see documentation for the target processor for a detailed description). When switching the life cycle, the best practice is to set BCA and FCF pages. Chip with the flash security enabled can be erased, if ISP is available and the FCF field ‘mass erase’ is enabled.

Life cycle is configured in the FCF page, in the field FSEC.SEC; for Flash secured, the SEC Tool applies value 0b11 (which is functionally the same as 0b00 or 0b01).

Backdoor key

The advanced life cycle can be temporarily disabled if the backdoor key was set and the backdoor key comparison is enabled in FCF. After the backdoor key verification, the processor behaves as if in the OEM Open life cycle until the next reset. If the verification fails, further verification is not possible until flash reset. Flash security can be disabled using the ‘Disable Flash Security’ dialog available under the Write tab.

MCX E24 device workflow

This chapter describes the workflow for MCX E24x processors.

Preparing source image for MCX E24x devices

An image running from the internal flash is the default option for almost all SDK examples. There is no need to modify the default configuration, build the example as it is.

Internal flash is the only supported boot memory for MCX E24x devices.

Connecting the board for MCX E24x devices

This section contains information about configuring the evaluation board FRDM-MCXE247 and connecting it to SEC.

Flashloader boot behavior on MCX E24x devices

MCX E24x devices do not support ISP boot mode. Instead, they are factory-preprogrammed with a flashloader image stored in the internal flash that includes both the flashloader loader and the flashloader firmware.

By default, these devices boot from internal flash memory. During the boot process, the preprogrammed flashloader is automatically loaded into RAM and executed from there. This enables flash programming functionality without requiring a separate ISP mode.

Flashloader initialization via debug probe

If the flashloader is not running on the device, it can be loaded and executed from RAM using a debug probe. The onboard MCU-Link on the FRDM-MCXE247 supports debug probe functionality and can therefore be used for this purpose.

Note: Flashloader can be initialized via MCU-Link or J-Link debug probe.

Note: SEC Tool scripts that use the debug probe host software (LinkServer or JLink) expect the host software’s installation directory to be included in the PATH environment variable.

Select the debug probe either in main menu > Target > Debug Probe or in the Toolbar, Dbg.

FRDM-MCXE247 UART pin connections

To establish communication between the preprogrammed flashloader (which uses LPUART1) and the onboard MCU-Link (which uses LPUART2), connect the MikroBUS UART to the Arduino UART using two Dupont wires as follows:

Connect Arduino J1 - Pin 2 (PTD17/LPUART2_RX-Arduino_D0) to MikroBUS J5 - Pin 3 (PTC8/LPUART1_RX-MIKROE)

Connect Arduino J1 - Pin 4 (PTE12/LPUART2_TX-Arduino_D1) to MikroBUS J5 - Pin 4 (PTC9/LPUART1_TX-MIKROE)

With this connection, the onboard MCU-Link’s USB-to-UART bridge functionality can be used to enable communication between the host PC and the flashloader via UART.

FRDM-MCXE247 connection via SPI

To establish the SPI communication between the preprogrammed flashloader and an external USB-to-SPI bridge (for example, MCU-Link Pro Debug Probe), connect the bridge to the target board as follows:

SPI MOSI to MicroBUS J6 - Pin 5 (PTB3/LPSPI0_SIN-MIKROE)

SPI SCK to Arduino J3 - Pin 1 (PTB2/FTM1_QD_PHB-MC_ENC_B)

SPI MISO to IO Expander J8 - Pin 12 (PTB1)

SPI PCS0 to IO Expander J8 - Pin 9 (PTB0)

With this connection, the external USB-to-SPI bridge can be used to enable communication between the host PC and the flashloader via SPI.

Connecting the board to host PC

Connect the J13 (MCU-Link USB) port to your PC with a USB cable.

Ensure SEC runs with a workspace created for the chosen device. For more information, see Setting up Secure Provisioning Tool.

Go to main menu > Target > Connection, select UART and test the connection.

Note: When the Test Connection button is clicked, the flashloader is initialized via a debug probe if it is not already running. In this case, a debug probe must be selected, see Flashloader initialization via debug probe.

Booting images for MCX E24x devices

This section describes building and writing of bootable images into the internal flash and booting.

Booting plain unsigned image - unsecure boot

This section describes image building and writing for unsecure boot.

First, build a bootable image:

Make sure that you have selected the Unsigned boot type in the toolbar.

Switch to the Build image view.

Select an image built in Preparing source image for MCX E24x devices as a Source executable image.

If there is a binary image, set the start address to 0x00000000.

If needed, open FCF configuration and configure.

If needed, open SHE keys configuration and configure, see SHE keys configuration.

To build a bootable image, click the Build image button. The result is a binary bootable image.

When the bootable image is built, upload it to the processor:

Make sure that the processor is connected.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, reset the board to boot the image.

Booting plain signed image - secure boot

This section describes how to build and write a bootable image for secure boot. During secure boot, the bootable image code section is authenticated, and the generated MAC is compared with a value previously stored in the secure key storage (BOOT_MAC).

First, build a bootable image:

Make sure that you have selected the Authenticated (SHE) serial or Authenticated (SHE) parallel or Authenticated (SHE) strict boot type in the toolbar. For more information about secure boot types, see the boot type tooltip.

Switch to the Build image view.

Select an image built in Preparing source image for MCX E24x devices as a Source executable image.

If there is a binary image, set the start address to 0x00000000.

If needed, open FCF configuration and configure.

Open SHE keys configuration and configure, see SHE keys configuration.

Make sure BOOT_MAC_KEY is configured to enable secure boot.

For details on BOOT_MAC, see Manual and automatic BOOT_MAC calculation.

To build a bootable image, click the Build image button.

This generates a binary bootable image.

If enabled, BOOT_MAC is calculated.

Binaries for loading SHE keys are also created.

When the bootable image is built, upload it to the processor:

Make sure that the processor is connected.

Switch to the Write image view.

Click the Write image button.

If the write operation is successful, reset the board to boot the image.

Note: The Authenticated (SHE) strict boot mode is permanent once set and cannot be changed. Additionally, automatic BOOT_MAC calculation is not supported in this mode. Before setting this boot mode, BOOT_MAC must be calculated and stored. Failure to do so will cause the device to remain in the RESET state and prevent it from booting.

SHE keys configuration