# MCUXpresso SDK Documentation Release 25.09.00

NXP Sep 19, 2025

## **Table of contents**

| 1   | LPC  | Xpresso860MAX 3                                      |  |  |  |  |

|-----|------|------------------------------------------------------|--|--|--|--|

|     | 1.1  | Overview                                             |  |  |  |  |

|     | 1.2  | Getting Started with MCUXpresso SDK Package          |  |  |  |  |

|     |      | 1.2.1 Getting Started with MCUXpresso SDK Package    |  |  |  |  |

|     | 1.3  | Getting Started with MCUXpresso SDK GitHub           |  |  |  |  |

|     |      | 1.3.1 Getting Started with MCUXpresso SDK Repository |  |  |  |  |

|     | 1.4  | Release Notes                                        |  |  |  |  |

|     |      | 1.4.1 MCUXpresso SDK Release Notes                   |  |  |  |  |

|     | 1.5  | ChangeLog                                            |  |  |  |  |

|     |      | 1.5.1 MCUXpresso SDK Changelog                       |  |  |  |  |

|     | 1.6  | Driver API Reference Manual                          |  |  |  |  |

|     | 1.7  | Middleware Documentation                             |  |  |  |  |

|     |      | 1.7.1 FreeMASTER                                     |  |  |  |  |

|     |      | 1.7.2 FreeRTOS                                       |  |  |  |  |

|     |      |                                                      |  |  |  |  |

| 2   |      | LPC865 107                                           |  |  |  |  |

|     | 2.1  | Clock Driver                                         |  |  |  |  |

| 2.2 |      | CRC: Cyclic Redundancy Check Driver                  |  |  |  |  |

|     | 2.3  | CTIMER: Standard counter/timers                      |  |  |  |  |

|     | 2.4  | DMA: Direct Memory Access Controller Driver          |  |  |  |  |

|     | 2.5  | FTM: FlexTimer Driver                                |  |  |  |  |

|     | 2.6  | I2C: Inter-Integrated Circuit Driver                 |  |  |  |  |

|     | 2.7  | I2C Driver                                           |  |  |  |  |

|     | 2.8  | I2C Master Driver                                    |  |  |  |  |

|     | 2.9  | I2C Slave Driver                                     |  |  |  |  |

|     |      | I3C: I3C Driver         190                          |  |  |  |  |

|     |      | I3C Common Driver         192                        |  |  |  |  |

|     |      | I3C Master DMA Driver                                |  |  |  |  |

|     |      | I3C Master Driver         198                        |  |  |  |  |

|     |      | I3C Slave DMA Driver                                 |  |  |  |  |

|     |      | I3C Slave Driver         226                         |  |  |  |  |

|     |      | IAP: In Application Programming Driver 239           |  |  |  |  |

|     |      | INPUTMUX: Input Multiplexing Driver                  |  |  |  |  |

|     |      | Common Driver                                        |  |  |  |  |

|     |      | LPC_ACOMP: Analog comparator Driver                  |  |  |  |  |

|     |      | ADC: 12-bit SAR Analog-to-Digital Converter Driver   |  |  |  |  |

|     |      | GPIO: General Purpose I/O                            |  |  |  |  |

|     |      | IOCON: I/O pin configuration                         |  |  |  |  |

|     |      | MRT: Multi-Rate Timer                                |  |  |  |  |

|     |      | PINT: Pin Interrupt and Pattern Match Driver         |  |  |  |  |

|     |      | Power                                                |  |  |  |  |

|     |      | Reset                                                |  |  |  |  |

|     |      | SCTimer: SCTimer/PWM (SCT)                           |  |  |  |  |

|     |      | SPI: Serial Peripheral Interface Driver              |  |  |  |  |

|     |      | SPI Driver                                           |  |  |  |  |

|     | 2.30 | SWM: Switch Matrix Module                            |  |  |  |  |

|   | 2.31 | SYSCO        | N: System Configuration                              |

|---|------|--------------|------------------------------------------------------|

|   | 2.32 | <b>USART</b> | : Universal Asynchronous Receiver/Transmitter Driver |

|   | 2.33 | <b>USART</b> | Driver                                               |

|   |      |              | Self-wake-up Timer                                   |

|   |      |              | : Windowed Watchdog Timer Driver                     |

|   |      |              |                                                      |

| 3 |      | dlewar       |                                                      |

|   | 3.1  | Motor        | Control                                              |

|   |      | 3.1.1        | FreeMASTER                                           |

| 4 | RTO  | S            | 395                                                  |

|   | 4.1  | _            | OS                                                   |

|   | 1.1  | 411          | FreeRTOS kernel                                      |

|   |      | 4.1.2        | FreeRTOS drivers                                     |

|   |      | 4.1.3        | backoffalgorithm                                     |

|   |      | 4.1.4        | corehttp                                             |

|   |      | 4.1.5        | corejson                                             |

|   |      | 4.1.6        | coremgtt                                             |

|   |      | 4.1.7        | •                                                    |

|   |      | 4.1.7        | coremqtt-agent                                       |

|   |      |              | corepkcs11                                           |

|   |      | 4.1.9        | freertos-plus-tcp                                    |

This documentation contains information specific to the lpcxpresso  $860 \, \mathrm{max}$  board.

Table of contents 1

Table of contents

### **Chapter 1**

## LPCXpresso860MAX

#### 1.1 Overview

The LPC86x are an Arm Cortex-M0+ based, low-cost 32-bit MCU family operating at CPU frequencies of up to 48 MHz. The LPC86x support up to 64 KB of flash memory and 8 KB of SRAM.

The peripheral complement of the LPC86x includes a CRC engine, one I2C-bus interface, one I3C-MIPI bus interface, up to three USARTs, up to two SPI interfaces, one multi-rate timer, self-wake-up timer, two FlexTimers, a DMA, one 12-bit ADC, one analog comparator, function-configurable I/O ports through a switch matrix, an input pattern match engine, and up to 54 general-purpose I/O pins.

MCU device and part on board is shown below:

• Device: LPC865

• PartNumber: LPC865M201JBD64

#### 1.2 Getting Started with MCUXpresso SDK Package

#### 1.2.1 Getting Started with MCUXpresso SDK Package

#### Overview

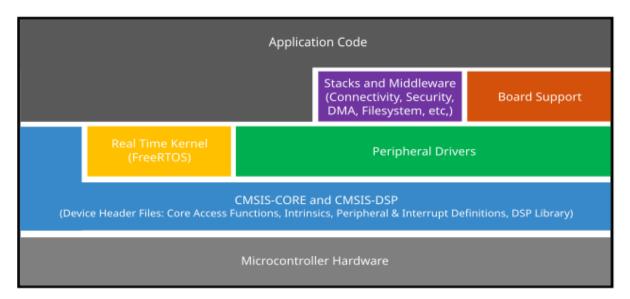

The NXP MCUXpresso software and tools offer comprehensive development solutions designed to optimize, ease, and help accelerate embedded system development of applications based on general purpose, crossover, and Bluetooth-enabled MCUs from NXP. The MCUXpresso SDK includes a flexible set of peripheral drivers designed to speed up and simplify development of embedded applications. Along with the peripheral drivers, the MCUXpresso SDK provides an extensive and rich set of example applications covering everything from basic peripheral use case examples to full demo applications. The MCUXpresso SDK contains optional RTOS integrations such as FreeRTOS and Azure RTOS, and various other middleware to support rapid development.

For supported toolchain versions, see *MCUXpresso SDK Release Notes* (document MCUXSDKRN). For more details about MCUXpresso SDK, see MCUXpresso Software Development Kit (SDK).

#### MCUXpresso SDK board support package folders

MCUXpresso SDK board support package provides example applications for NXP development and evaluation boards for Arm Cortex-M cores including Freedom, Tower System, and LPCX-presso boards. Board support packages are found inside the top-level boards folder and each supported board has its own folder (an MCUXpresso SDK package can support multiple boards). Within each <br/>

<br/>board\_name> folder, there are various subfolders to classify the type of examples it contains. These include (but are not limited to):

- cmsis driver examples: Simple applications intended to show how to use CMSIS drivers.

- demo\_apps: Full-featured applications that highlight key functionality and use cases of the target MCU. These applications typically use multiple MCU peripherals and may leverage stacks and middleware.

- driver\_examples: Simple applications that show how to use the MCUXpresso SDK's peripheral drivers for a single use case. These applications typically only use a single peripheral but there are cases where multiple peripherals are used (for example, SPI conversion using DMA).

- emwin examples: Applications that use the emWin GUI widgets.

- rtos\_examples: Basic FreeRTOS OS examples that show the use of various RTOS objects (semaphores, queues, and so on) and interfaces with the MCUXpresso SDK's RTOS drivers

- usb examples: Applications that use the USB host/device/OTG stack.

**Example application structure** This section describes how the various types of example applications interact with the other components in the MCUXpresso SDK. To get a comprehensive understanding of all MCUXpresso SDK components and folder structure, see *MCUXpresso SDK API Reference Manual*.

Each <board\_name> folder in the boards directory contains a comprehensive set of examples that are relevant to that specific piece of hardware. Although we use the hello\_world example (part of the demo\_apps folder), the same general rules apply to any type of example in the <board\_name> folder.

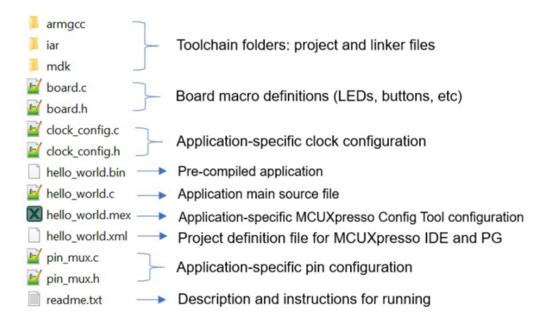

In the hello world application folder you see the following contents:

All files in the application folder are specific to that example, so it is easy to copy and paste an existing example to start developing a custom application based on a project provided in the MCUXpresso SDK.

**Locating example application source files** When opening an example application in any of the supported IDEs, various source files are referenced. The MCUXpresso SDK devices folder is the central component to all example applications. It means that the examples reference the same source files and, if one of these files is modified, it could potentially impact the behavior of other examples.

The main areas of the MCUXpresso SDK tree used in all example applications are:

- devices/<device\_name>: The device's CMSIS header file, MCUXpresso SDK feature file, and a few other files

- devices/<device\_name>/cmsis\_drivers: All the CMSIS drivers for your specific MCU

- devices/<device name>/drivers: All of the peripheral drivers for your specific MCU

- devices/<device\_name>/<tool\_name>: Toolchain-specific startup code, including vector table definitions

- $\bullet$   $\rm devices/< device\_name>/utilities:$  Items such as the debug console that are used by many of the example applications

- devices/<devices name>/project: Project template used in CMSIS PACK new project creation

For examples containing middleware/stacks or an RTOS, there are references to the appropriate source code. Middleware source files are located in the  $\operatorname{middleware}$  folder and RTOSes are in the  $\operatorname{rtos}$  folder. The core files of each of these are shared, so modifying one could have potential impacts on other projects that depend on that file.

#### Run a demo using MCUXpresso IDE

**Note:** Ensure that the MCUXpresso IDE toolchain is included when generating the MCUXpresso SDK package.

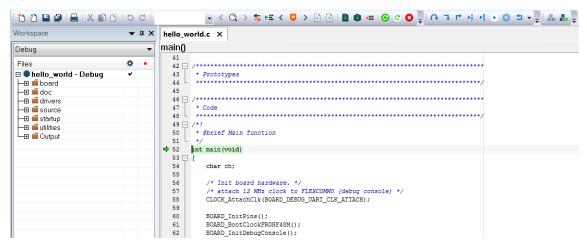

This section describes the steps required to configure MCUXpresso IDE to build, run, and debug example applications. The hello world demo application targeted for the hardware platform is

used as an example, though these steps can be applied to any example application in the MCUX-presso SDK.

**Select the workspace location** Every time MCUXpresso IDE launches, it prompts the user to select a workspace location. MCUXpresso IDE is built on top of Eclipse which uses workspace to store information about its current configuration, and in some use cases, source files for the projects are in the workspace. The location of the workspace can be anywhere, but it is recommended that the workspace be located outside the MCUXpresso SDK tree.

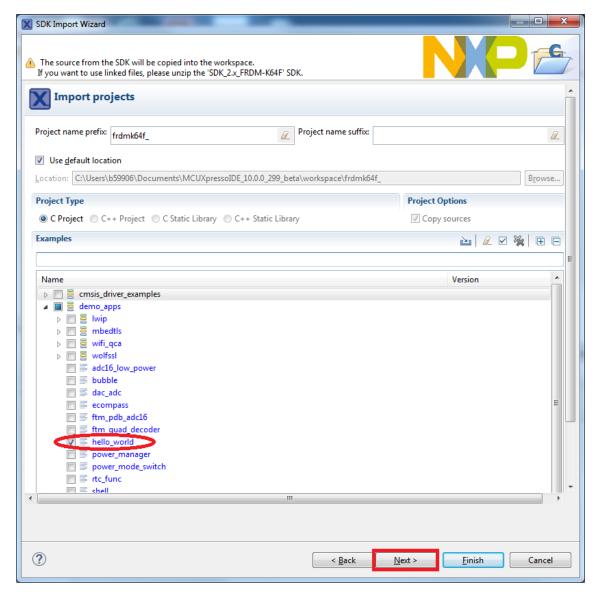

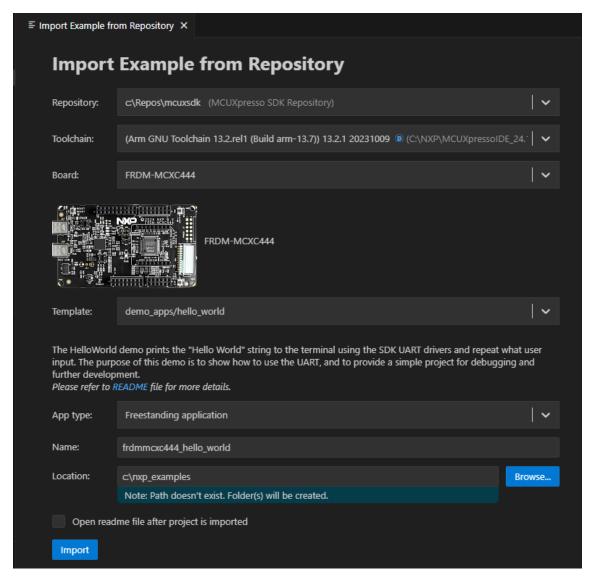

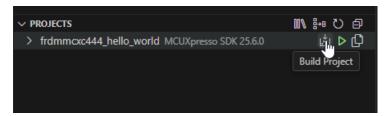

**Build an example application** To build an example application, follow these steps.

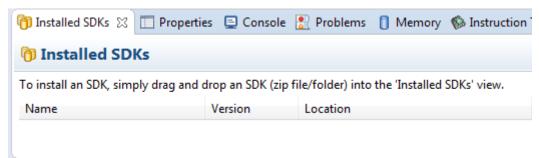

1. Drag and drop the SDK zip file into the **Installed SDKs** view to install an SDK. In the window that appears, click **OK** and wait until the import has finished.

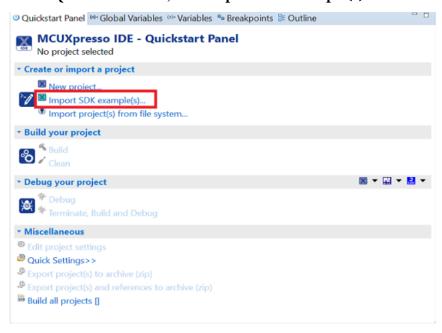

2. On the Quickstart Panel, click Import SDK example(s)....

- 3. Expand the demo\_apps folder and select hello\_world.

- 4. Click Next.

5. Ensure **Redlib:** Use floating-point version of printf is selected if the example prints floating-point numbers on the terminalfor demo applications such as adc\_basic, adc\_burst, adc\_dma, and adc\_interrupt. Otherwise, it is not necessary to select this option. Then, click **Finish**.

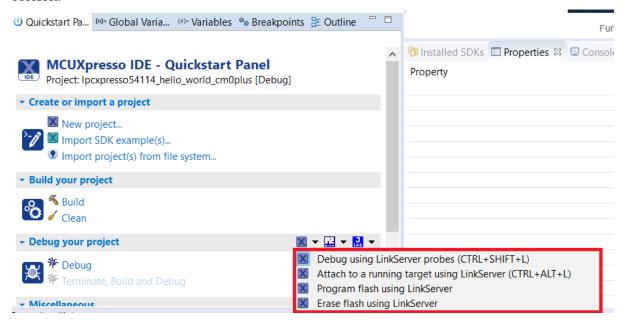

**Run an example application** For more information on debug probe support in the MCUX-presso IDE, see community.nxp.com.

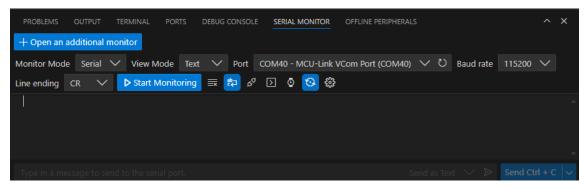

To download and run the application, perform the following steps:

- 1. Ensure the host driver for the debugger firmware has been installed. See *On-board debugger*.

- 2. Connect the development platform to your PC via a USB cable.

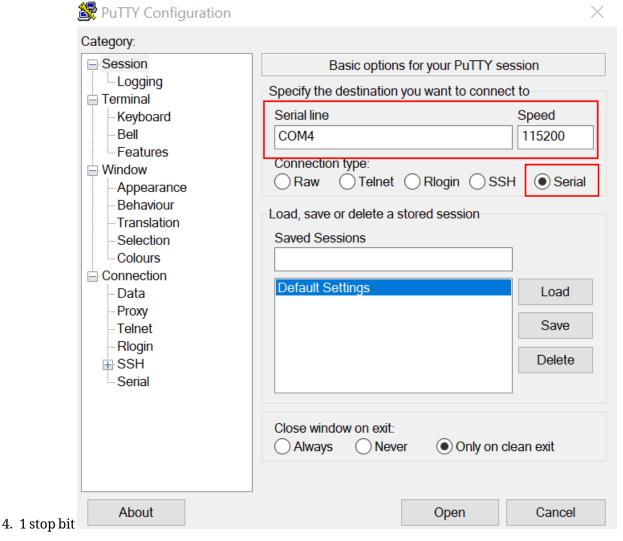

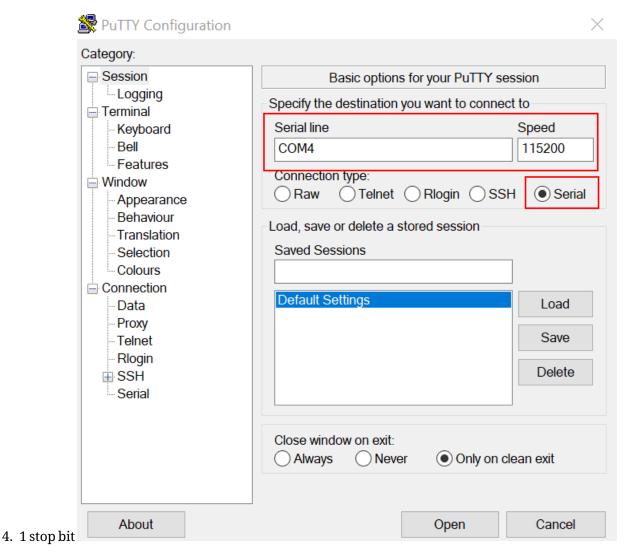

- 3. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug serial port number (to determine the COM port number, see *How to determine COM port*. Configure the terminal with these settings:

- 1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in board.h file)

- 2. No parity

#### 3. 8 data bits

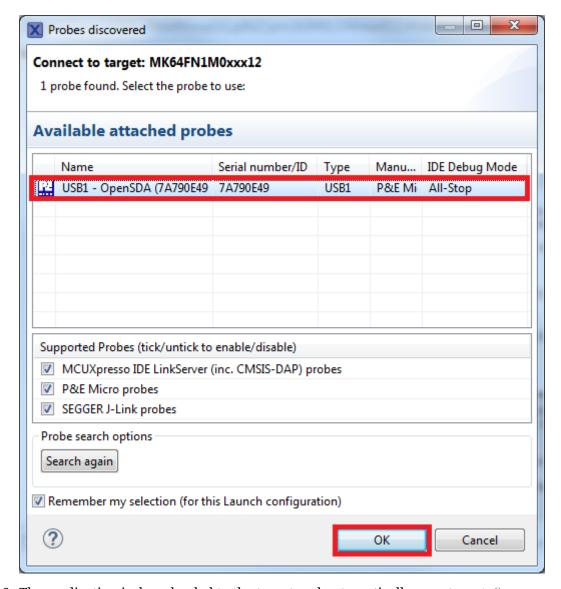

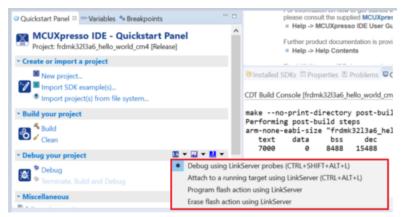

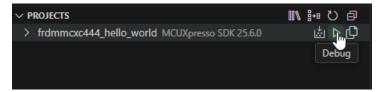

- 4. On the **Quickstart Panel**, click **Debug** to launch the debug session.

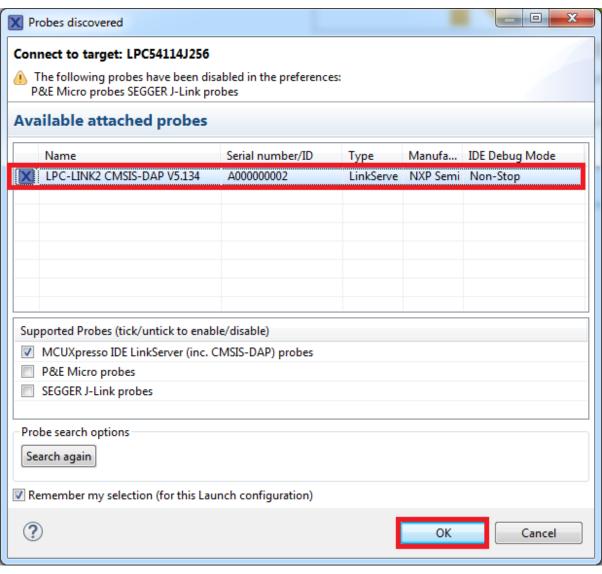

- 5. The first time you debug a project, the **Debug Emulator Selection** dialog is displayed, showing all supported probes that are attached to your computer. Select the probe through which you want to debug and click **OK**. (For any future debug sessions, the stored probe selection is automatically used, unless the probe cannot be found.)

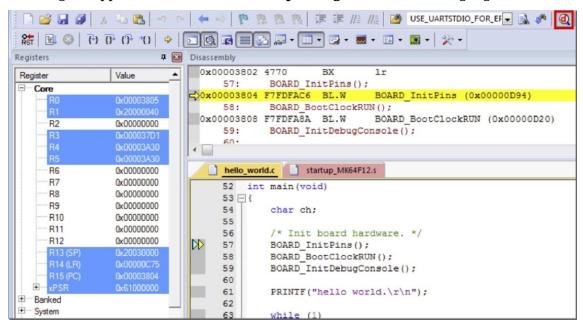

- 6. The application is downloaded to the target and automatically runs to main().

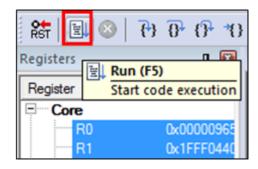

- 7. Start the application by clicking **Resume**.

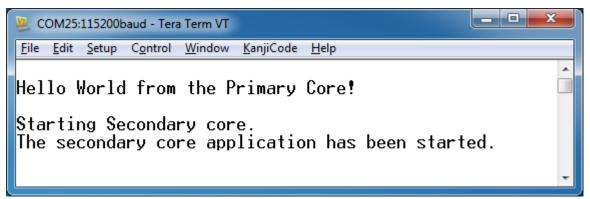

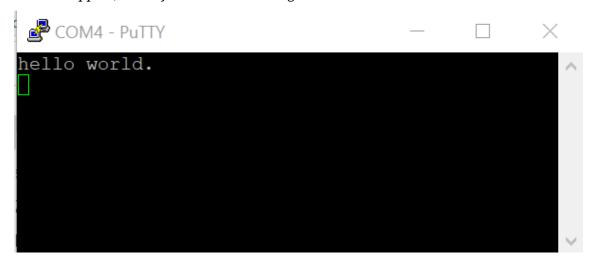

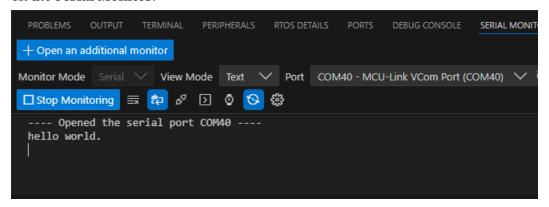

The hello\_world application is now running and a banner is displayed on the terminal. If not, check your terminal settings and connections.

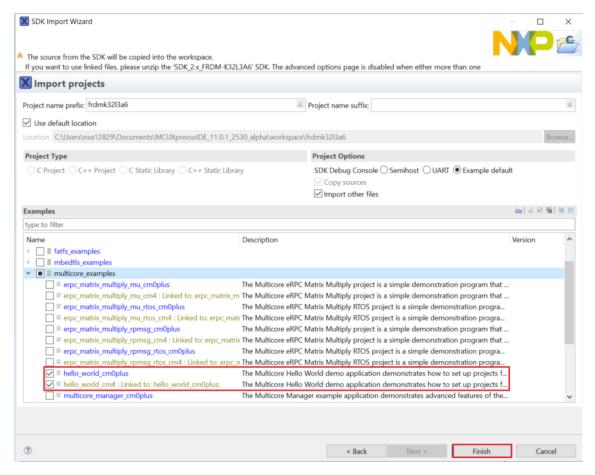

**Build a multicore example application** This section describes the steps required to configure MCUXpresso IDE to build, run, and debug multicore example applications. The following steps can be applied to any multicore example application in the MCUXpresso SDK. Here, the dual-core version of hello\_world example application targeted for the LPCXpresso54114 hardware platform is used as an example.

- 1. Multicore examples are imported into the workspace in a similar way as single core applications, explained in **Build an example application**. When the SDK zip package for LPCXpresso54114 is installed and available in the **Installed SDKs** view, click **Import SDK example(s)...** on the Quickstart Panel. In the window that appears, expand the **LPCxx** folder and select **LPC54114J256**. Then, select **lpcxpresso54114** and click **Next**.

- 2. Expand the multicore\_examples/hello\_world folder and select **cm4**. The cm0plus counterpart project is automatically imported with the cm4 project, because the multicore examples are linked together and there is no need to select it explicitly. Click **Finish**.

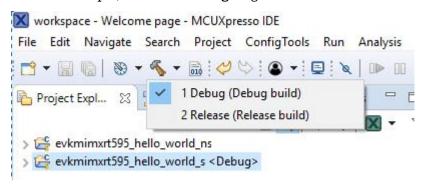

3. Now, two projects should be imported into the workspace. To start building the multicore application, highlight the <code>lpcxpresso54114\_multicore\_examples\_hello\_world\_cm4</code> project (multicore master project) in the Project Explorer. Then choose the appropriate build target, **Debug** or **Release**, by clicking the downward facing arrow next to the hammer icon, as shown in the figure. For this example, select **Debug**.

The project starts building after the build target is selected. Because of the project reference settings in multicore projects, triggering the build of the primary core application (cm4) also causes the referenced auxiliary core application (cm0plus) to build.

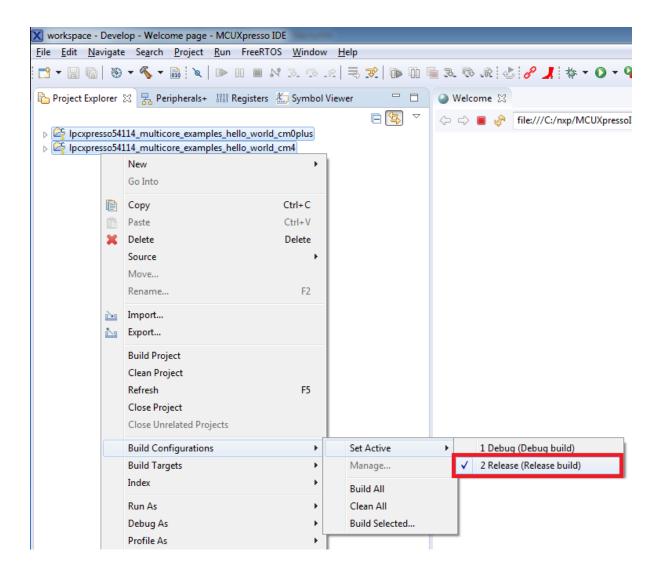

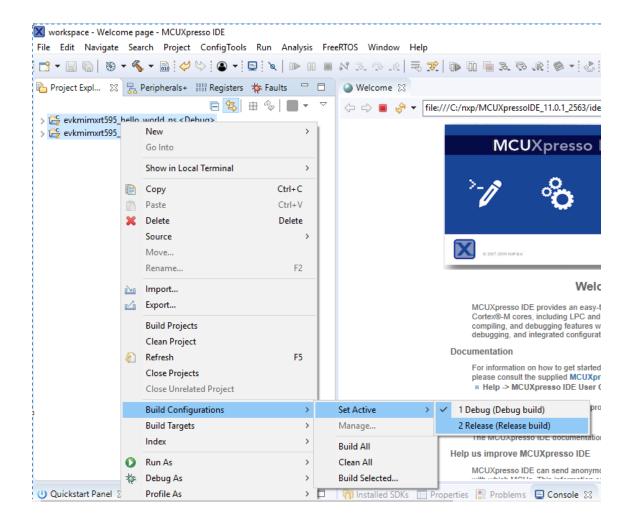

**Note:** When the **Release** build is requested, it is necessary to change the build configuration of both the primary and auxiliary core application projects first. To do this, select both projects in the Project Explorer view and then right click which displays the context-sensitive menu. Select **Build Configurations** -> **Set Active** -> **Release**. This alternate navigation using the menu item is **Project** -> **Build Configuration** -> **Set Active** -> **Release**. After switching to the **Release** build configuration, the build of the multicore example can be started by triggering the primary core application (cm4) build.

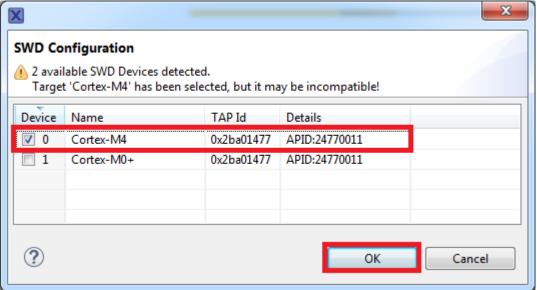

Run a multicore example application The primary core debugger handles flashing of both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform all steps as described in Run an example application. These steps are common for both single-core applications and the primary side of dual-core applications, ensuring both sides of the multicore application are properly loaded and started. However, there is one additional dialogue that is specific to multicore examples which requires selecting the target core. See the following figures as reference.

```

🗶 workspace - Develop - lpcxpresso54114_multicore_examples_hello_world_cm4/source/hello_world_core0.c - MCUXpresso IDE

File Edit Source Refactor Navigate Search Project Run FreeRTOS Window Help

🏇 Debug 🏻

■ Ipcxpresso54114_multicore_examples_hello_world_cm4 Debug [C/C++ (NXP Semiconductors) MCU Application]

8

■ ipcxpresso54114_multicore_examples_hello_world_cm4.axf [LPC54114J256 (cortex-m0plus)]

묾

■ Thread #11 (Stopped) (Suspended: Breakpoint)

1010

0101

main() at hello_world_core0.c:85 0x98a

*

arm-none-eabi-gdb (7.12.0.20161204)

8

ic hello_world_core0.c ⋈

(1)

68 {

(x)=

69

uint32_t core1_image_size;

(x)=

70 #if defined(__CC_ARM)

0

core1_image_size = (uint32_t)&Image$$CORE1_REGION$$Length;

71

72 #elif defined(__ICCARM__)

믊

_sec_core"

73

#pragma section = "

core1_image_size = (uint32_t)__section_end("__sec_core") - (uint32_t)&core1_image_start;

74

75

#endif

76

return core1_image_size;

77 }

78 #endif

80 * @brief Main function

81 */

820 int main(void)

83 {

/* Define the init structure for the switches*/

gpio_pin_config_t sw_config = {kGPIO_DigitalInput, 0};

86

87

/* Init board hardware.*/

88

/* attach 12 MHz clock to FLEXCOMM0 (debug console) */

89

CLOCK AttachClk(kFR012M to FLEXCOMM0);

90

91

BOARD InitPins Core0();

BOARD BootClockFROHF48M();

92

93

BOARD_InitDebugConsole();

94

95

/* Init switches */

GPIO_PinInit(BOARD_SW1_GPIO, BOARD_SW1_GPIO_PORT, BOARD_SW1_GPIO_PIN, &sw_config);

96

97

GPIO_PinInit(BOARD_SW2_GPIO, BOARD_SW2_GPIO_PORT, BOARD_SW2_GPIO_PIN, &sw_config);

```

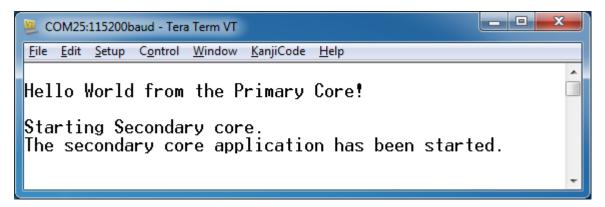

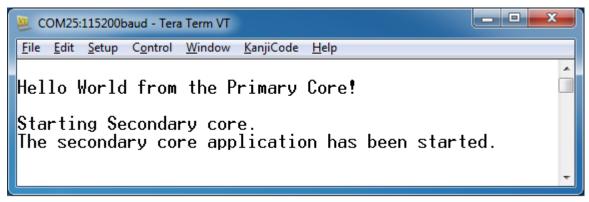

After clicking the "Resume All Debug sessions" button, the hello\_world multicore application runs and a banner is displayed on the terminal. If this is not the case, check your terminal settings and connections.

An LED controlled by the auxiliary core starts flashing, indicating that the auxiliary core has been released from the reset and running correctly. It is also possible to debug both sides of the multicore application in parallel. After creating the debug session for the primary core, perform same steps also for the auxiliary core application. Highlight the lpcxpresso54114\_multicore\_examples\_hello\_world\_cm0plus project (multicore slave project) in the Project Explorer. On the Quickstart Panel, click "Debug 1pcxpresso54114\_multicore\_examples\_hello\_world\_cm0plus' [Debug]" to launch the second debug

#### session.

```

📈 workspace - Develop - Ipcxpresso54114_multicore_examples_hello_world_cm4/source/hello_world_core0.c - MCUXpresso IDE

<u>File Edit Source Refactor Navigate Search Project Run FreeRTOS Window Help</u>

🏇 Debug 🏻

■ Ipcxpresso54114_multicore_examples_hello_world_cm4 Debug [C/C++ (NXP Semiconductors) MCU Application]

6

■ ipcxpresso54114_multicore_examples_hello_world_cm4.axf [LPC54114J256 (cortex-m0plus)]

묾

Thread #1 1 (Stopped) (Suspended : Breakpoint)

1010

0101

main() at hello world core0.c:85 0x98a

*

arm-none-eabi-gdb (7.12.0.20161204)

■ Ipcxpresso54114_multicore_examples_hello_world_cm0plus Debug [C/C++ (NXP Semiconductors) MCU Application]

■ Propresso54114_multicore_examples_hello_world_cm0plus.axf [LPC54114J256 (cortex-m0plus)]

8

Thread #1 1 (Stopped) (Suspended: Signal: SIGSTOP:Stopped (signal))

ψ

0x1ec

(x)=

<signal handler called>() at 0xfffffff9

(x)=

0x0

0

arm-none-eabi-gdb (7.12.0.20161204)

먎

🖟 hello_world_core0.c 🏻

68

uint32_t core1_image_size;

#if defined(__CC_ARM)

70

core1_image_size = (uint32_t)&Image$$CORE1_REGION$$Length;

71

#elif defined(_ICCARM_)

#pragma section = "__sec_core"

72

73

74

core1_image_size = (uint32_t)__section_end("__sec_core") - (uint32_t)&core1_image_start;

75

76

return core1_image_size;

77

78

#endif

79⊕ /*!

* @brief Main function

81

82@ int main(void)

83

{

/* Define the init structure for the switches*/

gpio_pin_config_t sw_config = {kGPIO_DigitalInput, 0};

86

87

/* Init board hardware.*/

/* attach 12 MHz clock to FLEXCOMM0 (debug console) */

88

CLOCK_AttachClk(kFR012M_to_FLEXCOMM0);

90

BOARD_InitPins_Core0();

91

BOARD_BootClockFROHF48M();

92

93

BOARD_InitDebugConsole();

95

/* Init switches */

GPIO PinInit(BOARD SW1 GPIO, BOARD SW1 GPIO PORT, BOARD SW1 GPIO PIN, &sw config);

96

GPIO_PinInit(BOARD_SW2_GPIO, BOARD_SW2_GPIO_PORT, BOARD_SW2_GPIO_PIN, &sw_config);

97

```

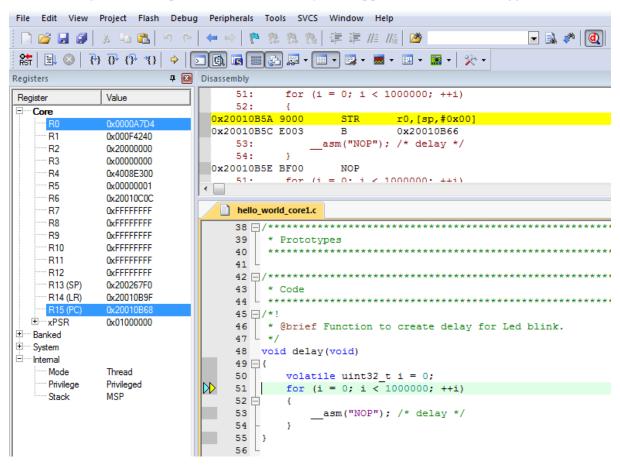

Now, the two debug sessions should be opened, and the debug controls can be used for both debug sessions depending on the debug session selection. Keep the primary core debug session selected by clicking the "Resume" button. The hello\_world multicore application then starts running. The primary core application starts the auxiliary core application during runtime, and the auxiliary core application stops at the beginning of the main() function. The debug session of the auxiliary core application is highlighted. After clicking the "Resume" button, it is applied to the auxiliary core debug session. Therefore, the auxiliary core application continues its execution.

```

📈 workspace - Develop - Ipcxpresso54114_multicore_examples_hello_world_cm0plus/source/hello_world_core1.c - MCUXpresso IDE

File Edit Source Refactor Navigate Search Project Run FreeRTOS Window Help

▼ 🗗 ▼ 🕡 ▼ 🐉 🕻 📞 🐉 🛷 🎉 🗿 🗊 🐗 🖟 🖟 🖟 🖟 🖟 🔝 🖜 ▼ 🏈 🖟 🔞 😭 🔐 😭

Step Return All Debug sessions

★ Debug

□

▲ X Ipcxpresso54114_multicore_examples_hello_world_cm4 Debug [C/C++ (NXP Semiconductors) MCU Application]

6

Ipcxpresso54114_multicore_examples_hello_world_cm4.axf [LPC54114J256 (cortex-m0plus)]

굶

Thread #11 (Stopped) (Running)

1010

0101

arm-none-eabi-gdb (7.12.0.20161204)

*

■ Ipcxpresso54114_multicore_examples_hello_world_cm0plus Debug [C/C++ (NXP Semiconductors) MCU Application]

■ Ipcxpresso54114_multicore_examples_hello_world_cm0plus.axf [LPC54114J256 (cortex-m0plus)]

8

main() at hello_world_core1.c:71 0x20010846

ψ

arm-none-eabi-gdb (7.12.0.20161204)

(x)=

(x)=

00

믊

nello_world_core1.c ⊠

hello_world_core0.c

.h fsl_mailbox.h

}

61 }

62

63⊖ /*!

64 * @brief Main function

65 */

65

66⊖ int main(void)

67 {

uint32_t startupData, i;

68

69

/* Define the init structure for the output LED pin*/

70

gpio_pin_config_t led_config = {

71

72

kGPIO DigitalOutput, 0,

73

74

75

/* Initialize MCMGR before calling its API */

76

MCMGR_Init();

77

/* Get the startup data */

78

MCMGR_GetStartupData(kMCMGR_Core1, &startupData);

79

80

81

/* Make a noticable delay after the reset */

/* Use startup parameter from the master core... */

82

83

for (i = 0; i < startupData; i++)</pre>

84

delay();

```

At this point, it is possible to suspend and resume individual cores independently. It is also possible to make synchronous suspension and resumption of both the cores. This is done either by selecting both opened debug sessions (multiple selections) and clicking the "Suspend" / "Resume" control button, or just using the "Suspend All Debug sessions" and the "Resume All Debug sessions" buttons.

```

💢 workspace - Develop - lpcxpresso54114_multicore_examples_hello_world_cm0plus/source/hello_world_core1.c - MCUXpresso IDE

<u>File Edit Source Refactor Navigate Search Project Run FreeRTOS Window Help</u>

- N R P R F F M P E R P M T F F N P F F N P

■ Ipcxpresso54114_multicore_examples_hello_world_cm4 Debug [C/C++ (NXP Semiconductors) MCU Application]

8

Ipcxpresso54114_multicore_examples_hello_world_cm4.axf [LPC54114J256 (cortex-m0plus)]

몲

Thread #1 1 (Stopped) (Running)

1010

0101

arm-none-eabi-gdb (7.12.0.20161204)

*

■ Ipcxpresso54114_multicore_examples_hello_world_cm0plus Debug [C/C++ (NXP Semiconductors) MCU Application]

Ipcxpresso54114_multicore_examples_hello_world_cm0plus.axf [LPC54114J256 (cortex-m0plus)]

Thread #1 1 (Stopped) (Running)

æ

arm-none-eabi-gdb (7.12.0.20161204)

ம

(x)=

(x)=

0

믊

.c hello_world_core0.c

h fsl_mailbox.h c hello_world_core1.c ⋈ c 0x190

asm("NOP"); /* delay */

60

61 }

62

63⊕ /*!

64 * @brief Main function

65 */

66⊖ int main(void)

67 {

68

uint32_t startupData, i;

69

/* Define the <u>init</u> structure for the output LED pin*/

70

71

gpio_pin_config_t led_config = {

72

kGPIO_DigitalOutput, 0,

73

74

/* Initialize MCMGR before calling its API */

75

76

MCMGR_Init();

77

78

/* Get the startup data */

79

MCMGR_GetStartupData(kMCMGR_Core1, &startupData);

80

81

/* Make a noticable delay after the reset */

/* Use startup parameter from the master core... */

82

83

for (i = 0; i < startupData; i++)</pre>

84

delay();

```

```

📈 workspace - Develop - Ipcxpresso54114_multicore_examples_hello_world_cm0plus/source/hello_world_core1.c - MCUXpresso IDE

<u>F</u>ile <u>E</u>dit <u>S</u>ource Refactor <u>N</u>avigate Search <u>P</u>roject <u>R</u>un FreeRTOS <u>W</u>indow <u>H</u>elp

8

■ Ipcxpresso54114_multicore_examples_hello_world_cm4 Debug [C/C++ (NXP Semiconductors) MCU Application]

6

■ ipcxpresso54114_multicore_examples_hello_world_cm4.axf [LPC54114J256 (cortex-m0plus)]

몲

Thread #1 1 (Stopped) (Suspended: Signal: SIGINT:Interrupt)

1010

0101

GPIO_ReadPinInput() at fsl_gpio.h:146 0x95c

*

main() at hello_world_core0.c:134 0xa10

arm-none-eabi-gdb (7.12.0.20161204)

Ð

■ MI lpcxpresso54114_multicore_examples_hello_world_cm0plus Debug [C/C++ (NXP Semiconductors) MCU Application]

■ Ipcxpresso54114_multicore_examples_hello_world_cm0plus.axf [LPC54114J256 (cortex-m0plus)]

ψ

Thread #1 1 (Stopped) (Suspended : Signal : SIGINT:Interrupt)

(x)=

delay() at hello_world_core1.c:59 0x20010824

(x)=

main() at hello_world_core1.c:99 0x200108a0

0

arm-none-eabi-gdb (7.12.0.20161204)

믊

hello_world_core0.c

h fsl_mailbox.h

le hello_world_core1.c ⋈ le 0x190

59

asm("NOP"); /* delay */

60

61 }

62

63@ /*!

* @brief Main function

660 int main(void)

67 {

68

uint32_t startupData, i;

70

/* Define the init structure for the output LED pin*/

gpio_pin_config_t led_config = {

71

72

kGPIO_DigitalOutput, 0,

73

74

75

/* Initialize MCMGR before calling its API */

76

MCMGR_Init();

77

78

/* Get the startup data */

79

MCMGR_GetStartupData(kMCMGR_Core1, &startupData);

80

/* Make a noticable delay after the reset */

81

82

/* Use startup parameter from the master core... */

83

for (i = 0; i < startupData; i++)

delay();

```

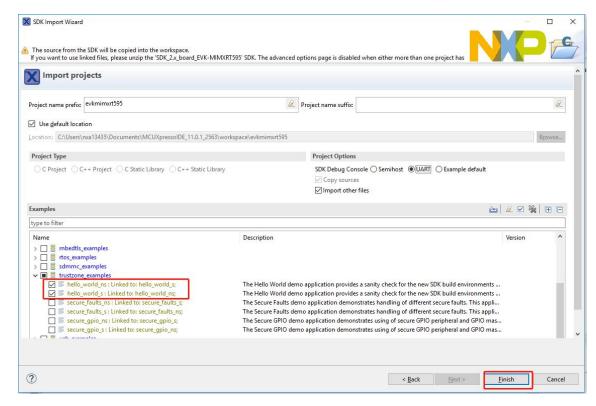

**Build a TrustZone example application** This section describes the steps required to configure MCUXpresso IDE to build, run, and debug TrustZone example applications. The TrustZone version of the hello\_world example application targeted for the MIMXRT595-EVK hardware platform is used as an example, though these steps can be applied to any TrustZone example application in the MCUXpresso SDK.

- 1. TrustZone examples are imported into the workspace in a similar way as single core applications. When the SDK zip package for MIMXRT595-EVK is installed and available in the Installed SDKs view, click Import SDK example(s)... on the Quickstart Panel. In the window that appears, expand the MIMXRT500 folder and select MIMXRT595S. Then, select evkmimxrt595 and click Next.

- 2. Expand the trustzone\_examples/ folder and select hello\_world\_s. Because TrustZone examples are linked together, the non-secure project is automatically imported with the secure project, and there is no need to select it explicitly. Then, click **Finish**.

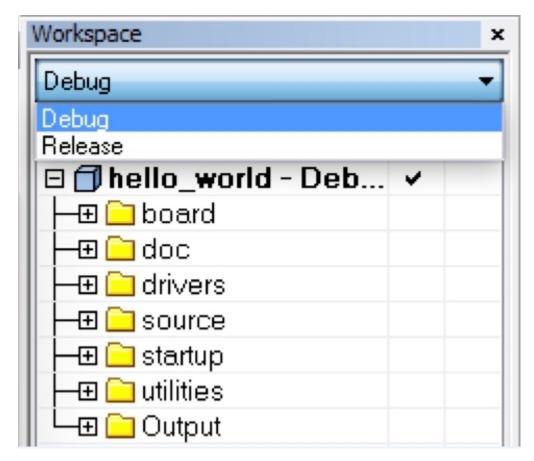

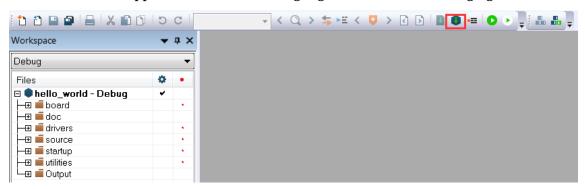

3. Now, two projects should be imported into the workspace. To start building the TrustZone application, highlight the <code>evkmimxrt595\_hello\_world\_s</code> project (TrustZone master project) in the Project Explorer. Then, choose the appropriate build target, **Debug** or **Release**, by clicking the downward facing arrow next to the hammer icon, as shown in following figure. For this example, select the **Debug** target.

The project starts building after the build target is selected. It is requested to build the application for the secure project first, because the non-secure project must know the secure project since CMSE library when running the linker. It is not possible to finish the non-secure project linker when the secure project since CMSE library is not ready.

**Note:** When the **Release** build is requested, it is necessary to change the build configuration of both the secure and non-secure application projects first. To do this, select both projects in the Project Explorer view by clicking to select the first project, then using shift-click or control-click to select the second project. Right click in the Project Explorer view to display the context-sensitive menu and select **Build Configurations** > **Set Active** > **Release**. This is also possible by using the menu item of **Project** > **Build Configuration** > **Set Active** > **Release**. After switching to the **Release** build configuration. Build the application for the secure project first.

**Run a TrustZone example application** To download and run the application, perform all steps as described in **Run an example application**. These steps are common for single core, and TrustZone applications, ensuring <br/>

<br/>

| board\_name > \_hello\_world\_s is selected for debugging. In the Quickstart Panel, click **Debug** to launch the second debug session.

Now, the TrustZone sessions should be opened. Click **Resume**. The hello\_world TrustZone application then starts running, and the secure application starts the non-secure application during runtime.

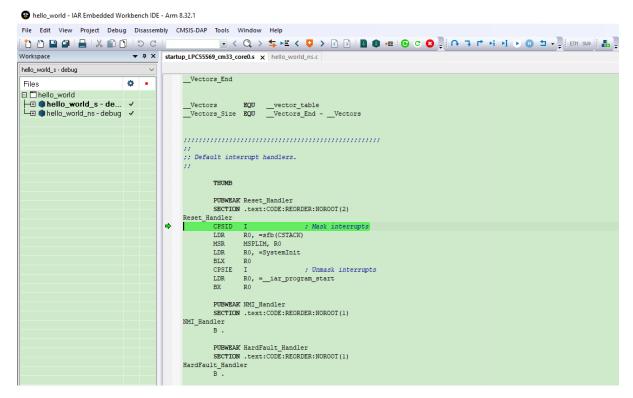

#### Run a demo application using IAR

This section describes the steps required to build, run, and debug example applications provided in the MCUXpresso SDK.

**Note:** IAR Embedded Workbench for Arm version 8.32.3 is used in the following example, and the IAR toolchain should correspond to the latest supported version, as described in the *MCUX-presso SDK Release Notes*.

**Build an example application** Do the following steps to build the hello\_world example application.

1. Open the desired demo application workspace. Most example application workspace files can be located using the following path:

Other example applications may have additional folders in their path.

2. Select the desired build target from the drop-down menu.

For this example, select hello\_world - debug.

3. To build the demo application, click Make, highlighted in red in following figure.

4. The build completes without errors.

**Run an example application** To download and run the application, perform these steps:

- 1. Ensure the host driver for the debugger firmware has been installed. See *On-board debugger*.

- 2. Connect the development platform to your PC via USB cable.

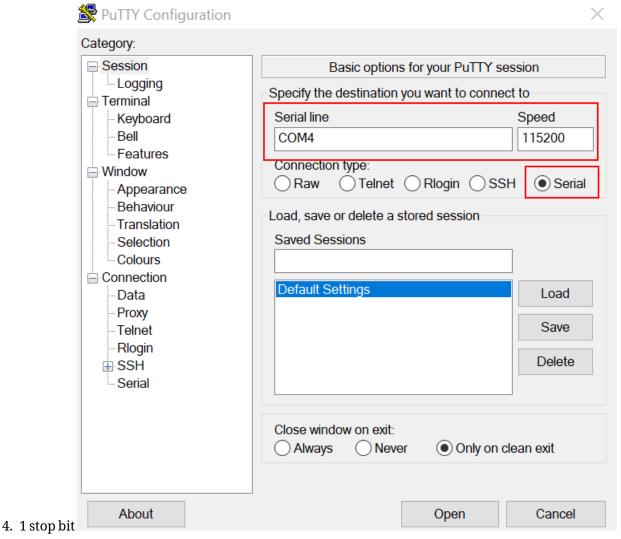

- 3. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug COM port (to determine the COM port number, see *How to determine COM port*). Configure the terminal with these settings:

- 1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in the board.h file)

- 2. No parity

- 3. 8 data bits

4. In IAR, click the **Download and Debug** button to download the application to the target.

5. The application is then downloaded to the target and automatically runs to the  $\min()$  function.

6. Run the code by clicking the **Go** button.

7. The hello\_world application is now running and a banner is displayed on the terminal. If it does not appear, check your terminal settings and connections.

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo applications workspace files are located in this folder:

Begin with a simple dual-core version of the Hello World application. The multicore Hello World IAR workspaces are located in this folder:

```

<install\_dir>/boards/lpcxpresso54114/multicore\_examples/hello\_world/cm0plus/iar/hello\_world\_cm0plus.\\ \rightarrow eww <install\_dir>/boards/lpcxpresso54114/multicore\_examples/hello\_world/cm4/iar/hello\_world\_cm4.eww

```

Build both applications separately by clicking the **Make** button. Build the application for the auxiliary core (cm0plus) first, because the primary core application project (cm4) must know the auxiliary core application binary when running the linker. It is not possible to finish the primary core linker when the auxiliary core application binary is not ready.

Run a multicore example application The primary core debugger handles flashing both primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1-4 as described in Run an example application. These steps are common for both single core and dual-core applications in IAR.

After clicking the "Download and Debug" button, the auxiliary core project is opened in the separate EWARM instance. Both the primary and auxiliary images are loaded into the device flash memory and the primary core application is executed. It stops at the default C language entry point in the \*main()\*function.

Run both cores by clicking the "Start all cores" button to start the multicore application.

During the primary core code execution, the auxiliary core is released from the reset. The hello\_world multicore application is now running and a banner is displayed on the terminal. If this does not appear, check the terminal settings and connections.

An LED controlled by the auxiliary core starts flashing, indicating that the auxiliary core has been released from the reset and is running correctly. When both cores are running, use the "Stop all cores", and "Start all cores" control buttons to stop or run both cores simultaneously.

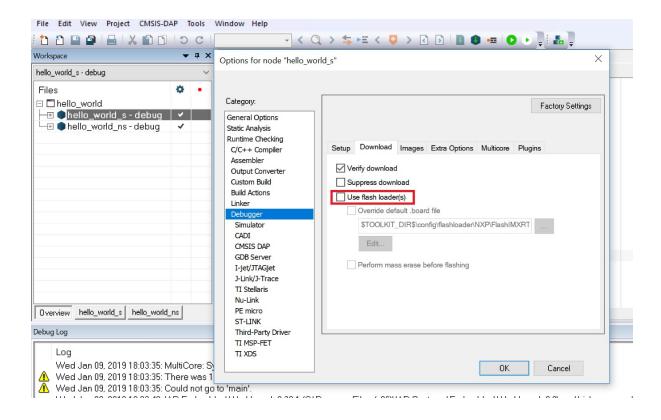

**Build a TrustZone example application** This section describes the particular steps that must be done in order to build and run a TrustZone application. The demo applications workspace files are located in this folder:

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World IAR workspaces are located in this folder:

```

< install\_dir > /boards / < board\_name > /trustzone\_examples / hello\_world / hello\_world\_ns / iar / hello\_world\_world\_world\_s. \\ < install\_dir > /boards / < board\_name > /trustzone\_examples / hello\_world / hello\_world\_s / iar / hello\_world\_s. \\ < install\_dir > /boards / < board\_name > /trustzone\_examples / hello\_world / hello\_world\_s / iar / hello\_world.eww

```

This project hello\_world.eww contains both secure and non-secure projects in one workspace and it allows the user to easily transition from one project to another. Build both applications separately by clicking **Make**. It is requested to build the application for the secure project first, because the non-secure project must know the secure project, since the CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project since CMSE library is not ready.

Run a TrustZone example application The secure project is configured to download both secure and non-secure output files, so debugging can be fully managed from the secure project. To download and run the TrustZone application, switch to the secure application project and perform steps 1-4 as described in Run an example application. These steps are common for both single core, and TrustZone applications in IAR. After clicking **Download and Debug**, both the secure and non-secure images are loaded into the device memory, and the secure application is executed. It stops at the Reset\_Handler function.

Run the code by clicking **Go** to start the application.

The TrustZone hello\_world application is now running and a banner is displayed on the terminal. If this is not true, check your terminal settings and connections.

```

COM57-PuTTY —

Hello from secure world!

Entering normal world.

Welcome in normal world!

This is a text printed from normal world!

Comparing two string as a callback to normal world

String 1: Test1

String 2: Test2

Both strings are not equal!

```

**Note:** If the application is running in RAM (debug/release build target), in **Options\*\*>\*\*Debugger > Download** tab, disable **Use flash loader(s)**. This can avoid the \_ns download issue on i.MXRT500.

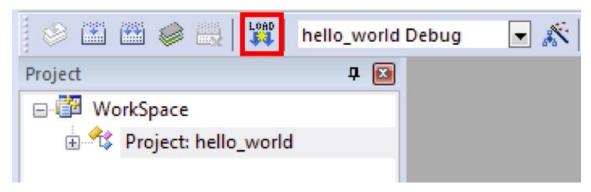

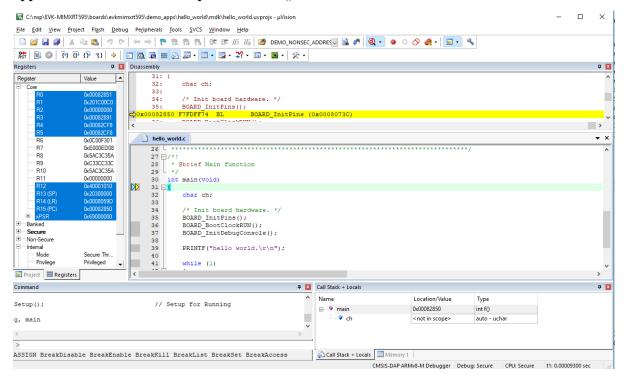

#### Run a demo using Keil MDK/µVision

This section describes the steps required to build, run, and debug example applications provided in the MCUXpresso SDK.

**Install CMSIS device pack** After the MDK tools are installed, Cortex Microcontroller Software Interface Standard (CMSIS) device packs must be installed to fully support the device from a debug perspective. These packs include things such as memory map information, register definitions, and flash programming algorithms. Follow these steps to install the appropriate CMSIS pack.

1. Open the MDK IDE, which is called  $\mu$ Vision. In the IDE, select the **Pack Installer** icon.

2. After the installation finishes, close the Pack Installer window and return to the  $\mu Vision$  IDE.

#### Build an example application

1. Open the desired example application workspace in:

The workspace file is named as <demo\_name>.uvmpw. For this specific example, the actual path is:

2. To build the demo project, select **Rebuild**, highlighted in red.

3. The build completes without errors.

**Run an example application** To download and run the application, perform these steps:

- 1. Ensure the host driver for the debugger firmware has been installed. See *On-board debugger*.

- 2. Connect the development platform to your PC via USB cable using USB connector.

- 3. Open the terminal application on the PC, such as PuTTY or TeraTerm and connect to the debug serial port number (to determine the COM port number, see *How to determine COM port*. Configure the terminal with these settings:

- 1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in the board.h file)

- 2. No parity

- 3. 8 data bits

4. In  $\mu$ Vision, after the application is built, click the **Download** button to download the application to the target.

5. After clicking the **Download** button, the application downloads to the target and is running. To debug the application, click the **Start/Stop Debug Session** button, highlighted in red.

6. Run the code by clicking the **Run** button to start the application.

The hello\_world application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo applications workspace files are located in this folder:

Begin with a simple dual-core version of the Hello World application. The multicore Hello World Keil MSDK/µVision workspaces are located in this folder:

Build both applications separately by clicking the **Rebuild** button. Build the application for the auxiliary core (cm0plus) first because the primary core application project (cm4) must know the auxiliary core application binary when running the linker. It is not possible to finish the primary core linker when the auxiliary core application binary is not ready.

Run a multicore example application The primary core debugger flashes both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1-5 as described in Run an example application. These steps are common for both single-core and dual-core applications in  $\mu$ Vision.

Both the primary and the auxiliary image is loaded into the device flash memory. After clicking the "Run" button, the primary core application is executed. During the primary core code execution, the auxiliary core is released from the reset. The hello\_world multicore application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

An LED controlled by the auxiliary core starts flashing indicating that the auxiliary core has been released from the reset and is running correctly.

Attach the running application of the auxiliary core by opening the auxiliary core project in the second  $\mu$ Vision instance and clicking the "Start/Stop Debug Session" button. After this, the second debug session is opened and the auxiliary core application can be debugged.

Arm describes multicore debugging using the NXP LPC54114 Cortex-M4/M0+ dual-core processor and Keil uVision IDE in Application Note 318 at www.keil.com/appnotes/docs/apnt\_318.asp. The associated video can be found here.

**Build a TrustZone example application** This section describes the particular steps that must be done in order to build and run a TrustZone application. The demo applications workspace files are located in this folder:

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World Keil MSDK/ $\mu$ Vision workspaces are located in this folder:

```

\label{lowerld_world_world} $$ < \frac{d_name}{tustzone}_examples/hello_world/hello_world_s/mdk/hello_world. $$ = uvmpw $$

```

This project hello\_world.uvmpw contains both secure and non-secure projects in one workspace and it allows the user to easily transition from one project to another.

Build both applications separately by clicking **Rebuild**. It is requested to build the application for the secure project first, because the non-secure project must know the secure project since CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project because CMSE library is not ready.

**Run a TrustZone example application** The secure project is configured to download both secure and non-secure output files so debugging can be fully managed from the secure project.

To download and run the TrustZone application, switch to the secure application project and perform steps as described in **Run an example application**. These steps are common for single core, dual-core, and TrustZone applications in  $\mu$ Vision. After clicking **Download and Debug**, both the secure and non-secure images are loaded into the device flash memory, and the secure application is executed. It stops at the  $\min()$  function.

Run the code by clicking **Run** to start the application.

The hello\_world application is now running and a banner is displayed on the terminal. If not, check your terminal settings and connections.

```

COM57-PuTTY

Hello from secure world!

Entering normal world.

Welcome in normal world!

This is a text printed from normal world!

Comparing two string as a callback to normal world

String 1: Test1

String 2: Test2

Both strings are not equal!

```

### Run a demo using Arm GCC

This section describes the steps to configure the command-line Arm GCC tools to build, run, and debug demo applications and necessary driver libraries provided in the MCUXpresso SDK. The hello world demo application is targeted which is used as an example.

**Set up toolchain** This section contains the steps to install the necessary components required to build and run an MCUXpresso SDK demo application with the Arm GCC toolchain, as supported by the MCUXpresso SDK. There are many ways to use Arm GCC tools, but this example focuses on a Windows operating system environment.

**Install GCC Arm Embedded tool chain** Download and run the installer from GNU Arm Embedded Toolchain. This is the actual toolset (in other words, compiler, linker, and so on). The GCC toolchain should correspond to the latest supported version, as described in **MCUXpresso SDK Release Notes**.

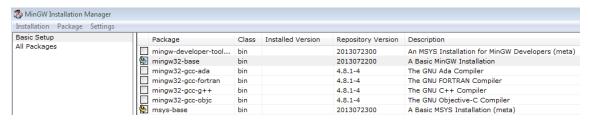

**Install MinGW (only required on Windows OS)** The Minimalist GNU for Windows (MinGW) development tools provide a set of tools that are not dependent on third-party C-Runtime DLLs (such as Cygwin). The build environment used by the MCUXpresso SDK does not use the MinGW build tools, but does leverage the base install of both MinGW and MSYS. MSYS provides a basic shell with a Unix-like interface and tools.

- 1. Download the latest MinGW mingw-get-setup installer from MinGW.

- 2. Run the installer. The recommended installation path is  $C:\MinGW$ , however, you may install to any location.

**Note:** The installation path cannot contain any spaces.

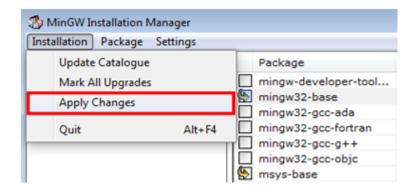

3. Ensure that the **mingw32-base** and **msys-base** are selected under **Basic Setup**.

4. In the **Installation** menu, click **Apply Changes** and follow the remaining instructions to complete the installation.

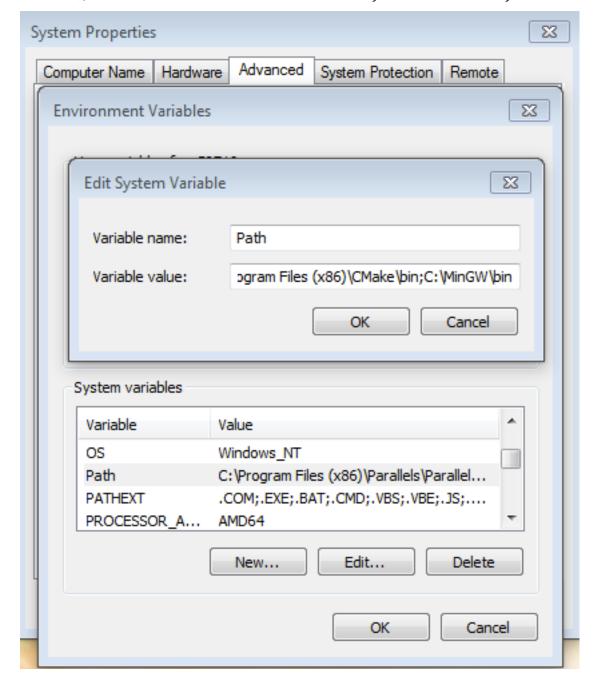

5. Add the appropriate item to the Windows operating system path environment variable. It can be found under **Control Panel->System and Security->System->Advanced System Settings** in the **Environment Variables...** section. The path is:

<mingw\_install\_dir>\bin

Assuming the default installation path,  $C:\MinGW$ , an example is shown below. If the path is not set correctly, the toolchain will not work.

**Note:** If you have  $C:\min GW \times x.x \in D$  in your PATH variable (as required by Kinetis SDK 1.0.0), remove it to ensure that the new GCC build system works correctly.

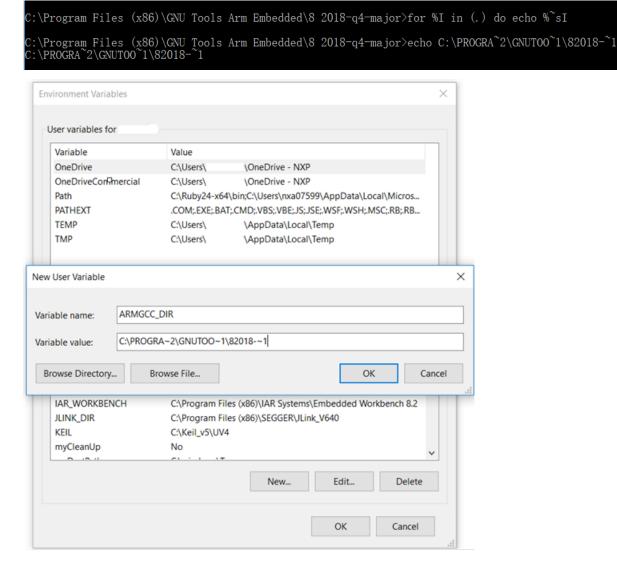

**Add a new system environment variable for ARMGCC\_DIR** Create a new *system* environment variable and name it as ARMGCC\_DIR. The value of this variable should point to the Arm GCC Embedded tool chain installation path. For this example, the path is:

C:\Program Files (x86)\GNU Tools Arm Embedded\8 2018-q4-major

See the installation folder of the GNU Arm GCC Embedded tools for the exact pathname of your installation.

Short path should be used for path setting, you could convert the path to short path by running command for %I in (.) do echo %-\$I in above path.

#### **Install CMake**

### Windows OS

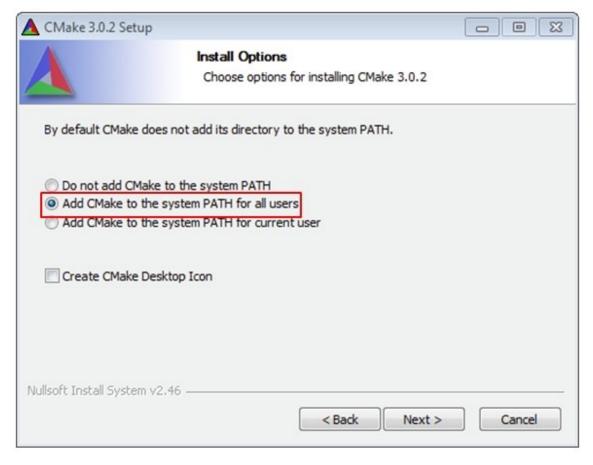

- 1. Download CMake 3.0.x from www.cmake.org/cmake/resources/software.html.

- 2. Install CMake, ensuring that the option **Add CMake to system PATH** is selected when installing. The user chooses to select whether it is installed into the PATH for all users or just the current user. In this example, it is installed for all users.

- 3. Follow the remaining instructions of the installer.

- 4. You may need to reboot your system for the PATH changes to take effect.

- 5. Make sure sh.exe is not in the Environment Variable PATH. This is a limitation of mingw32-make.

**Linux OS** It depends on the distributions of Linux Operation System. Here we use Ubuntu as an example.

Open shell and use following commands to install cmake and its version. Ensure the cmake version is above 3.0.x.

```

$ sudo apt-get install cmake

$ cmake --version

```

**Build an example application** To build an example application, follow these steps.

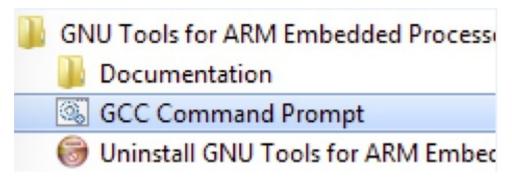

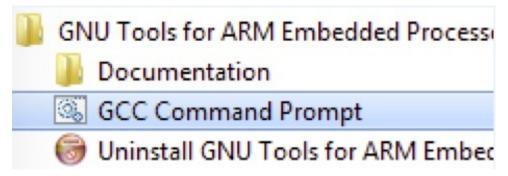

Open a GCC Arm Embedded tool chain command window. To launch the window, from the Windows operating system Start menu, go to Programs >GNU Tools Arm Embedded <version> and select GCC Command Prompt.

2. Change the directory to the example application project directory which has a path similar to the following:

```

\boxed{<\text{install\_dir}>/\text{boards}/<\text{board\_name}>/<\text{example\_type}>/<\text{application\_name}>/\text{armgcc}}

```

For this example, the exact path is:

**Note:** To change directories, use the cd command.

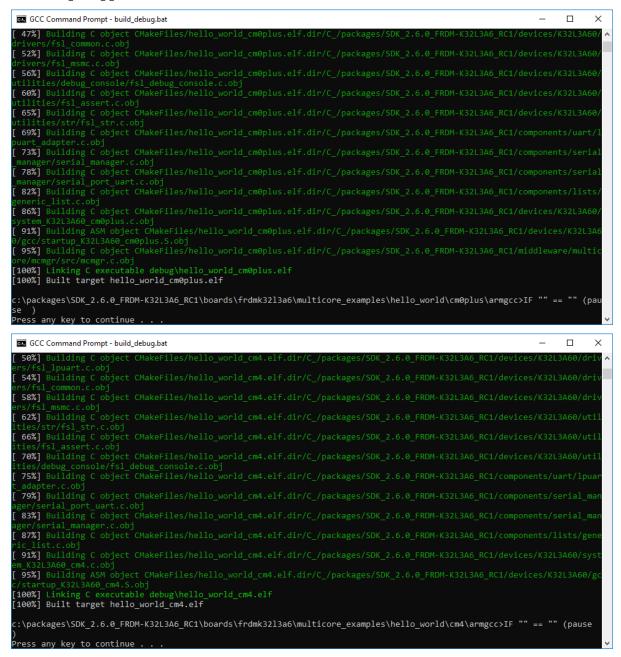

3. Type **build\_debug.bat** on the command line or double click on **build\_debug.bat** file in Windows Explorer to build it. The output is as shown in following figure.

**Run an example application** This section describes steps to run a demo application using J-Link GDB Server application. To install J-Link host driver and update the on-board debugger firmware to Jlink firmware, see *On-board debugger*.

After the J-Link interface is configured and connected, follow these steps to download and run the demo applications:

- 1. Connect the development platform to your PC via USB cable between the on-board debugger USB connector and the PC USB connector. If using a standalone J-Link debug pod, connect it to the SWD/JTAG connector of the board.

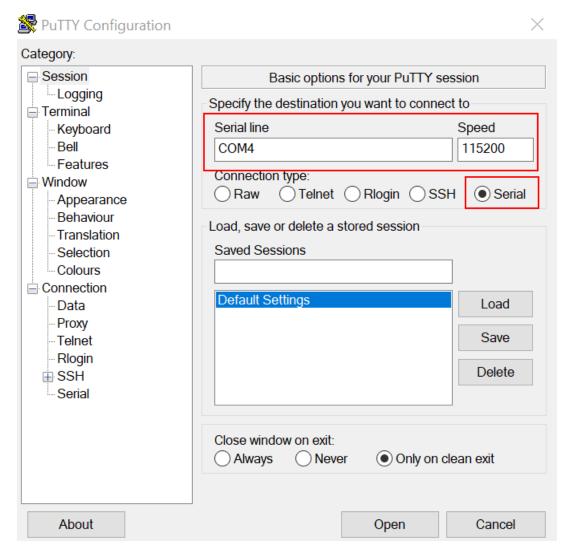

- 2. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug serial port number (to determine the COM port number, see *How to determine COM port*). Configure the terminal with these settings:

- 1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in board.h file)

- 2. No parity

- 3. 8 data bits

- 4. 1 stop bit

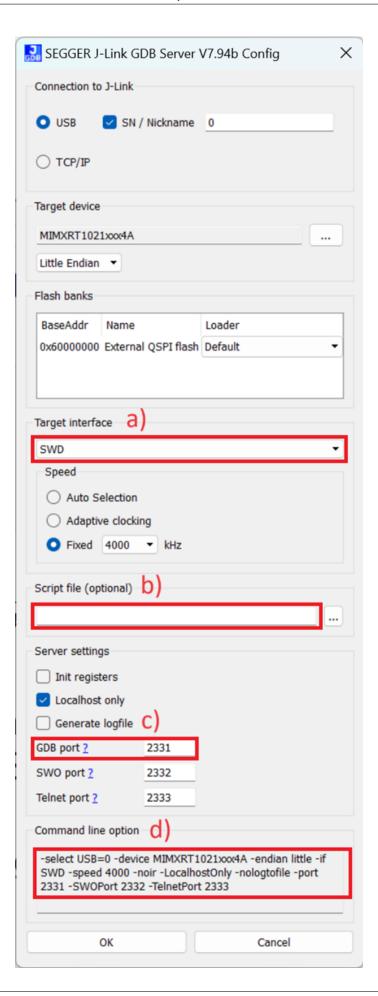

3. To launch the application, open the Windows **Start** menu and select **Programs** > **SEGGER** > **J-Link** <**version**> **J-Link GDB Server**.

**Note:** It is assumed that the J-Link software is already installed.

The **SEGGER J-Link GDB Server Config** settings dialog appears.

- 4. Make sure to check the following options.

- 1. **Target interface**: The debug connection on board uses internal SWD signaling. In case of a wrong setting J-Link is unable to communicate with device under test.

- 2. **Script file**: If required, a J-Link init script file can be used for board initialization. The file with the ".jlinkscript" file extension is located in the <install\_dir>/boards/<br/><box/directory.

- 3. Under the **Server settings**, check the GDB port for connection with the gdb target remote command. For more information, see step 9.

- 4. There is a command line version of J-Link GDB server "JLinkGDBServerCL.exe". Typical path is C: $\Program\ Files\SEGGER\JLink\$ . To start the J-Link GDB server with the same settings as are selected in the UI, you can use these command line options.

5. After it is connected, the screen should look like this figure:

SEGGER J-Link GDB Server V6.46g

- - - - - >

6. If not already running, open a GCC Arm Embedded tool chain command window. To launch the window, from the Windows operating system Start menu, go to **Programs - GNU Tools Arm Embedded <version>** and select **GCC Command Prompt**.

7. Change to the directory that contains the example application output. The output can be found in using one of these paths, depending on the build target selected:

```

\label{lem:constall_dir} $$ \left(\frac{dir}{boards} - \frac{name}{c}\right) = \frac{type}{c} - \frac{application_name}{armgcc/debug} $$ \left(\frac{dir}{boards} - \frac{name}{c}\right) = \frac{type}{c} - \frac{application_name}{armgcc/release} $$ \left(\frac{dir}{boards} - \frac{armgcc}{armgcc/release}\right) = \frac{armgcc}{armgcc/release} $$ \left(\frac{dir}{boards} - \frac{armgcc}{armgcc/release}\right) = \frac{a

```

8. Run the arm-none-eabi-gdb.exe <application\_name>.elf command. For this example, it is arm-none-eabi-gdb.exe hello world.elf.

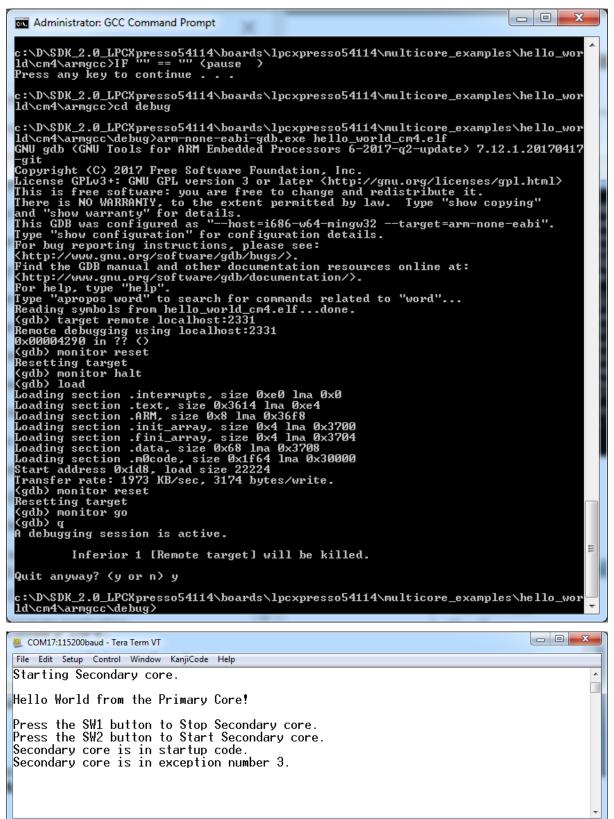

- 9. Run these commands:

- 1. target remote localhost:2331

- 2. monitor reset

- 3. monitor halt

- 4. load

- 5. monitor reset

- 10. The application is now downloaded and halted. Execute the  ${

m monitor~go}$  command to start the demo application.

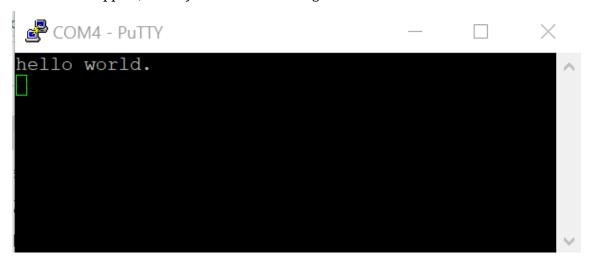

The hello\_world application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo application build scripts are located in this folder:

Begin with a simple dual-core version of the Hello World application. The multicore Hello World GCC build scripts are located in this folder:

```

\label{localization} $$ < install\_dir > /boards/lpcxpresso54114/multicore\_examples/hello\_world/cm0plus/armgcc/build\_debug.bat $$ < install\_dir > /boards/lpcxpresso54114/multicore\_examples/hello\_world/cm4/armgcc/build\_debug.bat $$ < install\_dir > /boards/lpcxpresso54114/multicore\_examples/hello\_world/cm4/armgcc/build\_debug.bat

```

Build both applications separately following steps for single core examples as described in **Build** an example application.

**Run a multicore example application** When running a multicore application, the same prerequisites for J-Link/J-Link OpenSDA firmware, and the serial console as for the single-core application, applies, as described in **Run an example application**.

The primary core debugger handles flashing of both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1 to 10, as described in **Run an example application**. These steps are common for both single-core and dual-core applications in Arm GCC.

Both the primary and the auxiliary image is loaded into the SPI flash memory. After execution of the monitor go command, the primary core application is executed. During the primary core code execution, the auxiliary core code is reallocated from the flash memory to the RAM, and the auxiliary core is released from the reset. The hello\_world multicore application is now running

and a banner is displayed on the terminal. If this is not true, check your terminal settings and connections.

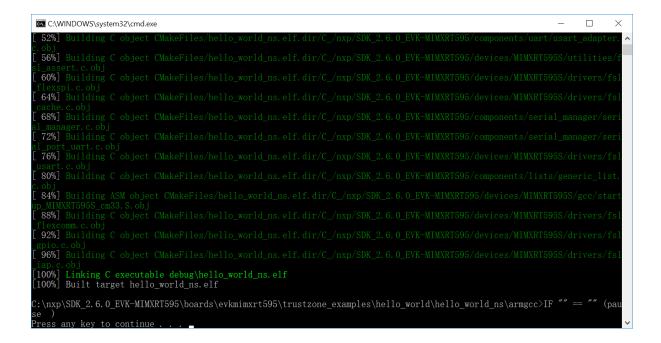

**Build a TrustZone example application** This section describes the steps to build and run a TrustZone application. The demo application build scripts are located in this folder:

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World GCC build scripts are located in this folder:

```

$$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world / hello_world_ns / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world / hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world / hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world / hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world / hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world_hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world_hello_world_s / armgcc / build_odebug.bat $$ < \armsontonians / boards / coard_name > / trustzone_examples / hello_world_hello_world_hello_world_s / boards / coard_name > / trustzone_examples / hello_world_hello_world_s / boards / coard_name > / trustzone_examples / hello_world_hello_world_hello_world_s / boards / coard_name > / trustzone_examples / hello_world_hello_world_hello_world_s / boards / coard_name > / trustzone_examples / hello_world_hello_world_hello_world_hello_world_s / boards / coard_name > / trustzone_examples / hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_world_hello_wor

```

Build both applications separately, following steps for single core examples as described in **Build** an example application. It is requested to build the application for the secure project first, because the non-secure project must know the secure project, since CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project because the CMSE library is not ready.

**Run a TrustZone example application** When running a TrustZone application, the same prerequisites for J-Link/J-Link OpenSDA firmware, and the serial console as for the single core application, apply, as described in **Run an example application**.

To download and run the TrustZone application, perform steps 1 to 10, as described in **Run an example application**. These steps are common for both single core and TrustZone applications in Arm GCC.

# Then, run these commands:

- 1. arm-none-eabi-gdb.exe

- 2. target remote localhost:2331

- 3. monitor reset

- 4. monitor halt

- 5. monitor exec SetFlashDLNoRMWThreshold = 0x20000

- 7. load <install\_dir>/boards/evkmimxrt595/trustzone\_examples/hello\_world/hello\_world\_s/armgcc/debug/hello world s.elf

- 8. monitor reset

The application is now downloaded and halted. Execute the  ${\ensuremath{c}}$  command to start the demo application.

```

Command Prompt - arm-none-eabi-gdb

C:\nxp\SDK_2.6.0_EVK-MIMXRT595\boards\evkmimxrt595\trustzone_examples\hello_world>arm-none-eabi-gdb

C:\Program Files (x86)\GNU Tools Arm Embedded\8 2018-q4-major\bin\arm-none-eabi-gdb.exe: warning: Couldn't determine a p

ath for the index cache directory.

GNU gdb (GNU Tools for Arm Embedded Processors 8-2018-q4-major) 8.2.50.20181213-git

Copyright (C) 2018 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later \http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law.

Type "show copying" and "show warranty" for details.

This GDB was configured as "--host=i686-w64-mingw32 --target=arm-none-eabi".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

\http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

\http://www.gnu.org/software/gdb/documentation/>.

<http://www.gnu.org/software/gdb/documentation/</pre>

or help, type "help

or help, type help.

Type "apropos word" to search for commands related to "word".

(gdb) target remote localhost:2331

Remote debugging using localhost:2331

warning: No executable has been specified and target does not support determining executable automatically. Try using the "file" command.

warning: No executable has been specified and target uses determining executable automatically. Try using the "file 0x0001c04a in ?? () (gdb) load hello_world_ns/armgcc/debug/hello_world_ns.elf Loading section .interrupts, size 0x163 lma 0xc0180 Loading section .ext, size 0x1d30 lma 0xc1eb0 Loading section .ARM, size 0x8 lma 0xcleb0 Loading section .init_array, size 0x4 lma 0xcleb8 Loading section .fini_array, size 0x4 lma 0xclebc Loading section .data, size 0x60 lma 0xclec0 Start address 0xc0234, load size 7944 Transfer rate: 74 KB/sec, 1324 bytes/write. (gdb) load hello_world_s/armgcc/debug/hello_world_s.elf Loading section .flash_config, size 0x200 lma 0x1007f400 Loading section .flash_config, size 0x200 lma 0x1007f400 Loading section .text, size 0x4d54 lma 0x10080000 Loading section .ARM, size 0x8 lma 0x10084ed4 Loading section .init_array, size 0x4 lma 0x10084ee0 Loading section .fini_array, size 0x4 lma 0x10084ee0 Loading section .data, size 0x68 lma 0x10084ee0 Loading section .gnu.sgstubs, size 0x20 lma 0x100bfe00 Start address 0x10080234, load size 20820 Transfer rate: 123 KB/sec, 2313 bytes/write.

Transfer rate: 123 KB/sec, 2313 bytes/write.

ontinuing.

COM57 - PuTTY

Hello from secure world!

Entering normal world.

Welcome in normal world!

This is a text printed from normal world!

Comparing two string as a callback to normal world

String 1: Testl

String 2: Test2

Both strings are not equal!

```

# **MCUXpresso Config Tools**

MCUXpresso Config Tools can help configure the processor and generate initialization code for the on chip peripherals. The tools are able to modify any existing example project, or create a new configuration for the selected board or processor. The generated code is designed to be used with MCUXpresso SDK version 24.12.00 or later.

Following table describes the tools included in the MCUXpresso Config Tools.

| Config Tool                          | Description                                                                                                                                                                    | Im-<br>age                                   |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Pins tool                            | For configuration of pin routing and pin electrical properties.                                                                                                                |                                              |

| Clock tool                           | For system clock configuration                                                                                                                                                 | (III)                                        |

| Peripher-<br>als tools               | For configuration of other peripherals                                                                                                                                         | P                                            |

| TEE tool                             | Configures access policies for memory area and peripherals helping to protect and isolate sensitive parts of the application.                                                  |                                              |

| Device<br>Config-<br>uration<br>tool | Configures Device Configuration Data (DCD) contained in the program image that the Boot ROM code interprets to set up various on-chip peripherals prior to the program launch. | <u>*************************************</u> |

MCUXpresso Config Tools can be accessed in the following products:

- **Integrated** in the MCUXpresso IDE. Config tools are integrated with both compiler and debugger which makes it the easiest way to begin the development.

- **Standalone version** available for download from www.nxp.com/mcuxpresso. Recommended for customers using IAR Embedded Workbench, Keil MDK μVision, or Arm GCC.

- **Online version** available on mcuxpresso.nxp.com. Recommended doing a quick evaluation of the processor or use the tool without installation.

Each version of the product contains a specific *Quick Start Guide* document MCUXpresso IDE Config Tools installation folder that can help start your work.

### **How to determine COM port**

This section describes the steps necessary to determine the debug COM port number of your NXP hardware development platform. All NXP boards ship with a factory programmed, onboard debug interface, whether it is based on MCU-Link or the legacy OpenSDA, LPC-Link2, P&E Micro OSJTAG interface. To determine what your specific board ships with, see *Default debug interfaces*.

1. **Linux**: The serial port can be determined by running the following command after the USB Serial is connected to the host:

```

$ dmesg | grep "ttyUSB"

[503175.307873] usb 3-12: cp210x converter now attached to ttyUSB0

[503175.309372] usb 3-12: cp210x converter now attached to ttyUSB1

```

There are two ports, one is for core0 debug console and the other is for core1.

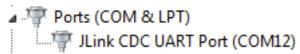

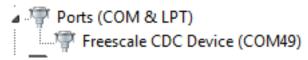

2. **Windows**: To determine the COM port open Device Manager in the Windows operating system. Click the **Start** menu and type **Device Manager** in the search bar.

In the Device Manager, expand the **Ports (COM & LPT)** section to view the available ports. The COM port names are different for all the NXP boards.

1. CMSIS-DAP/mbed/DAPLink interface:

#### 2. P&E Micro:

# 3. **J-Link**:

# 4. P&E Micro OSJTAG:

```

Ports (COM & LPT)

Ports (COM & LPT)

OSBDM/OSJTAG - CDC Serial Port (http://www.pemicro.com/osbdm, http://www.pemicro.com/opensda) (COM43)

```

### 5. MRB-KW01:

### **On-board Debugger**

This section describes the on-board debuggers used on NXP development boards.

On-board debugger MCU-Link MCU-Link is a powerful and cost effective debug probe that can be used seamlessly with MCUXpresso IDE, and is also compatible with 3rd party IDEs that support CMSIS-DAP protocol. MCU-Link also includes a USB to UART bridge feature (VCOM) that can be used to provide a serial connection between the target MCU and a host computer. MCU-Link features a high-speed USB interface for high performance debug. MCU-Link is compatible with Windows, MacOS and Linux. A free utility from NXP provides an easy way to install firmware updates.

On-board MCU-Link debugger supports CMSIS-DAP and J-Link firmware. See the table in *Default debug interfaces* to determine the default debug interface that comes loaded on your specific hardware platform.

# The corresponding host driver must be installed before debugging.

- For boards with CMSIS-DAP firmware, visit developer.mbed.org/handbook/Windows-serial-configuration and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- If using J-Link with either a standalone debug pod or MCU-Link, install the J-Link software (drivers and utilities) from www.segger.com/jlink-software.html.

**Updating MCU-Link firmware** This firmware in this debug interface may be updated using the host computer utility called MCU-Link. This typically used when switching between the default debugger protocol (CMSIS-DAP) to SEGGER J-Link, or for updating this firmware with new releases of these. This section contains the steps to reprogram the debug probe firmware.

**Note:** If MCUXpresso IDE is used and the jumper making DFUlink is installed on the board (JP5 on some boards, but consult the board user manual or schematic for specific jumper number), MCU-Link debug probe boots to DFU mode, and MCUXpresso IDE automatically downloads the

CMSIS-DAP firmware to the probe before flash memory programming (after clicking **Debug**). Using DFU mode ensures that most up-to-date/compatible firmware is used with MCUXpresso IDE.

NXP provides the MCU-Link utility, which is the recommended tool for programming the latest versions of CMSIS-DAP and J-Link firmware onto MCU-Link or NXP boards. The utility can be downloaded from MCU-Link.

These steps show how to update the debugger firmware on your board for Windows operating system.

- 1. Install the MCU-Link utility.

- 2. Unplug the board's USB cable.

- 3. Make the DFU link (install the jumper labeled DFUlink).

- 4. Connect the probe to the host via USB (use Link USB connector).

- 5. Open a command shell and call the appropriate script located in the MCU-Link installation directory (<MCU-Link install dir>).

- 1. To program CMSIS-DAP debug firmware:  ${\rm <MCU\text{-}Link~install~dir>/scripts/program\_CMSIS}$

- 2. To program J-Link debug firmware: <MCU-Link install dir>/scripts/program\_JLINK

- 6. Remove DFU link (remove the jumper installed in Step 3).

- 7. Repower the board by removing the USB cable and plugging it in again.

**On-board debugger LPC-Link** LPC-Link 2 is an extensible debug probe that can be used seamlessly with MCUXpresso IDE, and is also compatible with 3rd party IDEs that support CMSIS-DAP protocol. MCU-Link also includes a USB to UART bridge feature (VCOM) that can be used to provide a serial connection between the target MCU and a host computer. LPC-Link 2 is compatible with Windows, MacOS and Linux. A free utility from NXP provides an easy way to install firmware updates.

On-board LPC-Link 2 debugger supports CMSIS-DAP and J-Link firmware. See the table in *Default debug interfaces* to determine the default debug interface that comes loaded on your specific hardware platform.

### The corresponding host driver must be installed before debugging.

- For boards with CMSIS-DAP firmware, visit developer.mbed.org/handbook/Windowsserial-configuration and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- If using J-Link with either a standalone debug pod or MCU-Link, install the J-Link software (drivers and utilities) from www.segger.com/jlink-software.html.

**Updating LPC-Link firmware** The LPCXpresso hardware platform comes with a CMSIS-DAP-compatible debug interface (known as LPC-Link2). This firmware in this debug interface may be updated using the host computer utility called LPCScrypt. This typically used when switching between the default debugger protocol (CMSIS-DAP) to SEGGER J-Link, or for updating this firmware with new releases of these. This section contains the steps to reprogram the debug probe firmware.

**Note:** If MCUXpresso IDE is used and the jumper making DFUlink is installed on the board (JP5 on some boards, but consult the board user manual or schematic for specific jumper number), LPC-Link2 debug probe boots to DFU mode, and MCUXpresso IDE automatically downloads the CMSIS-DAP firmware to the probe before flash memory programming (after clicking **Debug**). Using DFU mode ensures that most up-to-date/compatible firmware is used with MCUXpresso IDE.

NXP provides the LPCScrypt utility, which is the recommended tool for programming the latest versions of CMSIS-DAP and J-Link firmware onto LPC-Link2 or LPCXpresso boards. The utility can be downloaded from LPCScrypt.

These steps show how to update the debugger firmware on your board for Windows operating system. For Linux OS, follow the instructions described in LPCScrypt user guide (LPCScrypt, select **LPCScrypt**, and then the documentation tab).

- 1. Install the LPCScript utility.

- 2. Unplug the board's USB cable.

- 3. Make the DFU link (install the jumper labeled DFUlink).

- 4. Connect the probe to the host via USB (use Link USB connector).

- 5. Open a command shell and call the appropriate script located in the LPCScrypt installation directory (<LPCScrypt install dir>).

- 1. To program CMSIS-DAP debug firmware: <LPCScrypt install dir>/scripts/program\_CMSIS

- 2. To program J-Link debug firmware: <LPCScrypt install dir>/scripts/program\_JLINK

- 6. Remove DFU link (remove the jumper installed in Step 3).

- 7. Repower the board by removing the USB cable and plugging it in again.

**On-board debugger OpenSDA** OpenSDA/OpenSDAv2 is a serial and debug adapter that is built into several NXP evaluation boards. It provides a bridge between your computer (or other USB host) and the embedded target processor, which can be used for debugging, flash programming, and serial communication, all over a simple USB cable.

The difference is the firmware implementation: OpenSDA: Programmed with the proprietary P&E Micro developed bootloader. P&E Micro is the default debug interface app. OpenSDAv2: Programmed with the open-sourced CMSIS-DAP/mbed bootloader. CMSIS-DAP is the default debug interface app.

See the table in *Default debug interfaces* to determine the default debug interface that comes loaded on your specific hardware platform.

# The corresponding host driver must be installed before debugging.

- For boards with CMSIS-DAP firmware, visit developer.mbed.org/handbook/Windows-serial-configuration and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- For boards with a P&E Micro interface, see PE micro to download and install the P&E Micro Hardware Interface Drivers package.

**Updating OpenSDA firmware** Any NXP hardware platform that comes with an OpenSDA-compatible debug interface has the ability to update the OpenSDA firmware. This typically means to switch from the default application (either CMSIS-DAP or P&E Micro) to a SEGGER J-Link. This section contains the steps to switch the OpenSDA firmware to a J-Link interface. However, the steps can be applied to restoring the original image also. For reference, OpenSDA firmware files can be found at the links below:

- J-Link: Download appropriate image from www.segger.com/opensda.html. Choose the appropriate J-Link binary based on the table in *Default debug interfaces*. Any OpenSDA v1.0 interface should use the standard OpenSDA download (in other words, the one with no version). For OpenSDA 2.0 or 2.1, select the corresponding binary.

- CMSIS-DAP: CMSIS-DAP OpenSDA firmware is available at www.nxp.com/opensda.

• P&E Micro: Downloading P&E Micro OpenSDA firmware images requires registration with P&E Micro (www.pemicro.com).

Perform the following steps to update the OpenSDA firmware on your board for Windows and Linux OS users:

- 1. Unplug the board's USB cable.

- 2. Press the **Reset** button on the board. While still holding the button, plug the USB cable back into the board.

- 3. When the board re-enumerates, it shows up as a disk drive called **MAINTENANCE**.

4. Drag and drop the new firmware image onto the MAINTENANCE drive.

**Note:** If for any reason the firmware update fails, the board can always reenter maintenance mode by holding down **Reset** button and power cycling.

These steps show how to update the OpenSDA firmware on your board for Mac OS users.

- 1. Unplug the board's USB cable.

- 2. Press the **Reset** button of the board. While still holding the button, plug the USB cable back into the board.

- 3. For boards with OpenSDA v2.0 or v2.1, it shows up as a disk drive called **BOOTLOADER** in **Finder**. Boards with OpenSDA v1.0 may or may not show up depending on the bootloader version. If you see the drive in **Finder**, proceed to the next step. If you do not see the drive in Finder, use a PC with Windows OS 7 or an earlier version to either update the OpenSDA firmware, or update the OpenSDA bootloader to version 1.11 or later. The bootloader update instructions and image can be obtained from P&E Microcomputer website.

- 4. For OpenSDA v2.1 and OpenSDA v1.0 (with bootloader 1.11 or later) users, drag the new firmware image onto the BOOTLOADER drive in **Finder**.

- 5. For OpenSDA v2.0 users, type these commands in a Terminal window:

```

> sudo mount -u -w -o sync /Volumes/BOOTLOADER

> cp -X <path to update file> /Volumes/BOOTLOADER

```

**Note:** If for any reason the firmware update fails, the board can always reenter bootloader mode by holding down the **Reset** button and power cycling.