# MCUXpresso SDK Documentation

Release 25.09.00

NXP

Sep 19, 2025

# Table of contents

|                                                                                                   |            |

|---------------------------------------------------------------------------------------------------|------------|

| <b>1 MCXW23-EVK</b>                                                                               | <b>3</b>   |

| 1.1 Overview . . . . .                                                                            | 3          |

| 1.2 Getting Started with MCUXpresso SDK GitHub . . . . .                                          | 4          |

| 1.2.1 Getting Started with MCUXpresso SDK Repository . . . . .                                    | 4          |

| 1.2.2 How to determine COM Port . . . . .                                                         | 17         |

| 1.2.3 Updating debugger firmware . . . . .                                                        | 18         |

| 1.3 Release Notes . . . . .                                                                       | 19         |

| 1.3.1 MCUXpresso SDK Release Notes . . . . .                                                      | 19         |

| 1.4 ChangeLog . . . . .                                                                           | 26         |

| 1.4.1 MCUXpresso SDK Changelog . . . . .                                                          | 26         |

| 1.5 Driver API Reference Manual . . . . .                                                         | 71         |

| 1.6 Middleware Documentation . . . . .                                                            | 71         |

| 1.6.1 Wireless Bluetooth LE host stack and applications . . . . .                                 | 71         |

| 1.6.2 Wireless Connectivity Framework . . . . .                                                   | 71         |

| 1.6.3 FreeRTOS . . . . .                                                                          | 135        |

| <b>2 MCXW236B</b>                                                                                 | <b>137</b> |

| 2.1 ANACTRL: Analog Control Driver . . . . .                                                      | 137        |

| 2.2 CASPER: The Cryptographic Accelerator and Signal Processing Engine with RAM sharing . . . . . | 142        |

| 2.3 casper_driver . . . . .                                                                       | 142        |

| 2.4 casper_driver_pkha . . . . .                                                                  | 145        |

| 2.5 CDOG . . . . .                                                                                | 148        |

| 2.6 CRC: Cyclic Redundancy Check Driver . . . . .                                                 | 152        |

| 2.7 CTIMER: Standard counter/timers . . . . .                                                     | 155        |

| 2.8 DMA: Direct Memory Access Controller Driver . . . . .                                         | 164        |

| 2.9 FLEXCOMM: FLEXCOMM Driver . . . . .                                                           | 181        |

| 2.10 FLEXCOMM Driver . . . . .                                                                    | 181        |

| 2.11 GINT: Group GPIO Input Interrupt Driver . . . . .                                            | 182        |

| 2.12 Hashcrypt: The Cryptographic Accelerator . . . . .                                           | 185        |

| 2.13 Hashcrypt Background HASH . . . . .                                                          | 185        |

| 2.14 Hashcrypt common functions . . . . .                                                         | 186        |

| 2.15 Hashcrypt AES . . . . .                                                                      | 188        |

| 2.16 Hashcrypt HASH . . . . .                                                                     | 193        |

| 2.17 I2C: Inter-Integrated Circuit Driver . . . . .                                               | 194        |

| 2.18 I2C DMA Driver . . . . .                                                                     | 194        |

| 2.19 I2C Driver . . . . .                                                                         | 196        |

| 2.20 I2C Master Driver . . . . .                                                                  | 200        |

| 2.21 I2C Slave Driver . . . . .                                                                   | 209        |

| 2.22 INPUTMUX: Input Multiplexing Driver . . . . .                                                | 218        |

| 2.23 Common Driver . . . . .                                                                      | 219        |

| 2.24 GPIO: General Purpose I/O . . . . .                                                          | 231        |

| 2.25 IOCON: I/O pin configuration . . . . .                                                       | 233        |

| 2.26 Mailbox . . . . .                                                                            | 234        |

| 2.27 MRT: Multi-Rate Timer . . . . .                                                              | 235        |

| 2.28 OSTIMER: OS Event Timer Driver . . . . .                                                     | 240        |

|          |                                                                                 |            |

|----------|---------------------------------------------------------------------------------|------------|

| 2.29     | PINT: Pin Interrupt and Pattern Match Driver . . . . .                          | 243        |

| 2.30     | PLU: Programmable Logic Unit . . . . .                                          | 252        |

| 2.31     | PUF: Physical Unclonable Function . . . . .                                     | 261        |

| 2.32     | RTC: Real Time Clock . . . . .                                                  | 263        |

| 2.33     | SCTimer: SCTimer/PWM (SCT) . . . . .                                            | 269        |

| 2.34     | SPI: Serial Peripheral Interface Driver . . . . .                               | 286        |

| 2.35     | SPI DMA Driver . . . . .                                                        | 286        |

| 2.36     | SPI Driver . . . . .                                                            | 290        |

| 2.37     | SPIFI: SPIFI flash interface driver . . . . .                                   | 298        |

| 2.38     | SPIFI DMA Driver . . . . .                                                      | 307        |

| 2.39     | SPIFI Driver . . . . .                                                          | 307        |

| 2.40     | TRNG: True Random Number Generator . . . . .                                    | 307        |

| 2.41     | USART: Universal Synchronous/Asynchronous Receiver/Transmitter Driver . . . . . | 311        |

| 2.42     | USART DMA Driver . . . . .                                                      | 312        |

| 2.43     | USART Driver . . . . .                                                          | 314        |

| 2.44     | UTICK: MictoTick Timer Driver . . . . .                                         | 330        |

| 2.45     | WWDT: Windowed Watchdog Timer Driver . . . . .                                  | 331        |

| <b>3</b> | <b>Middleware</b> . . . . .                                                     | <b>335</b> |

| 3.1      | Wireless . . . . .                                                              | 335        |

| 3.1.1    | NXP Wireless Framework and Stacks . . . . .                                     | 335        |

| <b>4</b> | <b>RTOS</b> . . . . .                                                           | <b>337</b> |

| 4.1      | FreeRTOS . . . . .                                                              | 337        |

| 4.1.1    | FreeRTOS kernel . . . . .                                                       | 337        |

| 4.1.2    | FreeRTOS drivers . . . . .                                                      | 343        |

| 4.1.3    | backoffalgorithm . . . . .                                                      | 343        |

| 4.1.4    | corehttp . . . . .                                                              | 346        |

| 4.1.5    | corejson . . . . .                                                              | 348        |

| 4.1.6    | coremqtt . . . . .                                                              | 351        |

| 4.1.7    | coremqtt-agent . . . . .                                                        | 354        |

| 4.1.8    | corepkcs11 . . . . .                                                            | 358        |

| 4.1.9    | freertos-plus-tcp . . . . .                                                     | 361        |

This documentation contains information specific to the mcxw23evk board.

# Chapter 1

## MCXW23-EVK

### 1.1 Overview

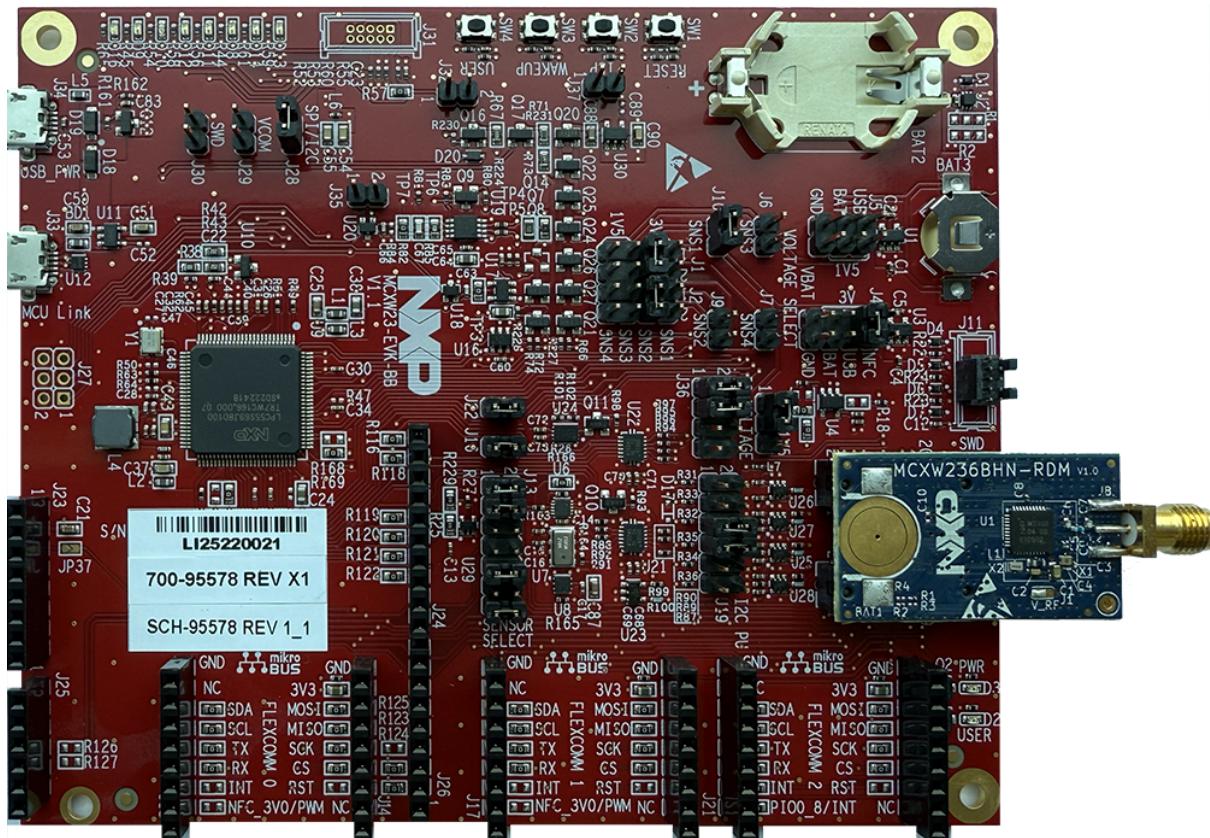

The NXP MCXW23-EVK is a development board for the MCXW23 32 MHz Arm Cortex-M33 microcontroller.

MCU device and part on board is shown below:

- Device: MCXW236B

- PartNumber: MCXW236BIHNAR

## 1.2 Getting Started with MCUXpresso SDK GitHub

Before debugging the silicon, remove the jumper on J32.

### 1.2.1 Getting Started with MCUXpresso SDK Repository

#### Installation

##### NOTE

If the installation instruction asks/selects whether to have the tool installation path added to the PATH variable, agree/select the choice. This option ensures that the tool can be used in any terminal in any path. *Verify the installation* after each tool installation.

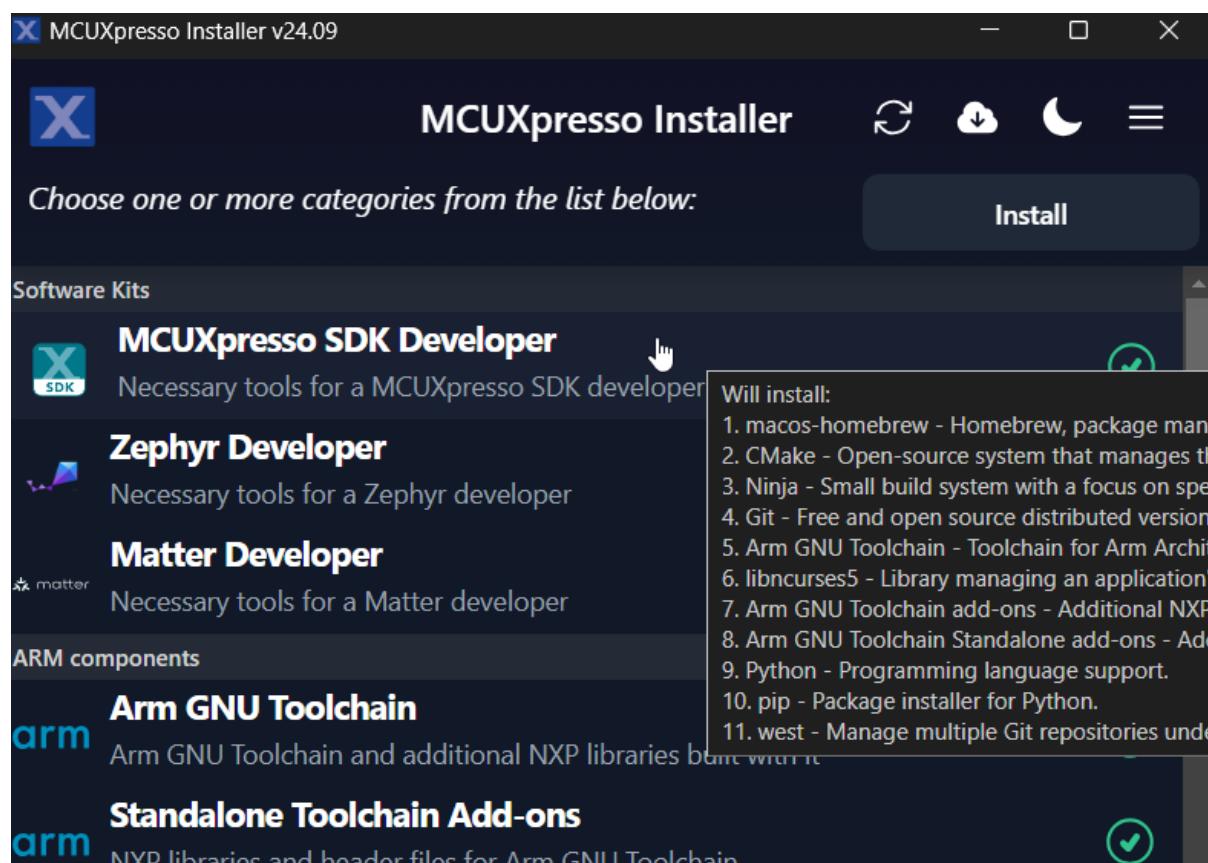

**Install Prerequisites with MCUXpresso Installer** The MCUXpresso Installer offers a quick and easy way to install the basic tools needed. The MCUXpresso Installer can be obtained from <https://github.com/nxp-mcuxpresso/vscode-for-mcux/wiki/Dependency-Installation>. The MCUXpresso Installer is an automated installation process, simply select MCUXpresso SDK Developer from the menu and click install. If you prefer to install the basic tools manually, refer to the next section.

#### Alternative: Manual Installation

##### Basic tools

**Git** Git is a free and open source distributed version control system. Git is designed to handle everything from small to large projects with speed and efficiency. To install Git, visit the official [Git website](#). Download the appropriate version(you may use the latest one) for your operating system (Windows, macOS, Linux). Then run the installer and follow the installation instructions.

User `git --version` to check the version if you have a version installed.

Then configure your username and email using the commands:

```

git config --global user.name "Your Name"

git config --global user.email "youremail@example.com"

```

**Python** Install python 3.10 or latest. Follow the [Python Download](#) guide.

Use `python --version` to check the version if you have a version installed.

**West** Please use the west version equal or greater than 1.2.0

```

# Note: you can add option '--default-timeout=1000' if you meet connection issue. Or you may set a different

# source using option '-i'.

# for example, in China you could try: pip install -U west -i https://pypi.tuna.tsinghua.edu.cn/simple

pip install -U west

```

## Build And Configuration System

**CMake** It is strongly recommended to use CMake version equal or later than 3.30.0. You can get latest CMake distributions from [the official CMake download page](#).

For Windows, you can directly use the .msi installer like [cmake-3.31.4-windows-x86\\_64.msi](#) to install.

For Linux, CMake can be installed using the system package manager or by getting binaries from [the official CMake download page](#).

After installation, you can use `cmake --version` to check the version.

**Ninja** Please use the ninja version equal or later than 1.12.1.

By default, Windows comes with the Ninja program. If the default Ninja version is too old, you can directly download the [ninja binary](#) and register the ninja executor location path into your system path variable to work.

For Linux, you can use your system package manager or you can directly download the [ninja binary](#) to work.

After installation, you can use `ninja --version` to check the version.

**Kconfig** MCUXpresso SDK uses Kconfig python implementation. We customize it based on our needs and integrate it into our build and configuration system. The Kconfiglib sources are placed under `mcux-sdk/scripts/kconfig` folder.

Please make sure [python](#) environment is setup ready then you can use the Kconfig.

**Ruby** Our build system supports IDE project generation for iar, mdk, codewarrior and xtensa to provide OOB from build to debug. This feature is implemented with ruby. You can follow the guide ruby environment setup to setup the ruby environment. Since we provide a built-in portable ruby, it is just a simple one cmd installation.

If you only work with CLI, you can skip this step.

**Toolchain** MCUXpresso SDK supports all mainstream toolchains for embedded development. You can install your used or interested toolchains following the guides.

| Toolchain                    | Download and Installation Guide                                      | Note                        |

|------------------------------|----------------------------------------------------------------------|-----------------------------|

| Armgcc                       | <a href="#">Arm GNU Toolchain Install Guide</a>                      | ARMGCC is default toolchain |

| IAR                          | <a href="#">IAR Installation and Licensing quick reference guide</a> |                             |

| MDK                          | <a href="#">MDK Installation</a>                                     |                             |

| Armclang                     | <a href="#">Installing Arm Compiler for Embedded</a>                 |                             |

| Zephyr                       | <a href="#">Zephyr SDK</a>                                           |                             |

| Codewarrior                  | <a href="#">NXP CodeWarrior</a>                                      |                             |

| Xtensa                       | <a href="#">Tensilica Tools</a>                                      |                             |

| NXP S32Compiler RISC-V Zen-V | <a href="#">NXP Website</a>                                          |                             |

After you have installed the toolchains, register them in the system environment variables. This will allow the west build to recognize them:

| Toolchain              | Environment Variable | Example                                                                                                                                                | Cmd Line Argument        |

|------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Armgcc                 | AR-MGCC_DIR          | C:\armgcc for windows/usr for Linux. arm-none-eabi-* is installed under /usr/bin                                                                       | – toolchain armgcc       |

| IAR                    | IAR_DIR              | C:\iar\ewarm-9.60.3 for Windows/opt/iar/systems/bxarm-9.60.3 for Linux                                                                                 | – toolchain iar          |

| MDK                    | MDK_DIR              | C:\Keil_v5 for Windows.MDK IDE is not officially supported with Linux.                                                                                 | – toolchain mdk          |

| Armclang               | ARM-CLANG_DIR        | C:\ArmCompilerforEmbedded6.22 for Windows/opt/ArmCompilerforEmbedded6.21 for Linux                                                                     | – toolchain mdk          |

| Zephyr                 | ZEPHYR_S1            | c:\NXP\zephyr-sdk-<version> for windows/opt/zephyr-sdk-<version> for Linux                                                                             | – toolchain zephyr       |

| CodeWarrior            | CW_DIR               | C:\Freescale\CW MCU v11.2 for windowsCodeWarrior is not supported with Linux                                                                           | – toolchain code-warrior |

| Xtensa                 | XCC_DIR              | C:\xtensa\XtDevTools\install\tools\RI-2023.11-win32\XtensaTools for windows/opt/xtensa/XtDevTools/install/tools/RI-2023.11-Linux/XtensaTools for Linux | – toolchain xtensa       |

| NXP RISC-V S32Compiler | RISCV-LVM_DIR        | C:\riscv-llvm-win32_b298_b298_2024.08.12 for Windows/opt/riscv-llvm-Linux-x64_b298_b298_2024.08.12 for Linux                                           | – toolchain riscv-lvm    |

- The <toolchain>\_DIR is the root installation folder, not the binary location folder. For IAR, it is directory containing following installation folders:

-  arm

-  common

-  install-info

- MDK IDE using armclang toolchain only officially supports Windows. In Linux, please directly use armclang toolchain by setting ARMCLANG\_DIR. In Windows, since most Keil users will install MDK IDE instead of standalone armclang toolchain, the MDK\_DIR has higher priority than ARMCLANG\_DIR.

- For Xtensa toolchain, please set the XTENSA\_CORE environment variable. Here's an example list:

| Device Core      | XTENSA_CORE              |

|------------------|--------------------------|

| RT500 fusion1    | nxp_rt500_RI23_11_newlib |

| RT600 hifi4      | nxp_rt600_RI23_11_newlib |

| RT700 hifi1      | rt700_hifi1_RI23_11_nlib |

| RT700 hifi4      | t700_hifi4_RI23_11_nlib  |

| i.MX8ULP fusion1 | fusion_nxp02_dsp_prod    |

- In Windows, the short path is used in environment variables. If any toolchain is using the long path, you can open a command window from the toolchain folder and use below command to get the short path: for %i in (.) do echo %~fsi

**Tool installation check** Once installed, open a terminal or command prompt and type the associated command to verify the installation.

If you see the version number, you have successfully installed the tool. Else, check whether the tool's installation path is added into the PATH variable. You can add the installation path to the PATH with the commands below:

- Windows: Open command prompt or powershell, run below command to show the user PATH variable.

```

reg query HKEY_CURRENT_USER\Environment /v PATH

```

The tool installation path should be C:\Users\xxx\AppData\Local\Programs\Git\cmd. If the path is not seen in the output from above, append the path value to the PATH variable with the command below:

```

reg add HKEY_CURRENT_USER\Environment /v PATH /d "%PATH%;C:\Users\xxx\AppData\Local\Programs\Git\cmd"

```

Then close the command prompt or powershell and verify the tool command again.

- Linux:

1. Open the \$HOME/.bashrc file using a text editor, such as vim.

2. Go to the end of the file.

3. Add the line which appends the tool installation path to the PATH variable and export PATH at the end of the file. For example, export PATH="/Directory1:\$PATH".

4. Save and exit.

5. Execute the script with source .bashrc or reboot the system to make the changes live. To verify the changes, run echo \$PATH.

- macOS:

1. Open the \$HOME/.bash\_profile file using a text editor, such as nano.

2. Go to the end of the file.

3. Add the line which appends the tool installation path to the PATH variable and export PATH at the end of the file. For example, export PATH="/Directory1:\$PATH".

4. Save and exit.

5. Execute the script with source .bash\_profile or reboot the system to make the changes live. To verify the changes, run echo \$PATH.

## Get MCUXpresso SDK Repo

**Establish SDK Workspace** To get the MCUXpresso SDK repository, use the west tool to clone the manifest repository and checkout all the west projects.

```

# Initialize west with the manifest repository

west init -m https://github.com/nxp-mcuxpresso/mcuxsdk-manifests/ mcuxpresso-sdk

# Update the west projects

cd mcuxpresso-sdk

west update

# Allow the usage of west extensions provided by MCUXpresso SDK

west config commands.allow_extensions true

```

**Install Python Dependency(If do tool installation manually)** To create a Python virtual environment in the west workspace core repo directory mcuxsdk, follow these steps:

1. Navigate to the core directory:

```

cd mcuxsdk

```

2. [Optional] Create and activate the virtual environment: If you don't want to use the python virtual environment, skip this step. **We strongly suggest you use venv to avoid conflicts with other projects using python.**

```

python -m venv .venv

# For Linux/MacOS

source .venv/bin/activate

# For Windows

.\venv\Scripts\activate

# If you are using powershell and see the issue that the activate script cannot be run.

# You may fix the issue by opening the powershell as administrator and run below command:

powershell Set-ExecutionPolicy RemoteSigned

# then run above activate command again.

```

Once activated, your shell will be prefixed with (.venv). The virtual environment can be deactivated at any time by running deactivate command.

**Remember to activate the virtual environment every time you start working in this directory.** If you are using some modern shell like zsh, there are some powerful plugins to help you auto switch venv among workspaces. For example, `zsh-autoswitch-virtualenv`.

3. Install the required Python packages:

```

# Note: you can add option '--default-timeout=1000' if you meet connection issue. Or you may set a

# different source using option '-i'.

# for example, in China you could try: pip3 install -r mcuxsdk/scripts/requirements.txt -i https://pypi.

# tuna.tsinghua.edu.cn/simple

pip install -r scripts/requirements.txt

```

## Explore Contents

This section helps you build basic understanding of current fundamental project content and guides you how to build and run the provided example project in whole SDK delivery.

**Folder View** The whole MCUXpresso SDK project, after you have done the west init and west update operations follow the guideline at [Getting Started Guide](#), have below folder structure:

| Folder    | Description                                                                            |

|-----------|----------------------------------------------------------------------------------------|

| manifests | Manifest repo, contains the manifest file to initialize and update the west workspace. |

| mcuxsdk   | The MCUXpresso SDK source code, examples, middleware integration and script files.     |

All the projects record in the [Manifest repo](#) are checked out to the folder mcuxsdk/, the layout of mcuxsdk folder is shown as below:

| Folder     | Description                                                                                                                                                                                   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arch       | Arch related files such as ARM CMSIS core files, RISC-V files and the build files related to the architecture.                                                                                |

| cmake      | The cmake modules, files which organize the build system.                                                                                                                                     |

| components | Software components.                                                                                                                                                                          |

| devices    | Device support package which categorized by device series. For each device, header file, feature file, startup file and linker files are provided, also device specific drivers are included. |

| docs       | Documentation source and build configuration for this sphinx built online documentation.                                                                                                      |

| drivers    | Peripheral drivers.                                                                                                                                                                           |

| examples   | Various demos and examples, support files on different supported boards. For each board support, there are board configuration files.                                                         |

| middleware | Middleware components integrated into SDK.                                                                                                                                                    |

| rtos       | Rtos components integrated into SDK.                                                                                                                                                          |

| scripts    | Script files for the west extension command and build system support.                                                                                                                         |

| svd        | Svd files for devices, this is optional because of large size. Customers run west manifest config group.filter +optional and west update mcux-soc-svd to get this folder.                     |

**Examples Project** The examples project is part of the whole SDK delivery, and locates in the folder mcuxsdk/examples of west workspace.

Examples files are placed in folder of <example\_category>, these examples include (but are not limited to)

- demo\_apps: Basic demo set to start using SDK, including hello\_world and led\_blinky.

- driver\_examples: Simple applications that show how to use the peripheral drivers for a single use case. These applications typically only use a single peripheral but there are cases where multiple peripherals are used (for example, SPI transfer using DMA).

Board porting layers are placed in folder of \_boards/<board\_name> which aims at providing the board specific parts for examples code mentioned above.

## Run a demo using MCUXpresso for VS Code

This section explains how to configure MCUXpresso for VS Code to build, run, and debug example applications. This guide uses the hello\_world demo application as an example. However, these

steps can be applied to any example application in the MCUXpresso SDK.

**Build an example application** This section assumes that the user has already obtained the SDK as outlined in [Get MCUXpresso SDK Repo](#).

To build an example application:

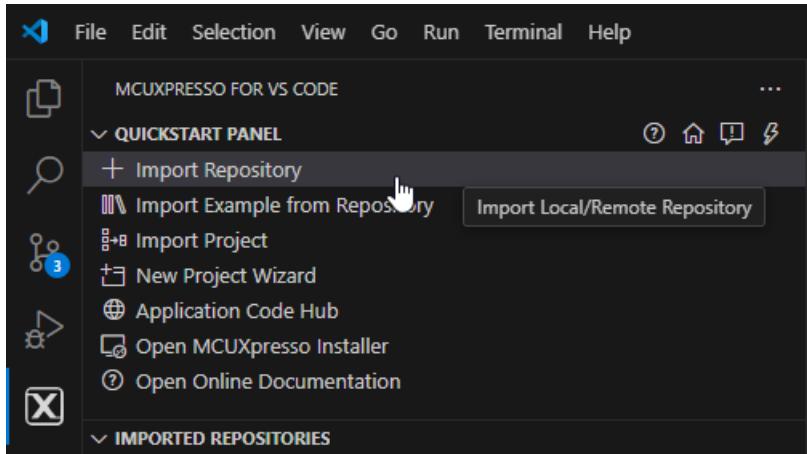

1. Import the SDK into your workspace. Click **Import Repository** from the **QUICKSTART PANEL**.

**Note:** You can import the SDK in several ways. Refer to [MCUXpresso for VS Code Wiki](#) for details.

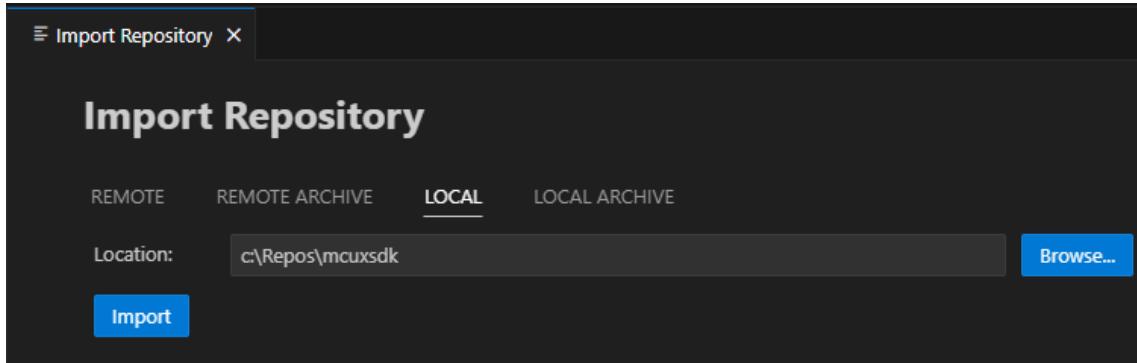

Select **Local** if you've already obtained the SDK as seen in [Get MCUXpresso SDK Repo](#). Select your location and click **Import**.

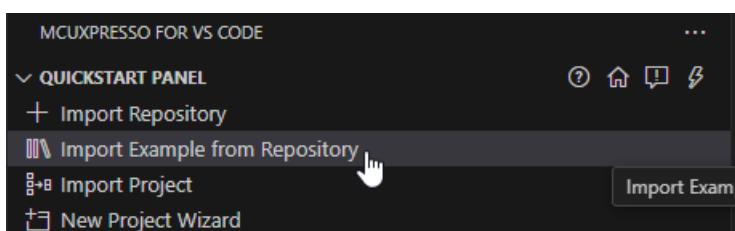

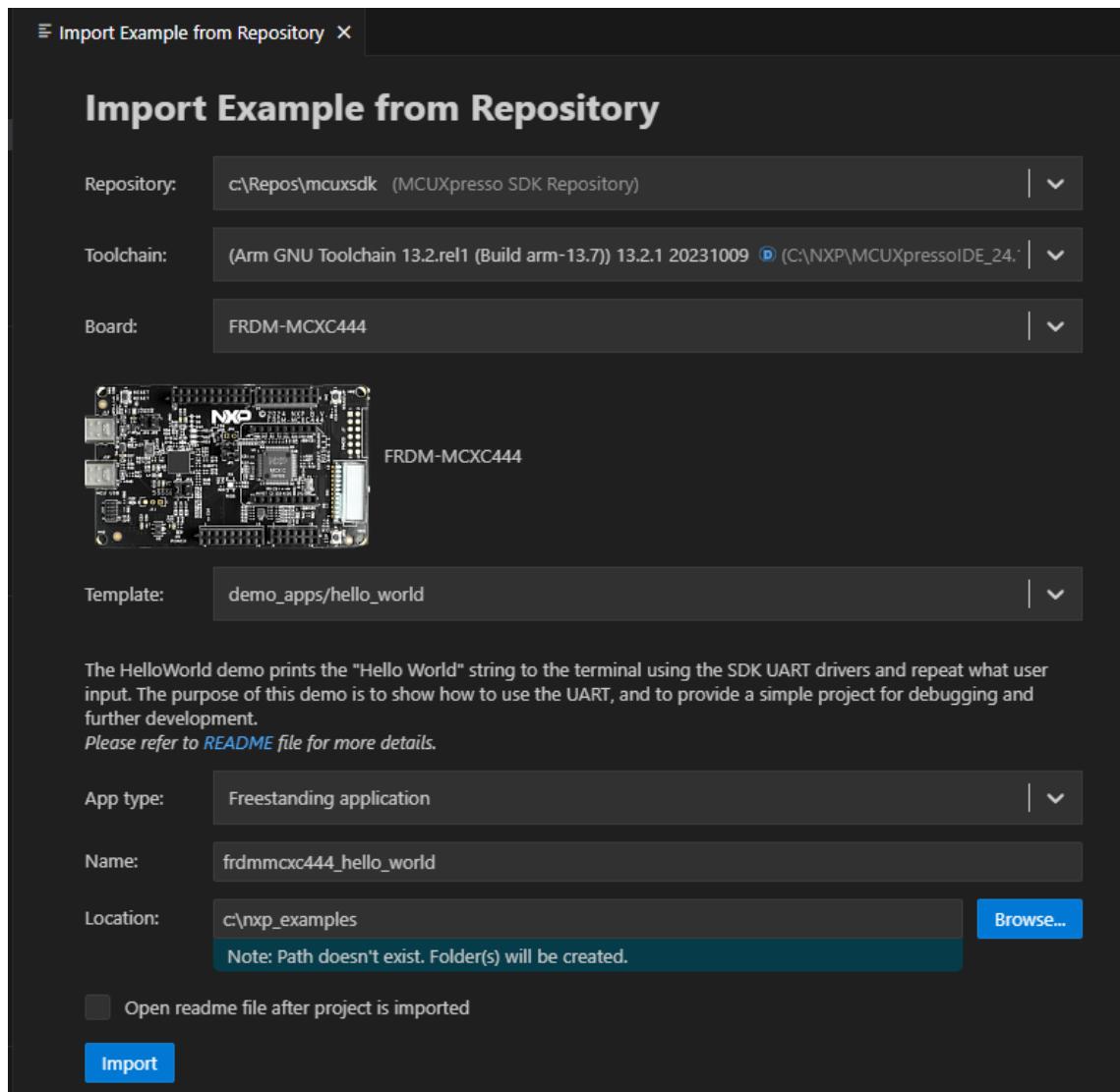

2. Click **Import Example from Repository** from the **QUICKSTART PANEL**.

In the dropdown menu, select the MCUXpresso SDK, the Arm GNU Toolchain, your board, template, and application type. Click **Import**.

**Note:** The MCUXpresso SDK projects can be imported as **Repository applications** or **Free-standing applications**. The difference between the two is the import location. Projects imported as Repository examples will be located inside the MCUXpresso SDK, whereas Free-standing examples can be imported to a user-defined location. Select between these by designating your selection in the **App type** dropdown menu.

3. VS Code will prompt you to confirm if the imported files are trusted. Click **Yes**.

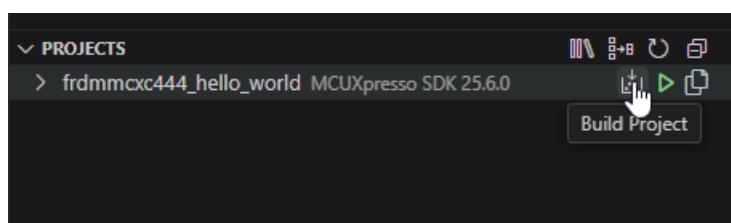

4. Navigate to the **PROJECTS** view. Find your project and click the **Build Project** icon.

The integrated terminal will open at the bottom and will display the build output.

```

[17/21] Building C object CMakeFiles/hello_world.dir/C_/Repos/mcux-sdk/mcux-sdk/components/debug_console_lite/fsl_debug_console.c.obj

[18/21] Building C object CMakeFiles/hello_world.dir/C_/Repos/mcux-sdk/mcux-sdk/devices/MCX/MCX444/drivers/fsl_clock.c.obj

[19/21] Building C object CMakeFiles/hello_world.dir/C_/Repos/mcux-sdk/mcux-sdk/drivers/1puart/fsl_1puart.c.obj

[20/21] Building C object CMakeFiles/hello_world.dir/C_/Repos/mcux-sdk/mcux-sdk/drivers/uart/fsl_uart.c.obj

[21/21] Linking C executable hello_world.elf

Memory region      Used Size  Region Size %age Used

m_interrupts:      192 B      512 B   37.50%

m_flash_config:     16 B       16 B  100.00%

m_text:      7892 B    261104 B   3.02%

m_data:       2128 B      32 KB   6.49%

build finished successfully.

* Terminal will be reused by tasks, press any key to close it.

```

**Run an example application** **Note:** for full details on MCUXpresso for VS Code debug probe support, see [MCUXpresso for VS Code Wiki](#).

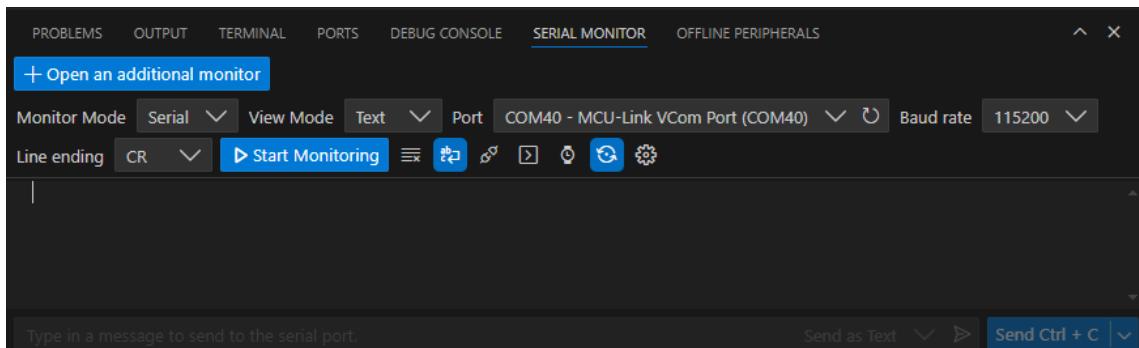

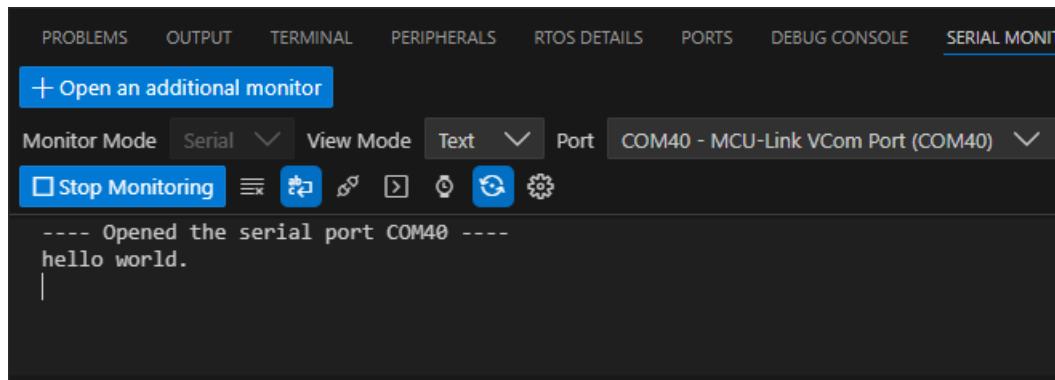

1. Open the **Serial Monitor** from the VS Code's integrated terminal. Select the VCom Port for your device and set the baud rate to 115200.

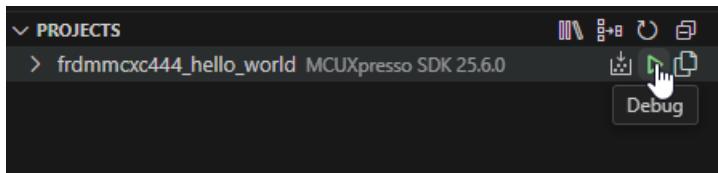

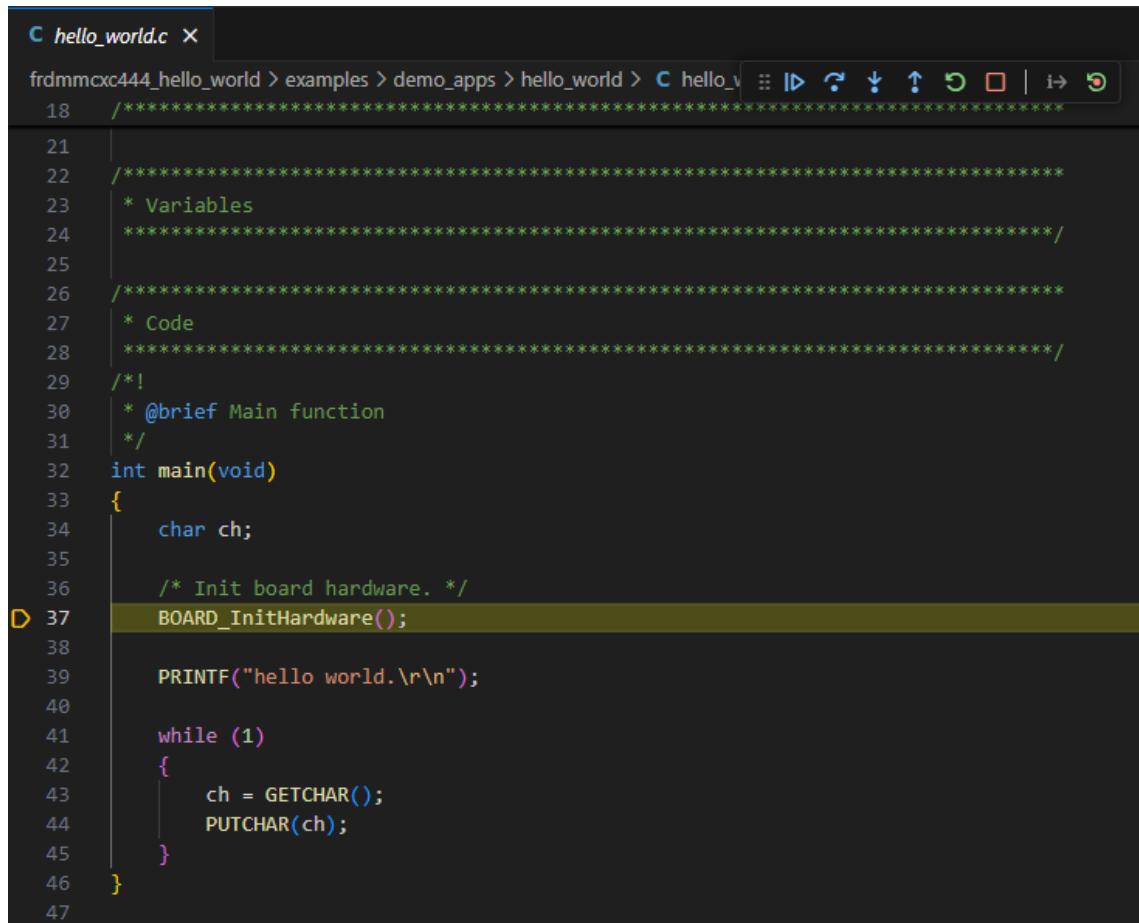

2. Navigate to the **PROJECTS** view and click the play button to initiate a debug session.

The debug session will begin. The debug controls are initially at the top.

```

C hello_world.c ×

frdmmcx444_hello_world > examples > demo_apps > hello_world > C hello_world

18  ****

19

20  ****

21  * Variables

22  ****

23

24  ****

25

26  ****

27  * Code

28  ****

29  */

30  * @brief Main function

31  */

32  int main(void)

33  {

34      char ch;

35

36      /* Init board hardware. */

37      BOARD_InitHardware();

38

39      PRINTF("hello world.\r\n");

40

41      while (1)

42      {

43          ch = GETCHAR();

44          PUTCHAR(ch);

45      }

46  }

47

```

3. Click **Continue** on the debug controls to resume execution of the code. Observe the output on the **Serial Monitor**.

## Running a demo using ARMGCC CLI/IAR/MDK

**Supported Boards** Use the west extension `west list_project` to understand the board support scope for a specified example. All supported build command will be listed in output:

```

west list_project -p examples/demo_apps/hello_world [-t armgcc]

```

```

INFO: [ 1][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b evk9mimx8ulp -Dcore_id=cm33]

INFO: [ 2][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b evkbimxrt1050]

INFO: [ 3][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b

```

(continues on next page)

(continued from previous page)

```

↳ evkbmimxrt1060]

INFO: [ 4][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_

↳ evkbmimxrt1170 -Dcore_id=cm4]

INFO: [ 5][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_

↳ evkbmimxrt1170 -Dcore_id=cm7]

INFO: [ 6][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_

↳ evkcmimxrt1060]

INFO: [ 7][west build -p always examples/demo_apps/hello_world --toolchain armgcc --config release -b_

↳ evkcmimx7ulp]

...

```

The supported toolchains and build targets for an example are decided by the example-self example.yml and board example.yml, please refer Example Toolchains and Targets for more details.

**Build the project** Use west build -h to see help information for west build command. Compared to zephyr's west build, MCUXpresso SDK's west build command provides following additional options for mcux examples:

- --toolchain: specify the toolchain for this build, default armgcc.

- --config: value for CMAKE\_BUILD\_TYPE. If not provided, build system will get all the example supported build targets and use the first debug target as the default one. Please refer Example Toolchains and Targets for more details about example supported build targets.

Here are some typical usages for generating a SDK example:

```

# Generate example with default settings, default used device is the mainset MK22F51212

west build -b frdmk22f examples/demo_apps/hello_world

# Just print cmake commands, do not execute it

west build -b frdmk22f examples/demo_apps/hello_world --dry-run

# Generate example with other toolchain like iar, default armgcc

west build -b frdmk22f examples/demo_apps/hello_world --toolchain iar

# Generate example with other config type

west build -b frdmk22f examples/demo_apps/hello_world --config release

# Generate example with other devices with --device

west build -b frdmk22f examples/demo_apps/hello_world --device MK22F12810 --config release

```

For multicore devices, you shall specify the corresponding core id by passing the command line argument -Dcore\_id. For example

```

west build -b evkbmimxrt1170 examples/demo_apps/hello_world --toolchain iar -Dcore_id=cm7 --config_

↳ flexspi_nor_debug

```

For shield, please use the --shield to specify the shield to run, like

```

west build -b mimxrt700evk --shield a8974 examples/issdk_examples/sensors/fxls8974cf/fxls8974cf_poll -

↳ Dcore_id=cm33_core0

```

**Sysbuild(System build)** To support multicore project building, we ported Sysbuild from Zephyr. It supports combine multiple projects for compilation. You can build all projects by adding --sysbuild for main application. For example:

```

west build -b evkbmimxrt1170 --sysbuild ./examples/multicore_examples/hello_world/primary -Dcore_

↳ id=cm7 --config flexspi_nor_debug --toolchain=armgcc -p always

```

For more details, please refer to System build.

**Config a Project** Example in MCUXpresso SDK is configured and tested with pre-defined configuration. You can follow steps blow to change the configuration.

1. Run cmake configuration

```

west build -b evkbmimxrt1170 examples/demo_apps/hello_world -Dcore_id=cm7 --cmake-only -p

```

Please note the project will be built without --cmake-only parameter.

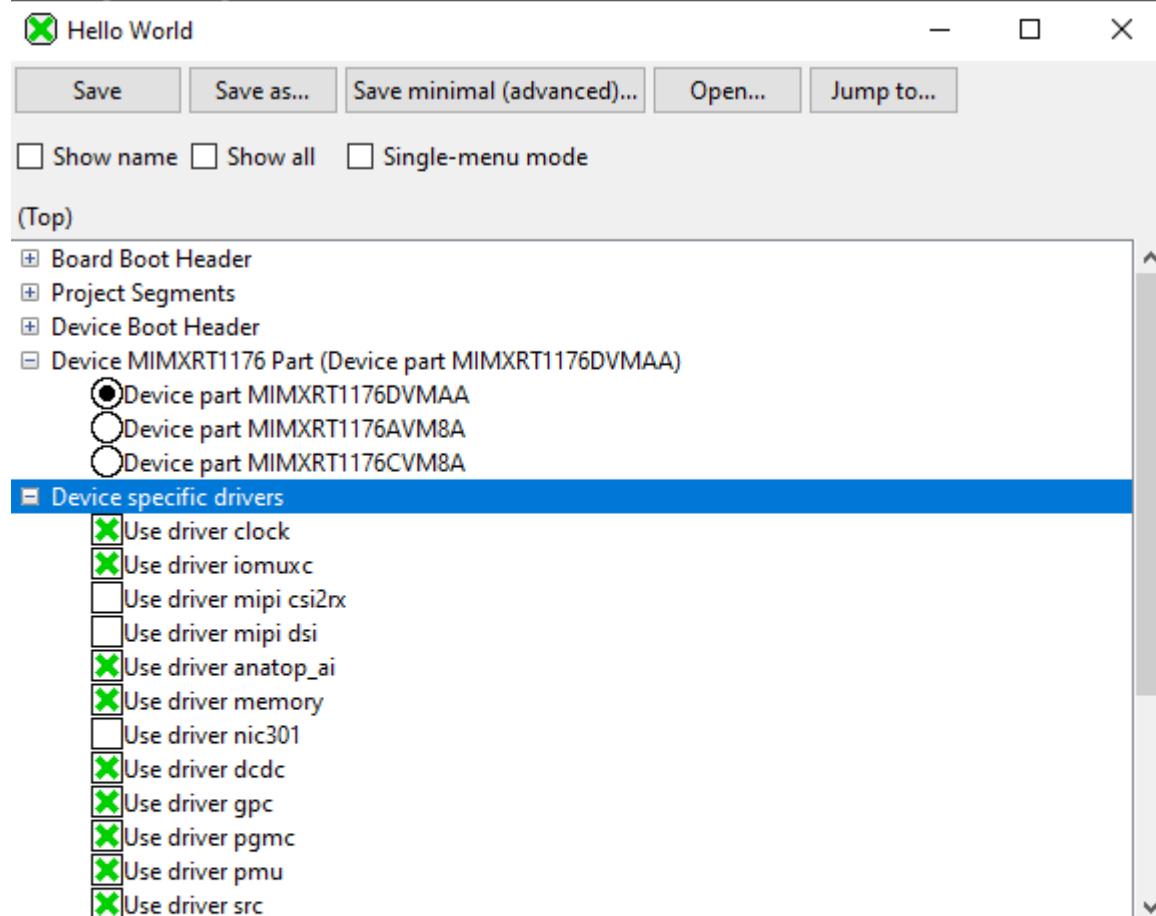

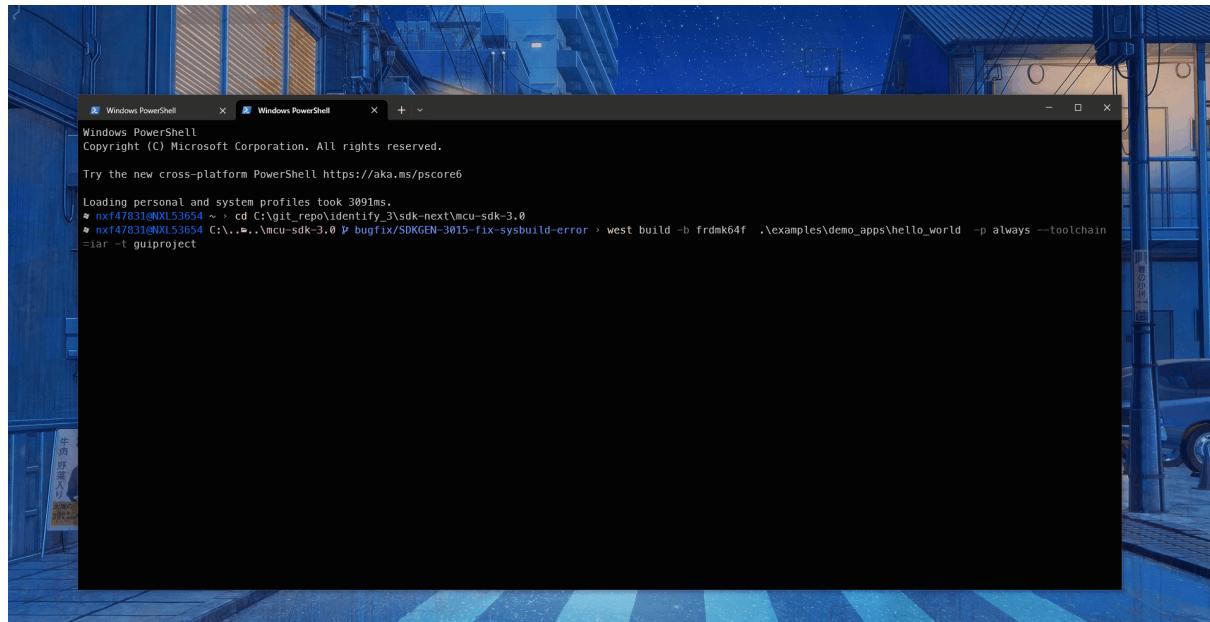

2. Run guiconfig target

```

west build -t guiconfig

```

Then you will get the Kconfig GUI launched, like

```

Kconfig definition, with parent deps. propagated to 'depends on'

=====

```

```

At D:/sdk_next/mcux-sdk/devices/../devices/RT/RT1170/MIMXRT1176/drivers/Kconfig:5

Included via D:/sdk_next/mcux-sdk/examples/demo_apps/hello_world/Kconfig:6 ->

D:/sdk_next/mcux-sdk/Kconfig.mcuxpresso:9 -> D:/sdk_next/mcux-sdk/devices/Kconfig:1

-> D:/sdk_next/mcux-sdk/devices/../devices/RT/RT1170/MIMXRT1176/Kconfig:8

Menu path: (Top)

```

```

menu "Device specific drivers"

```

You can reconfigure the project by selecting/deselecting Kconfig options.

After saving and closing the Kconfig GUI, you can directly run west build to build with the new configuration.

**Flash Note:** Please refer Flash and Debug The Example to enable west flash/debug support.

Flash the hello\_world example:

```

west flash -r linkserver

```

**Debug** Start a gdb interface by following command:

```

west debug -r linkserver

```

**Work with IDE Project** The above build functionalities are all with CLI. If you want to use the toolchain IDE to work to enjoy the better user experience especially for debugging or you are already used to develop with IDEs like IAR, MDK, Xtensa and CodeWarrior in the embedded world, you can play with our IDE project generation functionality.

This is the cmd to generate the evkbmimxrt1170 hello\_world IAR IDE project files.

```

west build -b evkbmimxrt1170 examples/demo_apps/hello_world --toolchain iar -Dcore_id=cm7 --config ↵

↵flexspi_nor_debug -p always -t guiproject

```

By default, the IDE project files are generated in mcux-sdk/build/<toolchain> folder, you can open the project file with the IDE tool to work:

Note, please follow the [Installation](#) to setup the environment especially make sure that `ruby` has been installed.

## 1.2.2 How to determine COM Port

This section describes the steps necessary to determine the debug COM port number of your NXP hardware development platform. All NXP boards ship with a factory programmed, on-board debug interface MCU-LINK.

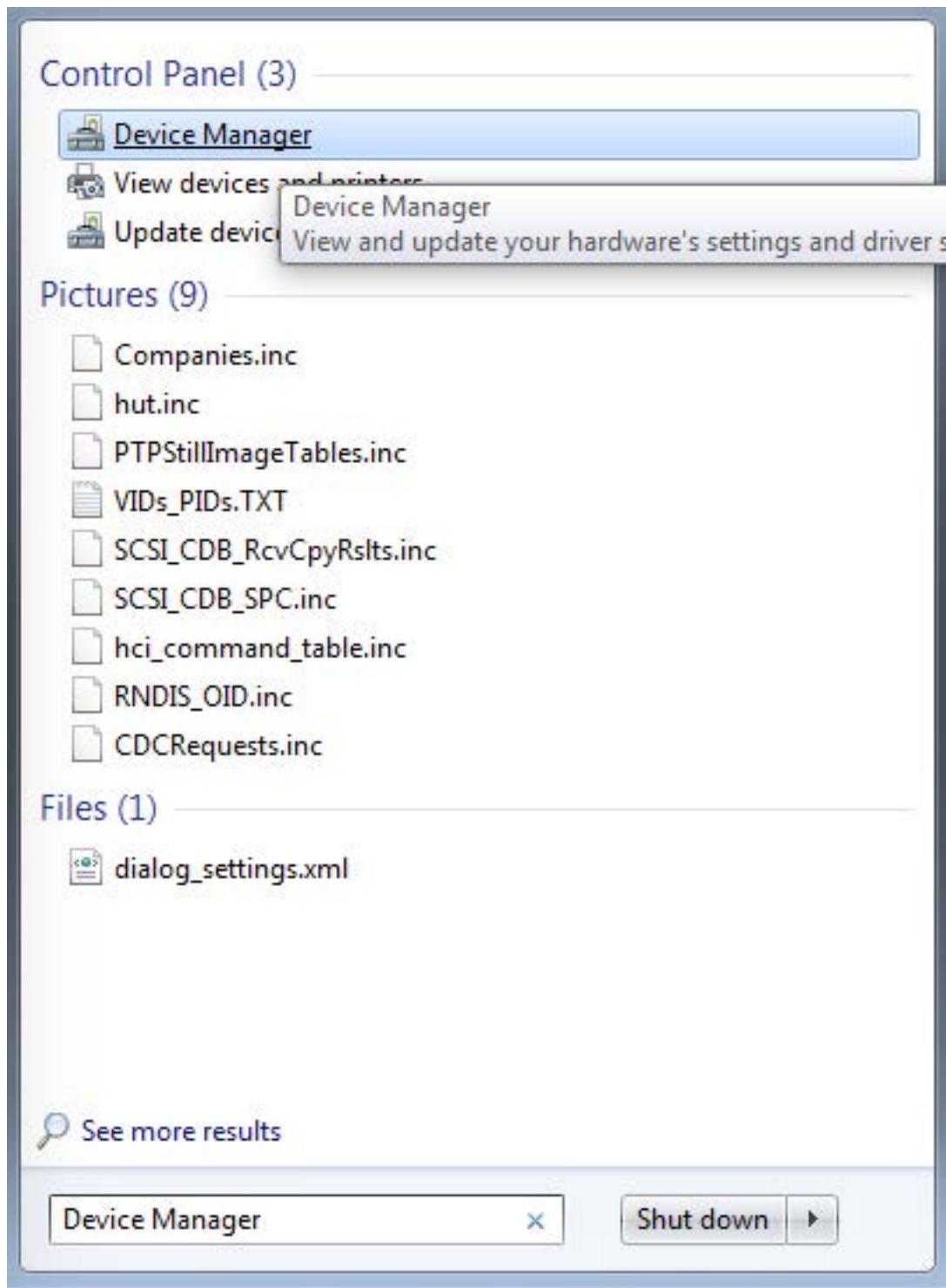

1. To determine the COM port, open the Windows operating system **Device Manager**. This can be achieved by going to the Windows operating system **Start** menu and typing **Device Manager** in the search bar, as shown in *Figure 1*.

2. In the **Device Manager**, expand the **Ports (COM & LPT)** section to view the available ports.

### 1.2.3 Updating debugger firmware

The MCXW23-EVK board comes with a CMSIS-DAP-compatible debug interface (known as MCULink). This firmware in this debug interface may be updated using the host computer scripts. This is typically used when switching between the default debugger protocol (CMSIS-DAP) to SEGGER J-Link, or for updating this firmware with new releases of these. This section contains the steps to re-program the debug probe firmware.

NXP provides the MCU-Link utility, which is the recommended tool for programming the latest versions of CMSIS-DAP and J-Link firmware onto MCU-Link. The utility can be downloaded from <https://www.nxp.com/design/microcontrollers-developer-resources/mcu-link-debug-probe:MCU-LINK>.

These steps show how to update the debugger firmware on your board for Windows operating system. For Linux OS, follow the instructions described in MCU-Link user guide, <https://www.nxp.com/design/software/development-software/mcuxpresso-software-and-tools/mcu-link-debug-probe:MCU-LINK>.

1. Install the MCU-Link utility.

2. Unplug the board's USB cable.

3. Install the jumper on J32.

4. Connect the probe to the host via USB (use Link USB connector).

5. Open a command shell and call the appropriate script located in the MCU-Link installation directory, *<MCU-Link install dir>.\**

1. To program CMSIS-DAP debug firmware: *<MCU-Link install dir>/scripts/program\_CMSIS*.

2. To program J-Link debug firmware: *<MCU-Link install dir>/scripts/program\_JLINK*.

6. Remove the jumper on J32.

7. Re-power the board by removing the USB cable and plugging it in again.

## 1.3 Release Notes

**This is an Ready For Production Release (RFP) for MCXW23-EVK development board.**

### 1.3.1 MCUXpresso SDK Release Notes

#### Overview

The MCUXpresso SDK is a comprehensive software enablement package designed to simplify and accelerate application development with Arm Cortex-M-based devices from NXP, including its general purpose, crossover and Bluetooth-enabled MCUs. MCUXpresso SW and Tools for DSC further extends the SDK support to current 32-bit Digital Signal Controllers. The MCUXpresso SDK includes production-grade software with integrated RTOS (optional), integrated enabling software technologies (stacks and middleware), reference software, and more.

In addition to working seamlessly with the MCUXpresso IDE, the MCUXpresso SDK also supports and provides example projects for various toolchains. The Development tools chapter in the associated Release Notes provides details about toolchain support for your board. Support for the MCUXpresso Config Tools allows easy cloning of existing SDK examples and demos, allowing users to leverage the existing software examples provided by the SDK for their own projects.

Underscoring our commitment to high quality, the MCUXpresso SDK is MISRA compliant and checked with Coverity static analysis tools. For details on MCUXpresso SDK, see [MCUXpresso-SDK: Software Development Kit for MCUXpresso](#).

#### MCUXpresso SDK

As part of the MCUXpresso software and tools, MCUXpresso SDK is the evolution of Kinetis SDK, includes support for LPC, DSC, PN76, and i.MX System-on-Chip (SoC). The same drivers, APIs, and

middleware are still available with support for Kinetis, LPC, DSC, and i.MX silicon. The MCUXpresso SDK adds support for the MCUXpresso IDE, an Eclipse-based toolchain that works with all MCUXpresso SDKs. Easily import your SDK into the new toolchain to access to all of the available components, examples, and demos for your target silicon. In addition to the MCUXpresso IDE, support for the MCUXpresso Config Tools allows easy cloning of existing SDK examples and demos, allowing users to leverage the existing software examples provided by the SDK for their own projects.

In order to maintain compatibility with legacy Freescale code, the filenames and source code in MCUXpresso SDK containing the legacy Freescale prefix FSL has been left as is. The FSL prefix has been redefined as the NXP Foundation Software Library.

## Development tools

The MCUXpresso SDK was tested with following development tools. Same versions or above are recommended.

**Currently, the new MCX W23 product does not natively support the IAR toolchain. This patch provides all the required files to your IAR Embedded Workbench installation, enabling you to build and debug MCX W23 SDK projects in the IDE. The following patch has been tested with IAR Embedded Workbench v9.60.4. IAR patch is distributed via <https://mcuxpresso.nxp.com>. Download the archive file `iar_support_patch_mcxw23x_25_09_00.zip`. Then, unzip the file and copy the content into your IAR folder structure (typically within `C:/Program Files/IAR systems`).**

- IAR Embedded Workbench for Arm, version is 9.60.4

- Keil MDK, version is 5.42

- MCUXpresso for VS Code v25.09

- GCC Arm Embedded Toolchain 14.2.x

## Supported development systems

This release supports board and devices listed in following table. The board and devices in bold were tested in this release.

|                    |                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Development boards | MCU devices                                                                                                                    |

| <b>MCXW23-EVK</b>  | MCXW235AIHNAR, MCXW235AIUKAR, MCXW235BIHNAR, MCXW235BIUKAR, MCXW236AIHNAR, MCXW236AIUKAR, <b>MCXW236BIHNAR</b> , MCXW236BIUKAR |

## MCUXpresso SDK release package

The MCUXpresso SDK release package content is aligned with the silicon subfamily it supports. This includes the boards, CMSIS, devices, middleware, and RTOS support.

**Device support** The device folder contains the whole software enablement available for the specific System-on-Chip (SoC) subfamily. This folder includes clock-specific implementation, device register header files, device register feature header files, and the system configuration source files. Included with the standard SoC support are folders containing peripheral drivers, toolchain support, and a standard debug console. The device-specific header files provide a direct access to the microcontroller peripheral registers. The device header file provides an overall

SoC memory mapped register definition. The folder also includes the feature header file for each peripheral on the microcontroller. The toolchain folder contains the startup code and linker files for each supported toolchain. The startup code efficiently transfers the code execution to the main() function.

**Board support** The boards folder provides the board-specific demo applications, driver examples, and middleware examples.

**Demo application and other examples** The demo applications demonstrate the usage of the peripheral drivers to achieve a system level solution. Each demo application contains a readme file that describes the operation of the demo and required setup steps. The driver examples demonstrate the capabilities of the peripheral drivers. Each example implements a common use case to help demonstrate the driver functionality.

## RTOS

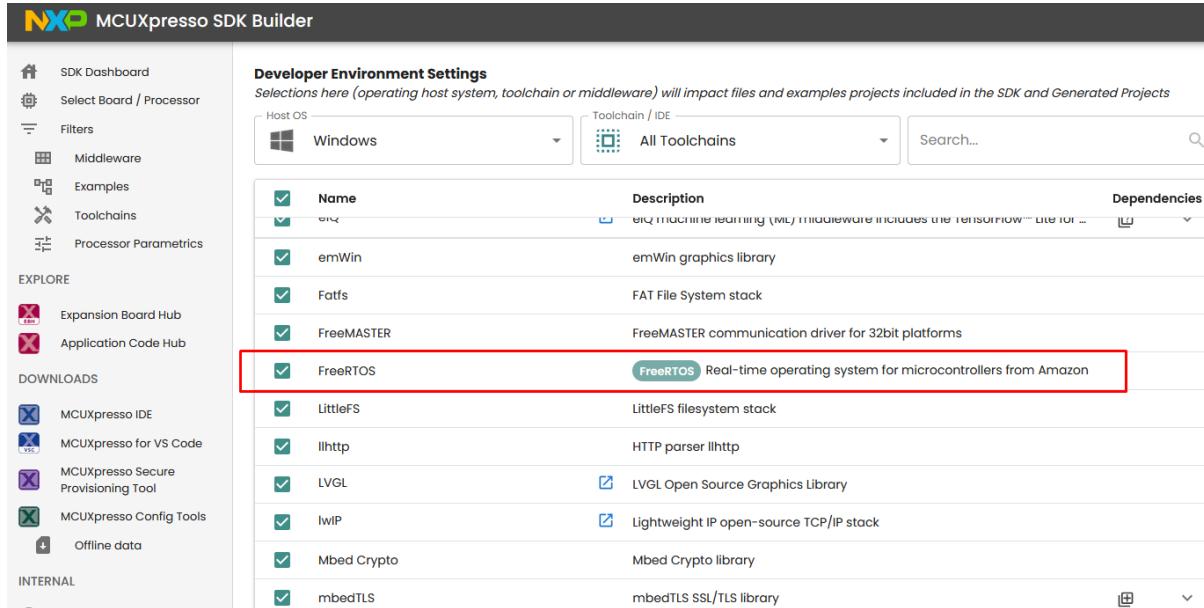

**FreeRTOS** Real-time operating system for microcontrollers from Amazon

## Middleware

**CMSIS DSP Library** The MCUXpresso SDK is shipped with the standard CMSIS development pack, including the prebuilt libraries.

**mbedTLS** mbedtls SSL/TLS library v3.x

**TF-M** Trusted Firmware - M Library

**PSA Test Suite** Arm Platform Security Architecture Test Suite

**Wireless Bluetooth LE host stack and applications** The Bluetooth LE Host Stack component provides an implementation for a Bluetooth LE mandatory and some optional, proprietary, and experimental features. The Bluetooth LE Host Stack component provides application examples, services, and profiles.

Main features supported:

- Automotive Compliance

- MISRA Compliance

- HIS CCM <= 20

- Advanced Secure Mode

- Enhanced ATT

- GATT Caching

- Bluetooth LE Host GCC Libraries

- Bluetooth LE Host IAR Libraries

- Bluetooth LE Host Peripheral Libraries

- Bluetooth LE Central Libraries

- Bluetooth LE Host Full Host Features Libraries

- Bluetooth LE Host Optional Features Libraries

- Bluetooth LE Host Mandatory Features Libraries

- Bare-metal and FreeRTOS Support

- Bluetooth LE Privacy Support

- CCC Sample Applications

- Enhanced Notifications

- Dynamic Database

- OTA Support - Sample Applications

- Decision based Advertising Filtering (DBAF) - Experimental feature

- Advertising Coding Selection (ACS) - Experimental feature

- Channel Sounding - Experimental feature with controlled access (contact your NXP representative for access)

- Bluetooth LE Controller main and experimental features and capabilities described below are supported by the Bluetooth LE Host.

**Note:** For evaluating DBAF and ACS experimental features, replace the Bluetooth LE Host default example projects libraries with the libraries from the *SDK* folder *..|middleware|wireless|bluetooth|host|lib\_exp* and enable the features in the application. The Radio Subsystem (NBU) Firmware with experimental features is required.

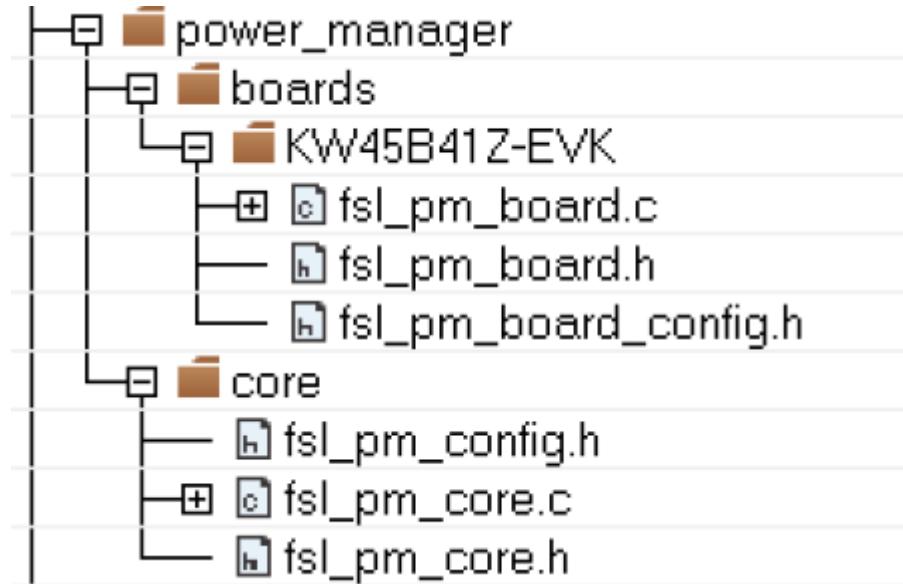

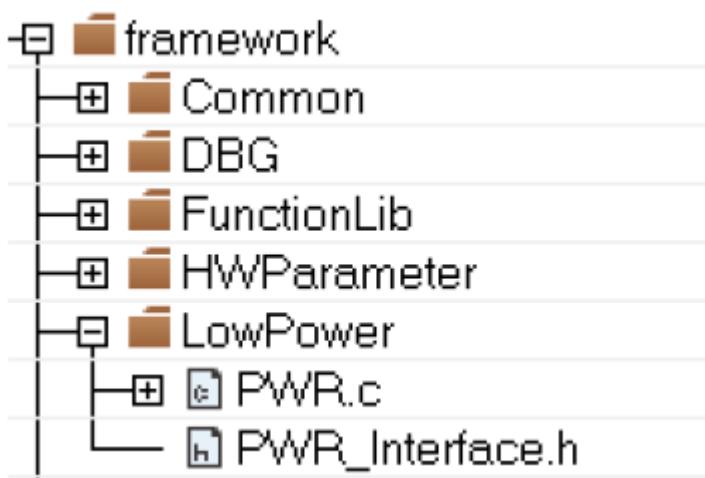

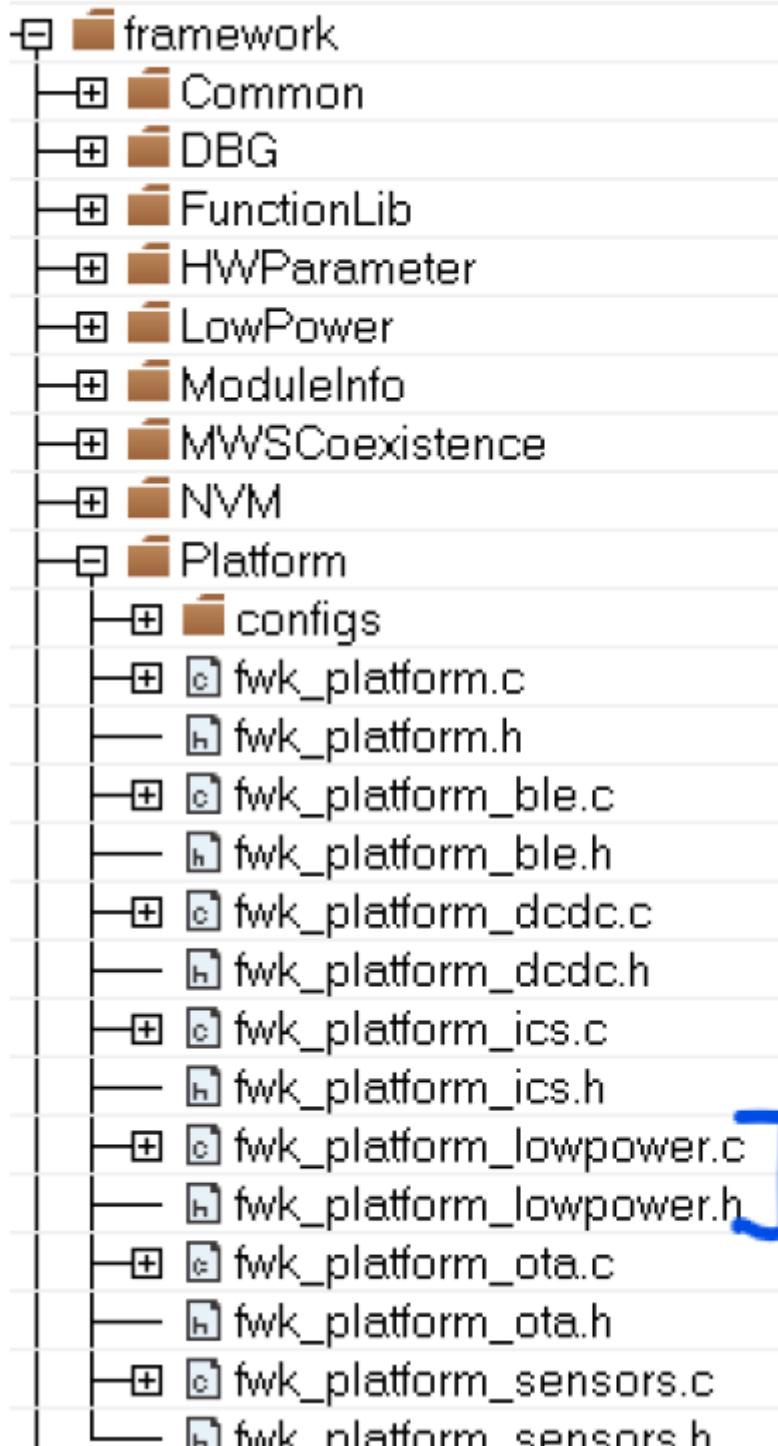

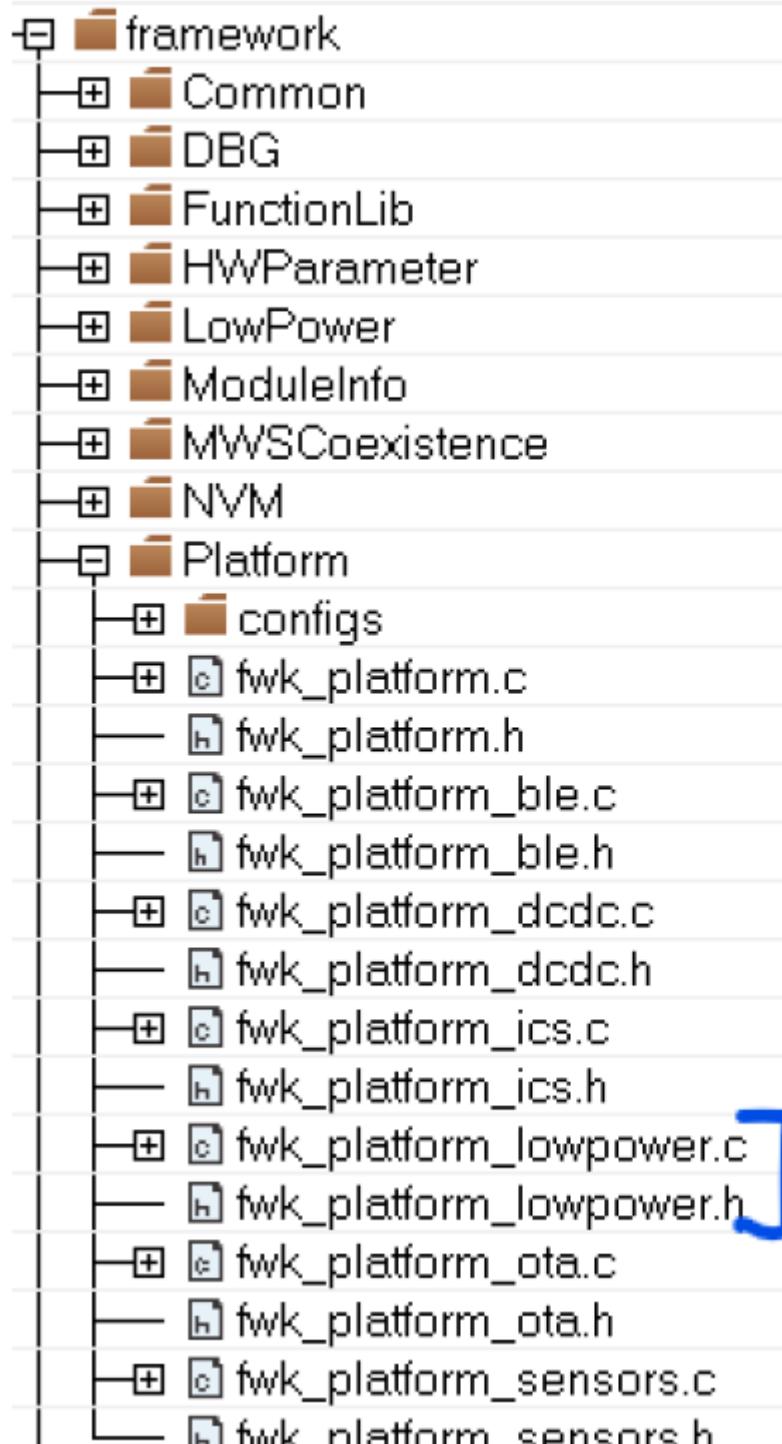

**Wireless Connectivity Framework** The Connectivity Framework is a software component that provides hardware abstraction modules to the upper layer connectivity stacks and components. It also provides a list of services and APIs, such as, Low power, Over the Air (OTA) Firmware update, File System, Security, Sensors, Serial Connectivity Interface (FSCI), and others. The Connectivity Framework modules are located in the *middleware|wireless|framework* *SDK* folder.

### Bluetooth Synopsys Controller

- Main features supported:

- All roles that the Bluetooth specification specifies:

- \* Broadcaster

- \* Observer

- \* Peripheral

- \* Central

- Up to 4 simultaneous connections supported

- Bluetooth Low Energy features:

- \* Device privacy and network privacy modes (version 5.0)

- \* Advertising extension PDUs (version 5.0)

- \* Anonymous device address type (version 5.0)

- \* Up to 2 Mbps data rate (version 5.0)

- \* Long range (version 5.0)

- \* High-duty cycle, nonconnectable advertising (version 5.0)

- \* Channel selection algorithm #2 (version 5.0)

- \* High output power (version 5.0)

- \* Advertising channel index (version 5.1)

- \* Periodic advertising sync transfer (PAST) (version 5.1)

- \* Supports LE power control feature (version 5.2)

- Device filtering through programmable size white lists

- Direct test mode

- RF antenna: 50 Ω single-ended

- RF receiver characteristics:

- \* Sensitivity -94 dBm in Bluetooth Low Energy 2 Mbps

- \* Sensitivity -97 dBm in Bluetooth Low Energy 1 Mbps

- \* Sensitivity -100 dBm in Bluetooth Low Energy 500 kbps

- \* Sensitivity -102 dBm in Bluetooth Low Energy 125 kbps

- \* Accurate RSSI measurement with ±3 dB accuracy

- Flexible RF transmitter level configurability:

- \* TX mode 1 (TXM1): Range from -31 dBm to +2 dBm when VDD\_RF exceeds 1.1 V

- \* TX mode 2 (TXM2): Range from -28 dBm to +6 dBm when VDD\_RF exceeds 1.7 V

## LittleFS LittleFS filesystem stack

### Release contents

Provides an overview of the MCUXpresso SDK release package contents and locations.

| Deliverable                                                                          | Location                                           |

|--------------------------------------------------------------------------------------|----------------------------------------------------|

| Boards                                                                               | INSTALL_DIR/boards                                 |

| Demo Applications                                                                    | INSTALL_DIR/boards/<board_name>/demo_apps          |

| Driver Examples                                                                      | INSTALL_DIR/boards/<board_name>/driver_examples    |

| eIQ examples                                                                         | INSTALL_DIR/boards/<board_name>/eiq_examples       |

| Board Project Template for MCUXpresso IDE NPW                                        | INSTALL_DIR/boards/<board_name>/project_template   |

| Driver, SoC header files, extension header files and feature header files, utilities | INSTALL_DIR/devices/<device_name>                  |

| CMSIS drivers                                                                        | INSTALL_DIR/devices/<device_name>/cmsis_drivers    |

| Peripheral drivers                                                                   | INSTALL_DIR/devices/<device_name>/drivers          |

| Toolchain linker files and startup code                                              | INSTALL_DIR/devices/<device_name>/<toolchain_name> |

| Utilities such as debug console                                                      | INSTALL_DIR/devices/<device_name>/utilities        |

| Device Project Template for MCUXpresso IDE NPW                                       | INSTALL_DIR/devices/<device_name>/project_template |

| CMSIS Arm Cortex-M header files, DSP library source                                  | INSTALL_DIR/CMSIS                                  |

| Components and board device drivers                                                  | INSTALL_DIR/components                             |

| RTOS                                                                                 | INSTALL_DIR/rtos                                   |

| Release Notes, Getting Started Document and other documents                          | INSTALL_DIR/docs                                   |

| Tools such as shared cmake files                                                     | INSTALL_DIR/tools                                  |

| Middleware                                                                           | INSTALL_DIR/middleware                             |

## What is new

The following changes have been implemented compared to the previous SDK release version (25.06.00).

- **Bluetooth Synopsys controller**

- LE ping stops after feature exchange.

- Connection drops as central after Connection Update from the slave.

- Fixed state not correctly reset when terminating periodic advertising sync leading to hard fault.

- Tx power is not changed in the database when the Tx power table changes.

- Provide API to enable/disable Channel Assessment.

- Debug HCI: Fix missed deferred HCI event logs.

- Disable checking irq priorities against unused BLE\_SLP\_TMR\_IRQ.

- Fixed the wrong Local Resolvable Private Address in the LE Enhanced Connection Complete event.

- **Bluetooth LE**

- **Common changes**

- \* Support for **IAR toolchain** added.

- \* Support for the **MCXW235B SoC variant** added.

- \* **SRAM placement updated** - data placement now starts at 0x20004000 instead of 0x20008000.

- \* **NVM storage integration improved** - NVM operations are now performed when the radio is not active for enough time

- \* **Experimental** support of mebdtls PSA. The feature can be enabled for **testing** purpose by setting `CONFIG_MCUX_COMPONENT_middleware.wireless.framework.seclib_rng_port.psa=y`, `CONFIG_MCUX_COMPONENT_component.psa_crypto_driver.casper=y`, `CONFIG_MCUX_COMPONENT_component.psa_crypto_driver.hashcrypt=y` configs in the application `prj.conf` file.

- **Health Care IoT Reference design applications**

- \* Support for **Keil toolchain** added.

- \* Fixed central application not retaining bonding information

- \* Moved **ENABLE\_LOW\_POWER** flag to `app_preinclude.h` for the peripheral application

- **Bluetooth LE host stack and applications**

- \* Support for **EATT Central/Peripheral** applications.

- \* Support for **FSCI black box** application.

- \* Support for **Beacon** application.

- \* **HCI transport** now uses the Connectivity Framework's PLATFORM API implementation

- **Connectivity Framework**

- [Common] Added MDK compatibility for the `errno` framework header.

- [OTA] Corrected definition of `gEepromParams_WriteAlignment_c` flag for `mcxw23`

- [OTA] Enabled calling `OTA_GetImgState()` prior to `OTA_Initialize()`.

- [OTA] Removed `gUseInternalStorageLink_d` linker flag definition when external OTA storage is used.

- [mcxw23] Implemented missing `PLATFORM_OtaClearBootInterface()` API.

- [mcxw23] Refactored `fwk_platform.c` to separate BLE-specific logic into `fwk_platform_ble.c`.

- [mcxw23] Introduced `PLATFORM_GetRadioIdleDuration32K()` to estimate time until next radio event.

- [mcxw23] Implemented HCI interface using `PLATFORM` API as preliminary requirement for Zephyr enablement, introducing `PLATFORM_SendHciMessageAlt()` alternative API.

- [mcxw23] Added experimental SecLib PSA support with additional configuration for `MBEDTLS_ECP_C` and `MBEDTLS_BIGNUM_C`.

## Known issues

This section lists the known issues, limitations, and/or workarounds.

### Limitations when creating a new FreeRTOS-based C/C++ project

Due to the missing component dependencies definition, there are several limitations when creating a new FreeRTOS-based C/C++ project in MCUXpresso IDE. When the **FreeRTOS kernel** component is selected (under Operating Systems/RTOS/Core menu), you must manually select the **FreeRTOS cm33 non trustzone port** component (under Middleware/RTOS menu) for projects without TrustZone. For FreeRTOS TrustZone projects creation, the support is not ready.

### Wireless UART application – Bluetooth Low Energy advertising and connection loss issue

When using the Wireless UART application with default settings, functionality is as expected. However, the following issue occurs when the Bluetooth Low Energy advertising interval is set to 20 milliseconds and the connection interval is set to 7.5 milliseconds: After two devices establish a connection, the central device fails to start advertising to a third device after a button press. The HCI command to start advertising returns success, but the device does not transmit any advertising packets. Additionally, the supervision timeout causes the existing connection to drop unexpectedly.

### Bluetooth Synopsys Controller

- Stability observation during extended testing The `llhwc_set_adv_param` function shows unexpected behavior during extended sequences of link layer tests, typically after 1.5 hours of continuous execution without a hardware reset.

- This rare behavior occurs only under specific test conditions.

- The behavior relates to the extended advertising feature.

- This behavior does not impact regular usage scenarios.

- Faulty passive channel assessment behavior

- Connection establishment fails when channel assessment finds only one suitable channel. However, the failure occurs rarely.

- Channel assessment fails on connections with slave latency greater than zero.

## 1.4 ChangeLog

### 1.4.1 MCUXpresso SDK Changelog

#### Board Support Files

##### board

###### [25.06.00]

- Initial version

##### clock\_config

###### [25.06.00]

- Initial version

##### pin\_mux

###### [25.06.00]

- Initial version

-

#### ANACTRL

##### [2.4.0]

- Improvements

- Added some interrupt flags for devices containing BOD1 and BOD2 interrupt controls.

- Added a control macro to enable/disable the 32MHz Crystal oscillator code in current driver.

- Added a feature macro for bit field ENA\_96MHZCLK in FRO192M\_CTRL.

- Added a feature macro for bit field BODCORE\_INT\_ENABLE in BOD\_DCDC\_INT\_CTRL.

##### [2.3.1]

- Bug Fixes

- Added casts to prevent overflow caused by capturing large target clock.

##### [2.3.0]

- Improvements

- Added AUX\_BIAS control APIs.

**[2.2.0]**

- Improvements

- Added some macros to separate the scenes that some bit fields are reserved for some devices.

- Optimized the comments.

- Optimized the code implementation inside some functions.

**[2.1.2]**

- Bug Fixes

- Fixed MISRA C-2012 rule 10.3 and rule 17.7.

**[2.1.1]**

- Bug Fixes

- Removed AnalogTestBus configuration to align with new header.

**[2.1.0]**

- Improvements

- Updates for LPC55xx A1.

- \* Removed the control of bitfield FRO192M\_CTRL\_ENA\_48MHZCLK, XO32M\_CTRL\_ACBUF\_PASS\_ENABLE.

- \* Removed status bits in ANACTRL\_STATUS: PMU\_ID OSC\_ID FINAL\_TEST\_DONE\_VECT.

- \* Removed API ANACTRL\_EnableAdcVBATDivider() and APIs which operate the RingOSC registers.

- \* Removed the configurations of 32 MHz Crystal oscillator voltage source supply control register.

- \* Added API ANACTRL\_ClearInterrupts().

**[2.0.0]**

- Initial version.

-

**CASSPER****[2.2.4]**

- Fix MISRA-C 2012 issue.

**[2.2.3]**

- Added macro into CASPER\_Init and CASPER\_Deinit to support devices without clock and reset control.

**[2.2.2]**

- Enable hardware interleaving to RAMX0 and RAMX1 for CASPER by feature macro FSL\_FEATURE\_CASPER\_RAM\_HW\_INTERLEAVE

**[2.2.1]**

- Fix MISRA C-2012 issue.

**[2.2.0]**

- Rework driver to support multiple curves at once.

**[2.1.0]**

- Add ECC NIST P-521 elliptic curve.

**[2.0.10]**

- Fix MISRA C-2012 issue.

**[2.0.9]**

- Remove unused function Jac\_oncurve().

- Fix ECC384 build.

**[2.0.8]**

- Add feature macro for CASPER\_RAM\_OFFSET.

**[2.0.7]**

- Fix MISRA C-2012 issue.

**[2.0.6]**

- Bug Fixes

- Fix IAR Pa082 warning

**[2.0.5]**

- Bug Fixes

- Fix sign-compare warning

**[2.0.4]**

- For GCC compiler, enforce O1 optimize level, specifically to remove strict-aliasing option. This driver is very specific and requires -fno-strict-aliasing.

### [2.0.3]

- Bug Fixes

- Fixed the bug for KPSDK-28107 RSUB, FILL and ZERO operations not implemented in enum \_casper\_operation.

### [2.0.2]

- Bug Fixes

- Fixed KPSDK-25015 CASPER\_MEMCPY hard-fault on LPC55xx when both source and destination buffers are outside of CASPER\_RAM.

### [2.0.1]

- Bug Fixes

- Fixed the bug that KPSDK-24531 double\_scalar\_multiplication() result may be all zeroes for some specific input.

### [2.0.0]

- Initial version.

-

## CDOG

### [2.1.3]

- Re-design multiple instance IRQs and Clocks

- Add fix for RESTART command errata

### [2.1.2]

- Support multiple IRQs

- Fix default CONTROL values

### [2.1.1]

- Remove bit CONTROL[CONTROL\_CTRL].

### [2.1.0]

- Rename CWT to CDOG.

### [2.0.2]

- Fix MISRA-2012 issues.

### [2.0.1]

- Fix doxygen issues.

## [2.0.0]

- Initial version.

-

## CLOCK

### [2.1.3]

- Improvements

- Added the missing enum kNONE\_to\_SCT\_CLK.

### [2.1.2]

- Improvements

- Include the fsl\_common.h in clock driver to fix the compiling issue in Zephyr build.

### [2.1.1]

- Improvements

- Fixed the coverity high issues in clock driver. Before using the pointer, check the passed parameter to ensure that it will not corrupt or misinterpret adjacent memory locations.

### [2.1.0]

- New Features

- Added CLOCK\_SetupPLUClkInClocking() to store the PLU CLKIN frequency.

- Bug Fixes

- Fixed CLOCK\_GetFlexCommClkFreq function to get flexcomm output frequency correctly.

- Fixed attach incorrect attach\_id for SCT.

### [2.0.3]

- Bug Fixes

- Fixed attach incorrect attach\_id.

### [2.0.2]

- New Features

- Added get actual clock attach id api to allow users to obtain the actual clock source in target register.

- Bug Fixes

- The attach clock and get actual clock attach id APIs should check combination of two clock sources.

- Optimizations

- Made the judgement statements more clear.

- Strengthened the compatibility of clock attach id.

- Removed some unmeaningful definitions and add some useful ones to enhance readability.

#### [2.0.1]

- Some minor fixes.

#### [2.0.0]

- Initial version.

-

### COMMON

#### [2.6.0]

- Bug Fixes

- Fix CERT-C violations.

#### [2.5.0]

- New Features

- Added new APIs InitCriticalSectionMeasurementContext, DisableGlobalIRQEx and EnableGlobalIRQEx so that user can measure the execution time of the protected sections.

#### [2.4.3]

- Improvements

- Enable irqs that mount under irqsteer interrupt extender.

#### [2.4.2]

- Improvements

- Add the macros to convert peripheral address to secure address or non-secure address.

#### [2.4.1]

- Improvements

- Improve for the macro redefinition error when integrated with zephyr.

#### [2.4.0]

- New Features

- Added EnableIRQWithPriority, IRQ\_SetPriority, and IRQ\_ClearPendingIRQ for ARM.

- Added MSDK\_EnableCpuCycleCounter, MSDK\_GetCpuCycleCount for ARM.

#### [2.3.3]

- New Features

- Added NETC into status group.

### [2.3.2]

- Improvements

- Make driver aarch64 compatible

### [2.3.1]

- Bug Fixes

- Fixed MAKE\_VERSION overflow on 16-bit platforms.

### [2.3.0]

- Improvements

- Split the driver to common part and CPU architecture related part.

### [2.2.10]

- Bug Fixes

- Fixed the ATOMIC macros build error in cpp files.

### [2.2.9]

- Bug Fixes

- Fixed MISRA C-2012 issue, 5.6, 5.8, 8.4, 8.5, 8.6, 10.1, 10.4, 17.7, 21.3.

- Fixed SDK\_Malloc issue that not allocate memory with required size.

### [2.2.8]

- Improvements

- Included stddef.h header file for MDK tool chain.

- New Features:

- Added atomic modification macros.

### [2.2.7]

- Other Change

- Added MECC status group definition.

### [2.2.6]

- Other Change

- Added more status group definition.

- Bug Fixes

- Undef \_\_VECTOR\_TABLE to avoid duplicate definition in cmsis\_clang.h

## [2.2.5]

- Bug Fixes

- Fixed MISRA C-2012 rule-15.5.

## [2.2.4]

- Bug Fixes

- Fixed MISRA C-2012 rule-10.4.

## [2.2.3]

- New Features

- Provided better accuracy of `SDK_DelayAtLeastUs` with DWT, use macro `SDK_DELAY_USE_DWT` to enable this feature.

- Modified the Cortex-M7 delay count divisor based on latest tests on RT series boards, this setting lets result be closer to actual delay time.

## [2.2.2]

- New Features

- Added include `RTE_Components.h` for CMSIS pack RTE.

## [2.2.1]

- Bug Fixes

- Fixed violation of MISRA C-2012 Rule 3.1, 10.1, 10.3, 10.4, 11.6, 11.9.

## [2.2.0]

- New Features

- Moved `SDK_DelayAtLeastUs` function from clock driver to common driver.

## [2.1.4]

- New Features

- Added OTFAD into status group.

## [2.1.3]

- Bug Fixes

- MISRA C-2012 issue fixed.

- \* Fixed the rule: rule-10.3.

## [2.1.2]

- Improvements

- Add `SUPPRESS_FALL_THROUGH_WARNING()` macro for the usage of suppressing fallthrough warning.

### [2.1.1]

- Bug Fixes

- Deleted and optimized repeated macro.

### [2.1.0]

- New Features

- Added IRQ operation for XCC toolchain.

- Added group IDs for newly supported drivers.

### [2.0.2]

- Bug Fixes

- MISRA C-2012 issue fixed.

- \* Fixed the rule: rule-10.4.

### [2.0.1]

- Improvements

- Removed the implementation of LPC8XX Enable/DisableDeepSleepIRQ() function.

- Added new feature macro switch “FSL\_FEATURE\_HAS\_NO\_NONCACHEABLE\_SECTION” for specific SoCs which have no noncacheable sections, that helps avoid an unnecessary complex in link file and the startup file.

- Updated the align(x) to **attribute**(aligned(x)) to support MDK v6 armclang compiler.

### [2.0.0]

- Initial version.

-

## CRC

### [2.1.1]

- Fix MISRA issue.

### [2.1.0]

- Add CRC\_WriteSeed function.

### [2.0.2]

- Fix MISRA issue.

### [2.0.1]

- Fixed KPSDK-13362. MDK compiler issue when writing to WR\_DATA with -O3 optimize for time.

**[2.0.0]**

- Initial version.

-

**C TIMER****[2.3.3]**

- Bug Fixes

- Fix CERT INT30-C INT31-C issue.

- Make API CTIMER\_SetupPwm and CTIMER\_UpdatePwmDutycycle return fail if pulse width register overflow.

**[2.3.2]**

- Bug Fixes

- Clear unexpected DMA request generated by RESET\_PeripheralReset in API CTIMER\_Init to avoid trigger DMA by mistake.

**[2.3.1]**

- Bug Fixes

- MISRA C-2012 issue fixed: rule 10.7 and 12.2.

**[2.3.0]**

- Improvements

- Added the CTIMER\_SetPrescale0(), CTIMER\_GetCaptureValue0(), CTIMER\_EnableResetMatchChannel0(), CTIMER\_EnableStopMatchChannel0(), CTIMER\_EnableRisingEdgeCapture0(), CTIMER\_EnableFallingEdgeCapture0(), CTIMER\_SetShadowValue0(), APIs Interface to reduce code complexity.

**[2.2.2]**

- Bug Fixes

- Fixed SetupPwm() API only can use match 3 as period channel issue.

**[2.2.1]**

- Bug Fixes

- Fixed use specified channel to setting the PWM period in SetupPwmPeriod() API.

- Fixed Coverity Out-of-bounds issue.

## [2.2.0]

- Improvements

- Updated three API Interface to support Users to flexibly configure the PWM period and PWM output.

- Bug Fixes

- MISRA C-2012 issue fixed: rule 8.4.

## [2.1.0]

- Improvements

- Added the CTIMER\_GetOutputMatchStatus() API Interface.

- Added feature macro for FSL\_FEATURE\_CTIMER\_HAS\_NO\_CCR\_CAP2 and FSL\_FEATURE\_CTIMER\_HAS\_NO\_IR\_CR2INT.

## [2.0.3]

- Bug Fixes

- MISRA C-2012 issue fixed: rule 10.3, 10.4, 10.6, 10.7 and 11.9.

## [2.0.2]

- New Features

- Added new API “CTIMER\_GetTimerCountValue” to get the current timer count value.

- Added a control macro to enable/disable the RESET and CLOCK code in current driver.

- Added a new feature macro to update the API of CTimer driver for lpc8n04.

## [2.0.1]

- Improvements

- API Interface Change

- \* Changed API interface by adding CTIMER\_SetupPwmPeriod API and CTIMER\_UpdatePwmPulsePeriod API, which both can set up the right PWM with high resolution.

## [2.0.0]

- Initial version.

-

## LPC\_DMA

### [2.5.3]

- Improvements

- Add assert in DMA\_SetChannelXferConfig to prevent XFERCOUNT value overflow.

**[2.5.2]**

- Bug Fixes

- Use separate “SET” and “CLR” registers to modify shared registers for all channels, in case of thread-safe issue.

**[2.5.1]**

- Bug Fixes

- Fixed violation of the MISRA C-2012 rule 11.6.

**[2.5.0]**

- Improvements

- Added a new api DMA\_SetChannelXferConfig to set DMA xfer config.

**[2.4.4]**

- Bug Fixes

- Fixed the issue that DMA\_IRQHandler might generate redundant callbacks.

- Fixed the issue that DMA driver cannot support channel bigger then 32.

- Fixed violation of the MISRA C-2012 rule 13.5.

**[2.4.3]**

- Improvements

- Added features FSL\_FEATURE\_DMA\_DESCRIPTOR\_ALIGN\_SIZEn/FSL\_FEATURE\_DMA0\_DESCRIPTOR\_ALIGN\_SIZE to support the descriptor align size not constant in the two instances.

**[2.4.2]**

- Bug Fixes

- Fixed violation of the MISRA C-2012 rule 8.4.

**[2.4.1]**

- Bug Fixes

- Fixed violations of the MISRA C-2012 rules 5.7, 8.3.

**[2.4.0]**

- Improvements

- Added new APIs DMA\_LoadChannelDescriptor/DMA\_ChannelIsBusy to support polling transfer case.

- Bug Fixes

- Added address alignment check for descriptor source and destination address.

- Added DMA\_ALLOCATE\_DATA\_TRANSFER\_BUFFER for application buffer allocation.

- Fixed the sign-compare warning.

- Fixed violations of the MISRA C-2012 rules 18.1, 10.4, 11.6, 10.7, 14.4, 16.3, 20.7, 10.8, 16.1, 17.7, 10.3, 3.1, 18.1.

### [2.3.0]

- Bug Fixes

- Removed DMA\_HandleIRQ prototype definition from header file.

- Added DMA\_IRQHandle prototype definition in header file.

### [2.2.5]

- Improvements

- Added new API DMA\_SetupChannelDescriptor to support configuring wrap descriptor.

- Added wrap support in function DMA\_SubmitChannelTransfer.

### [2.2.4]

- Bug Fixes

- Fixed the issue that macro DMA\_CHANNEL\_CFER used wrong parameter to calculate DSTINC.

### [2.2.3]

- Bug Fixes

- Improved DMA driver Deinit function for correct logic order.

- Improvements

- Added API DMA\_SubmitChannelTransferParameter to support creating head descriptor directly.

- Added API DMA\_SubmitChannelDescriptor to support ping pong transfer.

- Added macro DMA\_ALLOCATE\_HEAD\_DESCRIPTOR/DMA\_ALLOCATE\_LINK\_DESCRIPTOR to simplify DMA descriptor allocation.

### [2.2.2]

- Bug Fixes

- Do not use software trigger when hardware trigger is enabled.

### [2.2.1]

- Bug Fixes

- Fixed Coverity issue.

**[2.2.0]**

- Improvements

- Changed API DMA\_SetupDMADescriptor to non-static.

- Marked APIs below as deprecated.

- \* DMA\_PrepTransfer.

- \* DMA\_Submit transfer.

- Added new APIs as below:

- \* DMA\_SetChannelConfig.

- \* DMA\_PrepChannelTransfer.

- \* DMA\_InstallDescriptorMemory.

- \* DMA\_SubmitChannelTransfer.

- \* DMA\_SetChannelConfigValid.

- \* DMA\_DoChannelSoftwareTrigger.

- \* DMA\_LoadChannelTransferConfig.

**[2.0.1]**

- Improvements

- Added volatile for DMA descriptor member xfercfg to avoid optimization.

**[2.0.0]**

- Initial version.

-

**FLEXCOMM****[2.0.2]**

- Bug Fixes

- Fixed typos in FLEXCOMM15\_DriverIRQHandler().

- Fixed MISRA issues.

- \* Fixed rules 10.1, 10.3, 10.4, 10.7, 10.8, 11.3, 11.6, 11.8, 11.9, 13.5.

- Improvements

- Added instance calculation in FLEXCOMM16\_DriverIRQHandler() to align with Flex-comm 14 and 15.

**[2.0.1]**

- Improvements

- Added more IRQHandler code in drivers to adapt new devices.

## [2.0.0]

- Initial version.

-

## GPIO

### [2.1.1]

- Improvements

- Added support for platforms with PORT\_POL and PORT\_ENA registers without arrays.

### [2.1.0]

- Improvements

- Updated for platforms which only has one port.

### [2.0.3]

- Bug Fixes

- MISRA C-2012 issue fixed: rule 10.8.

### [2.0.2]

- Bug Fixes

- Fixed issue for MISRA-2012 check.

- Fixed rule 17.7.

### [2.0.1]

- Added control macro to enable/disable the RESET and CLOCK code in current driver.

### [2.0.0]

- Initial version.

-

## GPIO

### [2.1.7]

- Improvements

- Enhanced GPIO\_PinInit to enable clock internally.

### [2.1.6]

- Bug Fixes

- Clear bit before set it within GPIO\_SetPinInterruptConfig() API.

### [2.1.5]

- Bug Fixes

- Fixed violations of the MISRA C-2012 rules 3.1, 10.6, 10.7, 17.7.

### [2.1.4]

- Improvements

- Added API GPIO\_PortGetInterruptStatus to retrieve interrupt status for whole port.

- Corrected typos in header file.

### [2.1.3]

- Improvements

- Updated “GPIO\_PinInit” API. If it has DIRCLR and DIRSET registers, use them at set 1 or clean 0.

### [2.1.2]

- Improvements

- Removed deprecated APIs.

### [2.1.1]

- Improvements

- API interface changes:

- \* Refined naming of APIs while keeping all original APIs, marking them as deprecated. Original APIs will be removed in next release. The mainin change is updating APIs with prefix of \_PinXXX() and \_PorortXXX

### [2.1.0]

- New Features

- Added GPIO initialize API.

### [2.0.0]

- Initial version.

-

## HASHCRYPT

### [2.0.0]

- Initial version.

### [2.0.1]

- Supported loading AES key from unaligned address.

**[2.0.2]**

- Supported loading AES key from unaligned address for different compiler and core variants.

**[2.0.3]**

- Remove SHA512 and AES ICB algorithm definitions

**[2.0.4]**

- Add SHA context switch support

**[2.1.0]**

- Update the register name and macro to align with new header.

- Fixed the sign-compare warning in hashcrypt\_load\_data.

**[2.1.1]**

- Fix MISRA C-2012.

**[2.1.2]**

- Support loading AES input data from unaligned address.

**[2.1.3]**

- Fix MISRA C-2012.

**[2.1.4]**

- Fix context switch cannot work when switching from AES.

**[2.1.5]**

- Add data synchronization barrier inside hashcrypt\_sha\_ldm\_stm\_16\_words() to prevent possible optimization issue.

**[2.2.0]**

- Add AES-OFB and AES-CFB mixed IP/SW modes.

**[2.2.1]**

- Add data synchronization barrier inside hashcrypt\_sha\_ldm\_stm\_16\_words() prevent compiler from reordering memory write when -O2 or higher is used.

**[2.2.2]**

- Add data synchronization barrier inside hashcrypt\_sha\_ldm\_stm\_16\_words() to fix optimization issue

**[2.2.3]**

- Added check for size in hashcrypt\_aes\_one\_block to prevent overflowing COUNT field in MEMCTRL register, if its bigger than COUNT field do a multiple runs.

**[2.2.4]**

- In all HASHCRYPT\_AES\_xx functions have been added setting CTRL\_MODE bitfield to 0 after processing data, which decreases power consumption.

**[2.2.5]**

- Add data synchronization barrier and instruction synchronization barrier inside hashcrypt\_sha\_process\_message\_data() to fix optimization issue

**[2.2.6]**

- Add data synchronization barrier inside HASHCRYPT\_SHA\_Update() and hashcrypt\_get\_data() function to fix optimization issue on MDK and ARMGCC release targets

**[2.2.7]**

- Add data synchronization barrier inside HASHCRYPT\_SHA\_Update() to fix optimization issue on MCUX IDE release target

**[2.2.8]**

- Unify hashcrypt hashing behavior between aligned and unaligned input data

**[2.2.9]**

- Add handling of set ERROR bit in the STATUS register

**[2.2.10]**

- Fix missing error statement in hashcrypt\_save\_running\_hash()

**[2.2.11]**

- Fix incorrect SHA-256 calculation for long messages with reload

**[2.2.12]**

- Fix hardfault issue on the Keil compiler due to unaligned memcpy() input on some optimization levels

**[2.2.13]**

- Added function hashcrypt\_seed\_prng() which loading random number into PRNG\_SEED register before AES operation for SCA protection

**[2.2.14]**

- Modify function hashcrypt\_get\_data() to prevent issue with unaligned access

**[2.2.15]**

- Add wait on DIGEST BIT inside hashcrypt\_sha\_one\_block() to fix issues with some optimization flags

**[2.2.16]**

- Add DSB instruction inside hashcrypt\_sha\_ldm\_stm\_16\_words() to fix issues with some optimization flags

**[2.2.17]**

- Fix context size when hashcrypt built with reload feature

-

**I2C**

**[2.3.3]**

- Bug Fixes

- Fixed violations of the MISRA C-2012 rules 10.1.

- Fixed issue that if master only sends address without data during I2C interrupt transfer, address nack cannot be detected.

**[2.3.2]**

- Improvement

- Enable or disable timeout option according to enableTimeout.

- Bug Fixes

- Fixed timeout value calculation error.