# MCUXpresso SDK Documentation

Release 25.09.00

NXP

Sep 19, 2025

# Table of contents

|          |                                                                    |            |

|----------|--------------------------------------------------------------------|------------|

| <b>1</b> | <b>FRDM-KE02Z40M</b>                                               | <b>3</b>   |

| 1.1      | Overview . . . . .                                                 | 3          |

| 1.2      | Getting Started with MCUXpresso SDK Package . . . . .              | 3          |

| 1.2.1    | Getting Started with MCUXpresso SDK Package . . . . .              | 3          |

| 1.3      | Getting Started with MCUXpresso SDK GitHub . . . . .               | 55         |

| 1.3.1    | Getting Started with MCUXpresso SDK Repository . . . . .           | 55         |

| 1.4      | Release Notes . . . . .                                            | 68         |

| 1.4.1    | MCUXpresso SDK Release Notes . . . . .                             | 68         |

| 1.5      | ChangeLog . . . . .                                                | 71         |

| 1.5.1    | MCUXpresso SDK Changelog . . . . .                                 | 71         |

| 1.6      | Driver API Reference Manual . . . . .                              | 96         |

| 1.7      | Middleware Documentation . . . . .                                 | 96         |

| 1.7.1    | FreeMASTER . . . . .                                               | 96         |

| <b>2</b> | <b>MKE02Z4</b>                                                     | <b>97</b>  |

| 2.1      | ACMP: Analog Comparator Driver . . . . .                           | 97         |

| 2.2      | ADC: 12-bit Analog to Digital Converter Driver . . . . .           | 100        |

| 2.3      | Clock Driver . . . . .                                             | 106        |

| 2.4      | CRC: Cyclic Redundancy Check Driver . . . . .                      | 117        |

| 2.5      | GPIO Driver . . . . .                                              | 120        |

| 2.6      | FTMRx Flash Driver . . . . .                                       | 122        |

| 2.7      | FTM: FlexTimer Driver . . . . .                                    | 140        |

| 2.8      | GPIO: General-Purpose Input/Output Driver . . . . .                | 162        |

| 2.9      | GPIO Driver . . . . .                                              | 163        |

| 2.10     | I2C: Inter-Integrated Circuit Driver . . . . .                     | 165        |

| 2.11     | I2C Driver . . . . .                                               | 165        |

| 2.12     | Irq . . . . .                                                      | 179        |

| 2.13     | IRQ: external interrupt (IRQ) module . . . . .                     | 182        |

| 2.14     | KBI: Keyboard interrupt Driver . . . . .                           | 182        |

| 2.15     | Common Driver . . . . .                                            | 183        |

| 2.16     | MCM: Miscellaneous Control Module . . . . .                        | 195        |

| 2.17     | PIT: Periodic Interrupt Timer . . . . .                            | 200        |

| 2.18     | PORT Driver . . . . .                                              | 204        |

| 2.19     | RTC: Real Time Clock . . . . .                                     | 211        |

| 2.20     | SPI: Serial Peripheral Interface Driver . . . . .                  | 216        |

| 2.21     | SPI Driver . . . . .                                               | 216        |

| 2.22     | TPM: Timer PWM Module . . . . .                                    | 229        |

| 2.23     | UART: Universal Asynchronous Receiver/Transmitter Driver . . . . . | 240        |

| 2.24     | UART Driver . . . . .                                              | 240        |

| 2.25     | WDOG8: 8-bit Watchdog Timer . . . . .                              | 255        |

| <b>3</b> | <b>Middleware</b>                                                  | <b>259</b> |

| 3.1      | Motor Control . . . . .                                            | 259        |

| 3.1.1    | FreeMASTER . . . . .                                               | 259        |

| <b>4</b> | <b>RTOS</b>                                                        | <b>297</b> |

| 4.1      | FreeRTOS . . . . .                                                 | 297        |

|       |                   |     |

|-------|-------------------|-----|

| 4.1.1 | FreeRTOS kernel   | 297 |

| 4.1.2 | FreeRTOS drivers  | 297 |

| 4.1.3 | backoffalgorithm  | 297 |

| 4.1.4 | corehttp          | 297 |

| 4.1.5 | corejson          | 297 |

| 4.1.6 | coremqtt          | 298 |

| 4.1.7 | coremqtt-agent    | 298 |

| 4.1.8 | corepkcs11        | 298 |

| 4.1.9 | freertos-plus-tcp | 298 |

This documentation contains information specific to the frdmke02z40m board.

# Chapter 1

## FRDM-KE02Z40M

### 1.1 Overview

The Freedom-KE02Z40M is an ultra-low-cost development platform for Kinetis KE02 MCUs

MCU device and part on board is shown below:

- Device: MKE02Z4

- PartNumber: MKE02Z64VQH4

### 1.2 Getting Started with MCUXpresso SDK Package

#### 1.2.1 Getting Started with MCUXpresso SDK Package

##### Overview

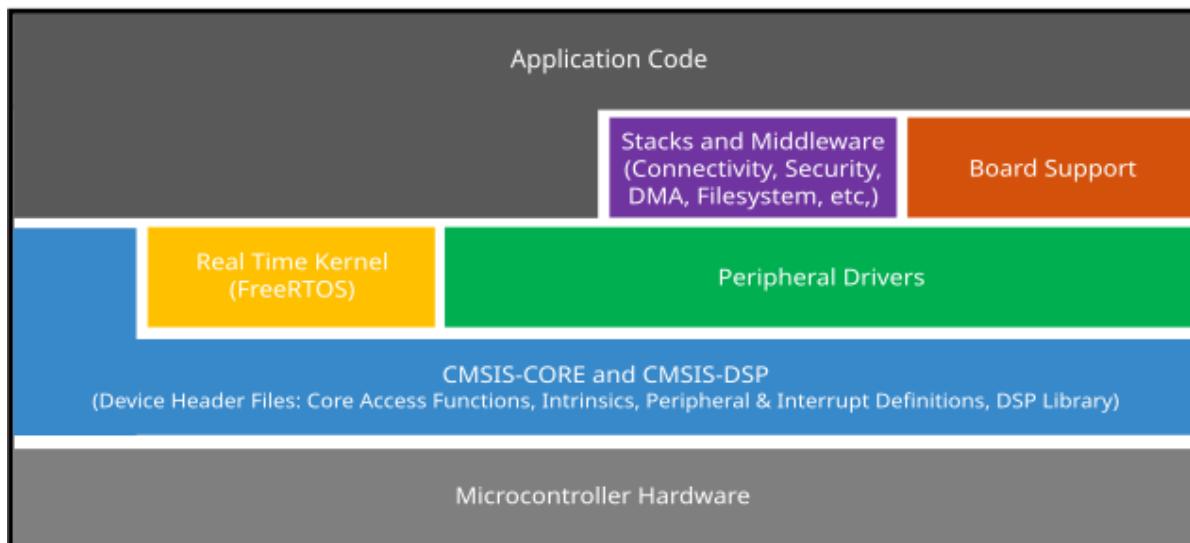

The NXP MCUXpresso software and tools offer comprehensive development solutions designed to optimize, ease, and help accelerate embedded system development of applications based on general purpose, crossover, and Bluetooth-enabled MCUs from NXP. The MCUXpresso SDK includes a flexible set of peripheral drivers designed to speed up and simplify development of embedded applications. Along with the peripheral drivers, the MCUXpresso SDK provides an extensive and rich set of example applications covering everything from basic peripheral use case examples to full demo applications. The MCUXpresso SDK contains optional RTOS integrations such as FreeRTOS and Azure RTOS, and various other middleware to support rapid development.

For supported toolchain versions, see *MCUXpresso SDK Release Notes* (document MCUXSDKRNN).

For more details about MCUXpresso SDK, see [MCUXpresso Software Development Kit \(SDK\)](#).

## MCUXpresso SDK board support package folders

MCUXpresso SDK board support package provides example applications for NXP development and evaluation boards for Arm Cortex-M cores including Freedom, Tower System, and LPCXpresso boards. Board support packages are found inside the top-level boards folder and each supported board has its own folder (an MCUXpresso SDK package can support multiple boards). Within each `<board_name>` folder, there are various subfolders to classify the type of examples it contains. These include (but are not limited to):

- `cmsis_driver_examples`: Simple applications intended to show how to use CMSIS drivers.

- `demo_apps`: Full-featured applications that highlight key functionality and use cases of the target MCU. These applications typically use multiple MCU peripherals and may leverage stacks and middleware.

- `driver_examples`: Simple applications that show how to use the MCUXpresso SDK's peripheral drivers for a single use case. These applications typically only use a single peripheral but there are cases where multiple peripherals are used (for example, SPI conversion using DMA).

- `emwin_examples`: Applications that use the emWin GUI widgets.

- `rtos_examples`: Basic FreeRTOS OS examples that show the use of various RTOS objects (semaphores, queues, and so on) and interfaces with the MCUXpresso SDK's RTOS drivers

- `usb_examples`: Applications that use the USB host/device/OTG stack.

**Example application structure** This section describes how the various types of example applications interact with the other components in the MCUXpresso SDK. To get a comprehensive understanding of all MCUXpresso SDK components and folder structure, see *MCUXpresso SDK API Reference Manual*.

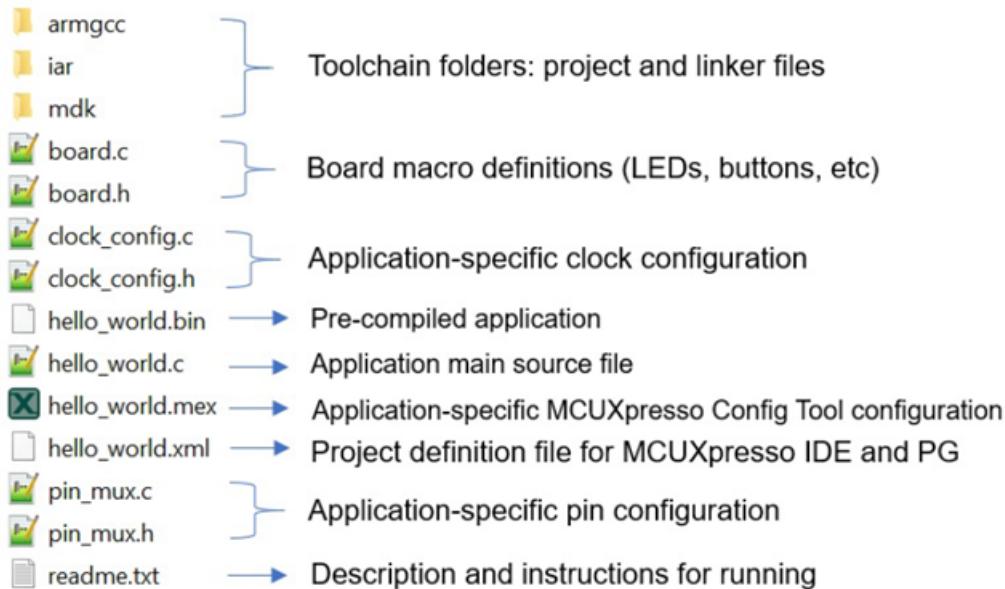

Each `<board_name>` folder in the boards directory contains a comprehensive set of examples that are relevant to that specific piece of hardware. Although we use the `hello_world` example (part of the `demo_apps` folder), the same general rules apply to any type of example in the `<board_name>` folder.

In the `hello_world` application folder you see the following contents:

All files in the application folder are specific to that example, so it is easy to copy and paste an existing example to start developing a custom application based on a project provided in the MCUXpresso SDK.

**Locating example application source files** When opening an example application in any of the supported IDEs, various source files are referenced. The MCUXpresso SDK devices folder is the central component to all example applications. It means that the examples reference the same source files and, if one of these files is modified, it could potentially impact the behavior of other examples.

The main areas of the MCUXpresso SDK tree used in all example applications are:

- devices/<device\_name>: The device's CMSIS header file, MCUXpresso SDK feature file, and a few other files

- devices/<device\_name>/cmsis\_drivers: All the CMSIS drivers for your specific MCU

- devices/<device\_name>/drivers: All of the peripheral drivers for your specific MCU

- devices/<device\_name>/<tool\_name>: Toolchain-specific startup code, including vector table definitions

- devices/<device\_name>/utilities: Items such as the debug console that are used by many of the example applications

- devices/<device\_name>/project: Project template used in CMSIS PACK new project creation

For examples containing middleware/stacks or an RTOS, there are references to the appropriate source code. Middleware source files are located in the middleware folder and RTOSes are in the rtos folder. The core files of each of these are shared, so modifying one could have potential impacts on other projects that depend on that file.

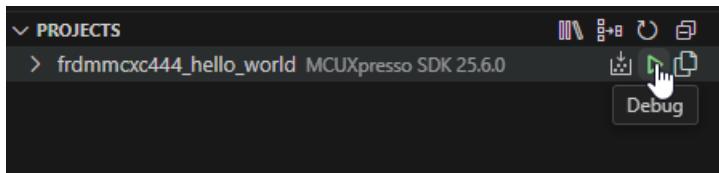

## Run a demo using MCUXpresso IDE

**Note:** Ensure that the MCUXpresso IDE toolchain is included when generating the MCUXpresso SDK package.

This section describes the steps required to configure MCUXpresso IDE to build, run, and debug example applications. The hello\_world demo application targeted for the hardware platform is

used as an example, though these steps can be applied to any example application in the MCUXpresso SDK.

**Select the workspace location** Every time MCUXpresso IDE launches, it prompts the user to select a workspace location. MCUXpresso IDE is built on top of Eclipse which uses workspace to store information about its current configuration, and in some use cases, source files for the projects are in the workspace. The location of the workspace can be anywhere, but it is recommended that the workspace be located outside the MCUXpresso SDK tree.

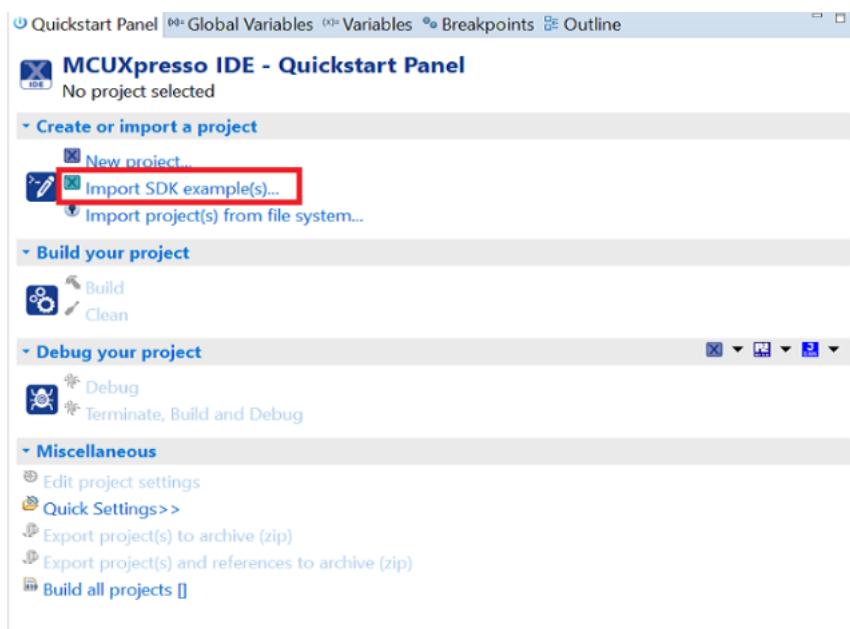

**Build an example application** To build an example application, follow these steps.

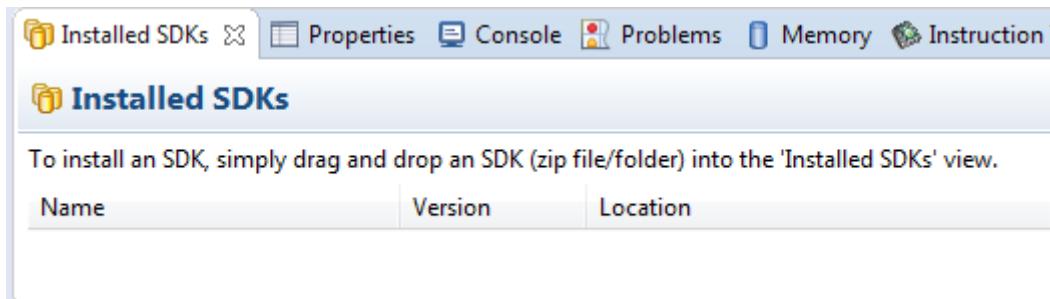

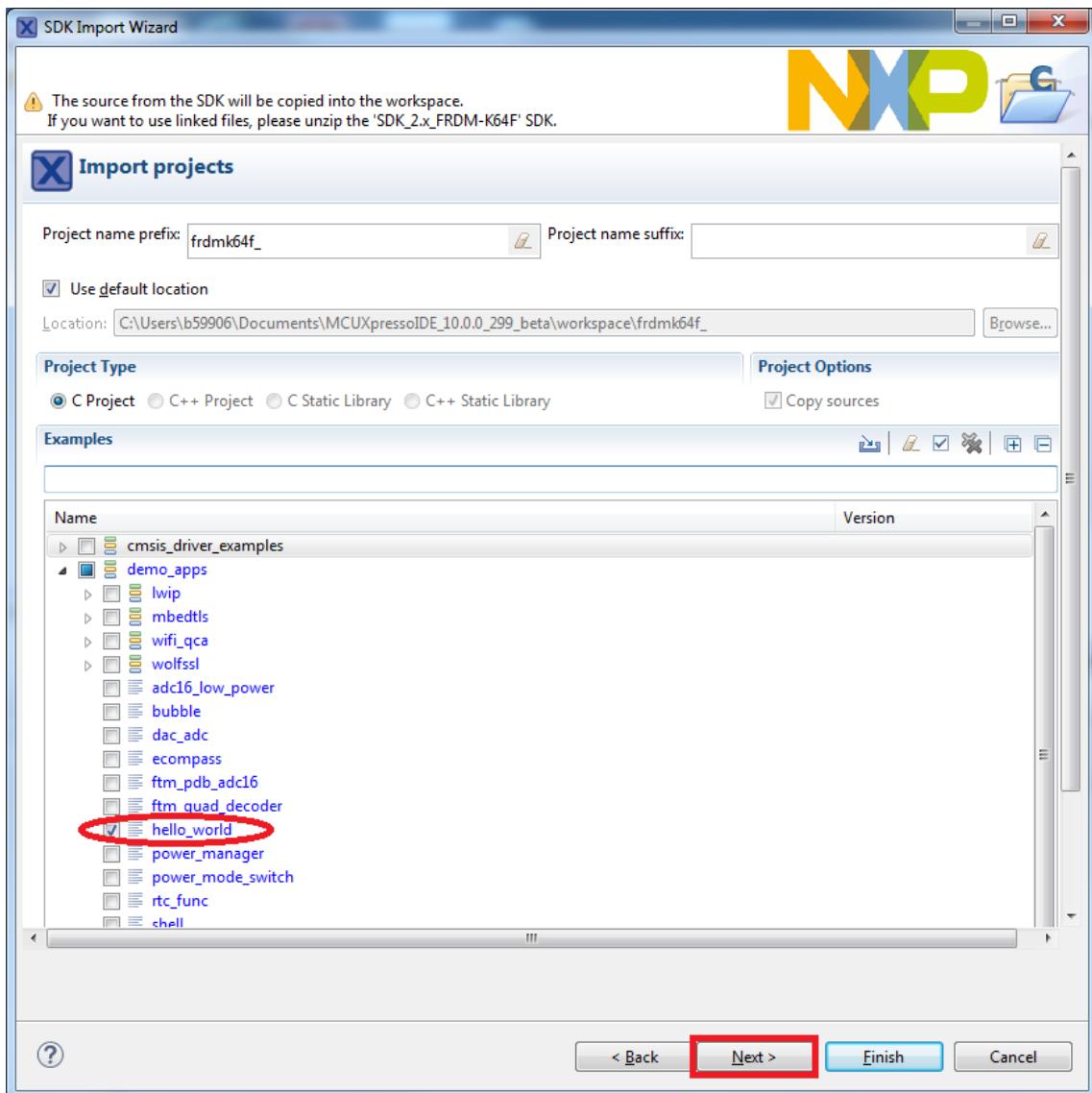

1. Drag and drop the SDK zip file into the **Installed SDKs** view to install an SDK. In the window that appears, click **OK** and wait until the import has finished.

2. On the **Quickstart Panel**, click **Import SDK example(s)....**

3. Expand the `demo_apps` folder and select `hello_world`.

4. Click **Next**.

5. Ensure **Redlib**: **Use floating-point version of printf** is selected if the example prints floating-point numbers on the terminal for demo applications such as adc\_basic, adc\_burst, adc\_dma, and adc\_interrupt. Otherwise, it is not necessary to select this option. Then, click **Finish**.

**Run an example application** For more information on debug probe support in the MCUXpresso IDE, see [community.nxp.com](http://community.nxp.com).

To download and run the application, perform the following steps:

1. Ensure the host driver for the debugger firmware has been installed. See [On-board debugger](#).

2. Connect the development platform to your PC via a USB cable.

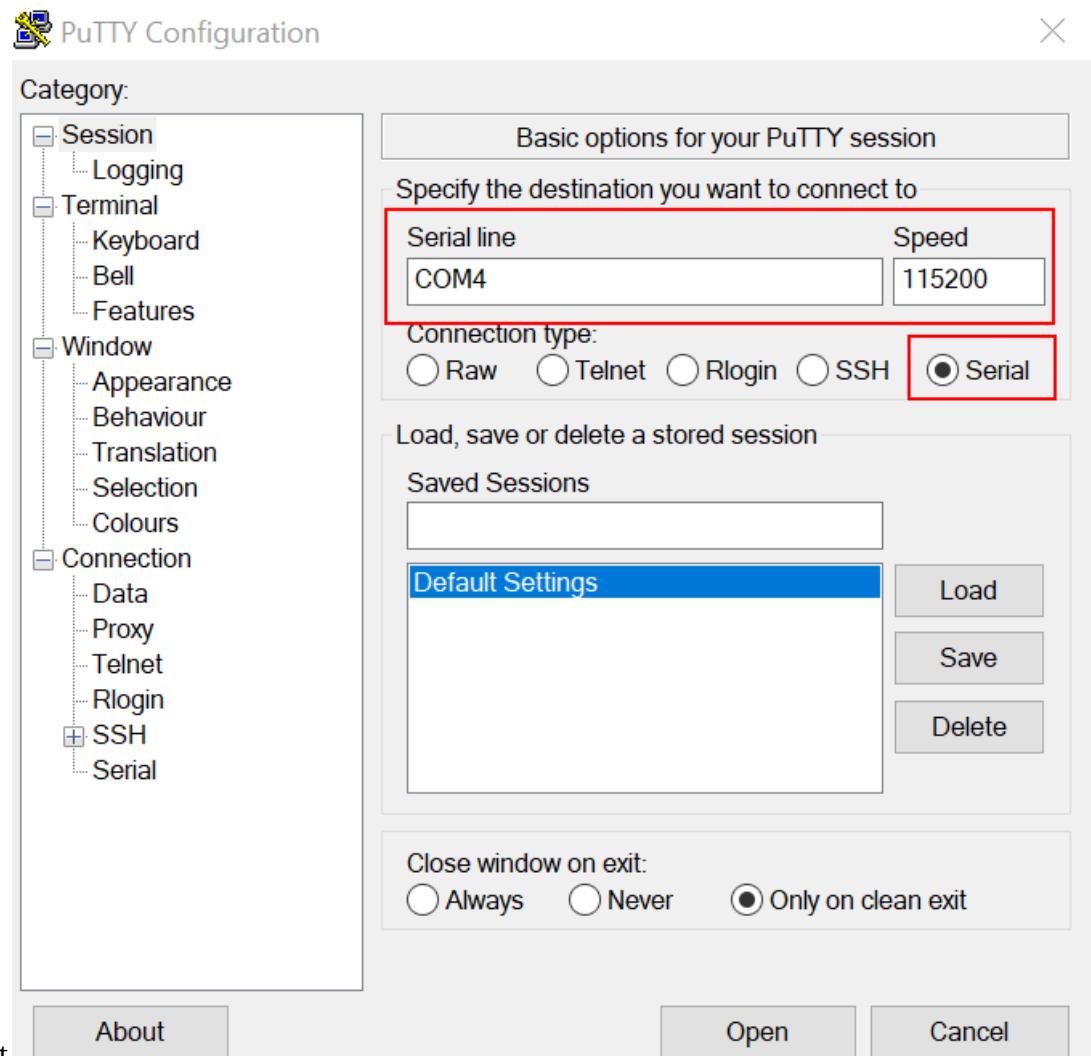

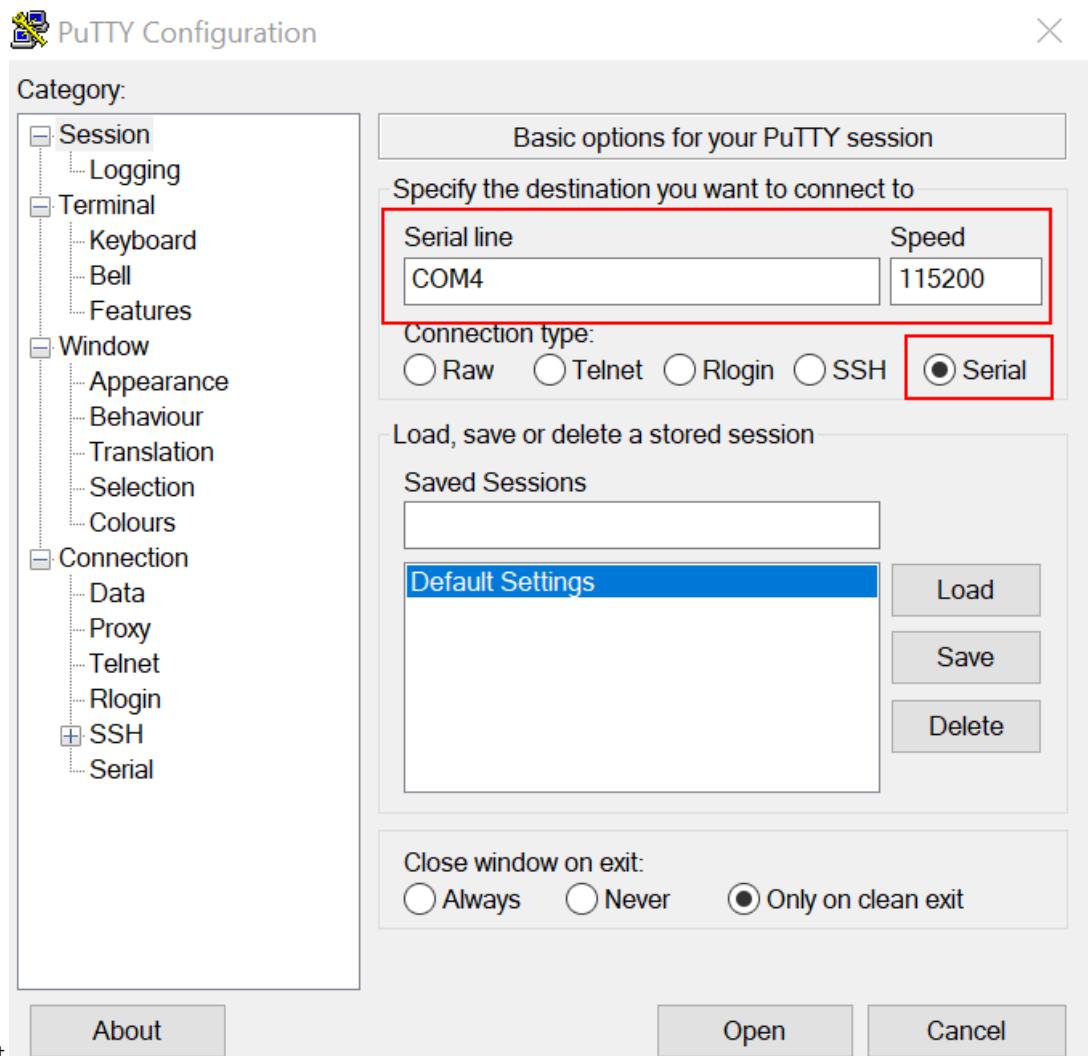

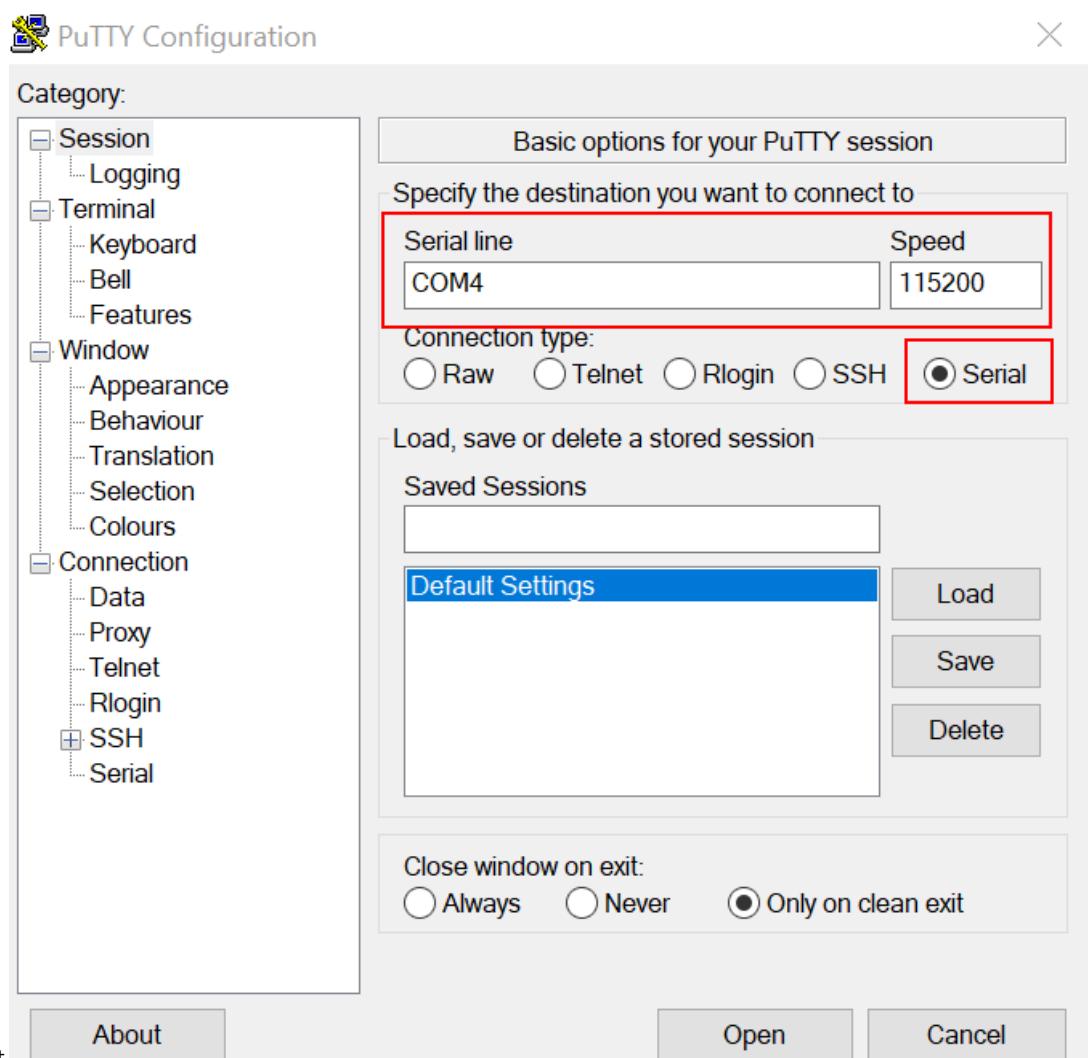

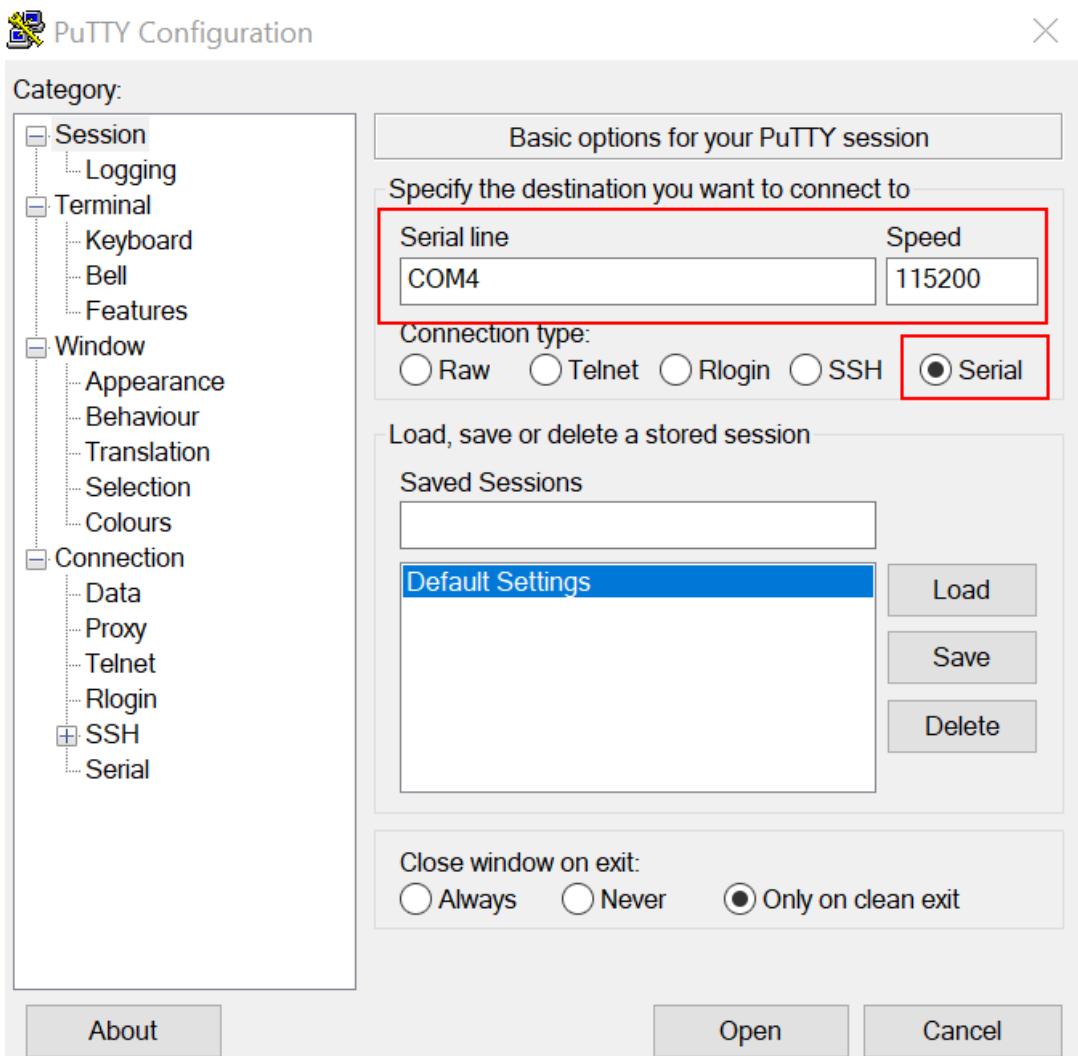

3. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug serial port number (to determine the COM port number, see [How to determine COM port](#)). Configure the terminal with these settings:

1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in board.h file)

2. No parity

## 3. 8 data bits

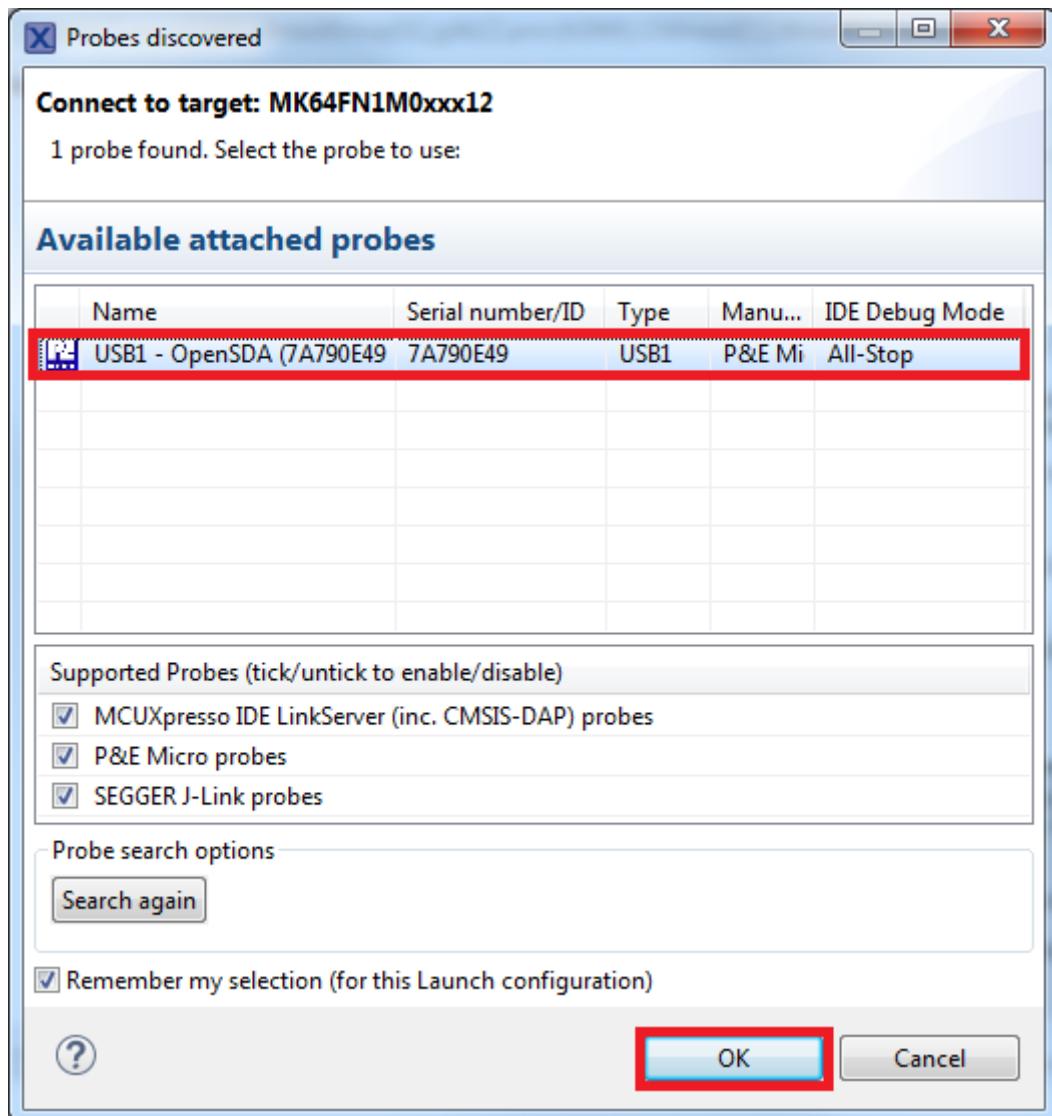

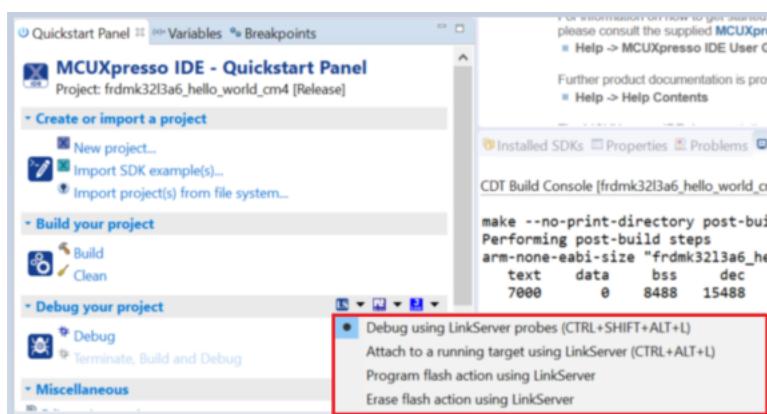

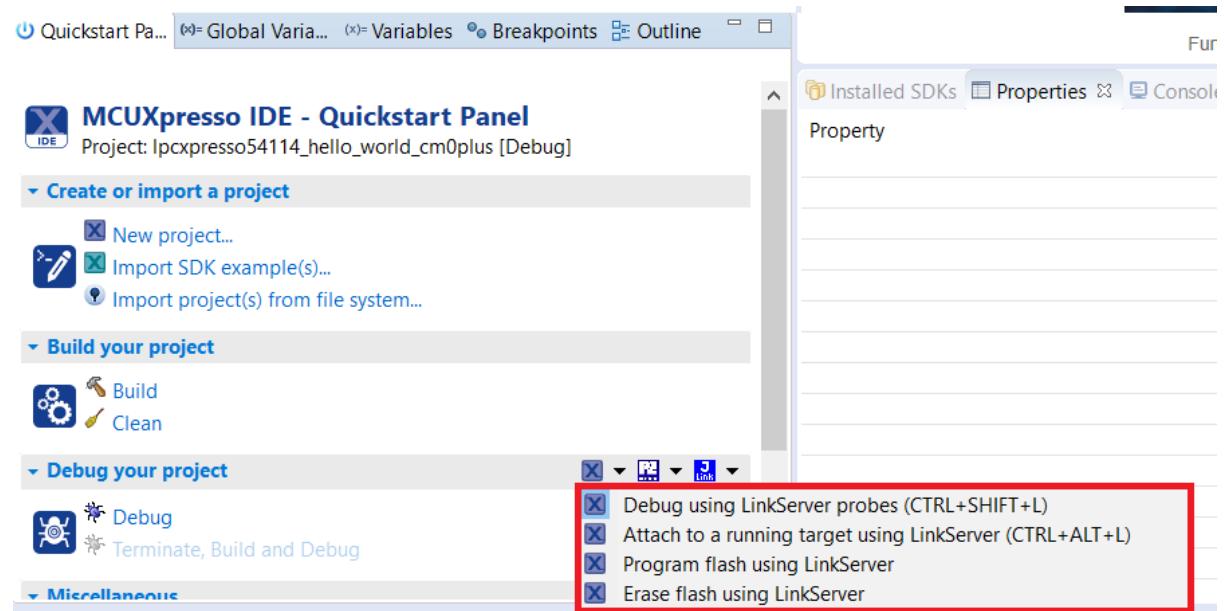

4. On the **Quickstart Panel**, click **Debug** to launch the debug session.

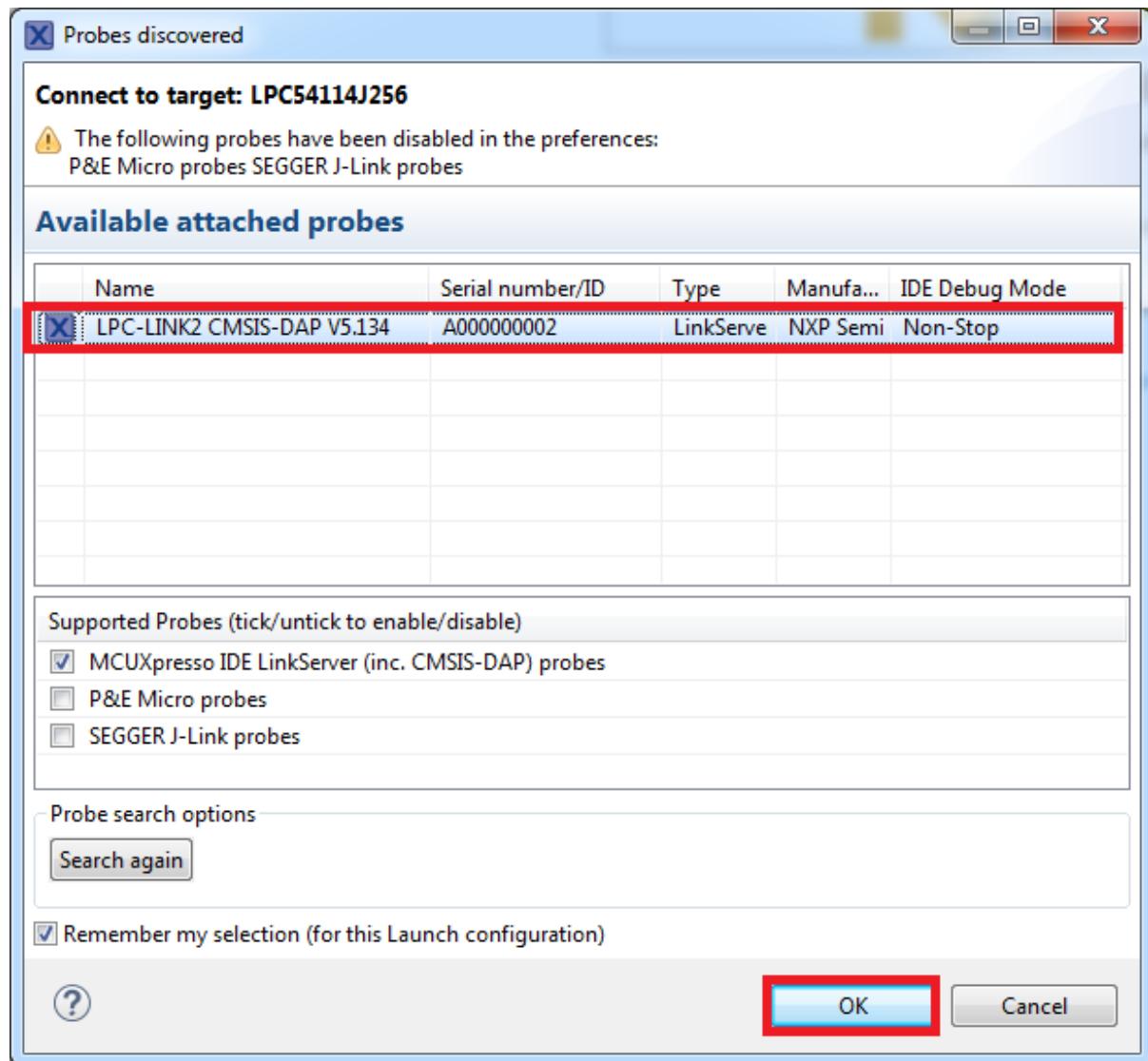

5. The first time you debug a project, the **Debug Emulator Selection** dialog is displayed, showing all supported probes that are attached to your computer. Select the probe through which you want to debug and click **OK**. (For any future debug sessions, the stored probe selection is automatically used, unless the probe cannot be found.)

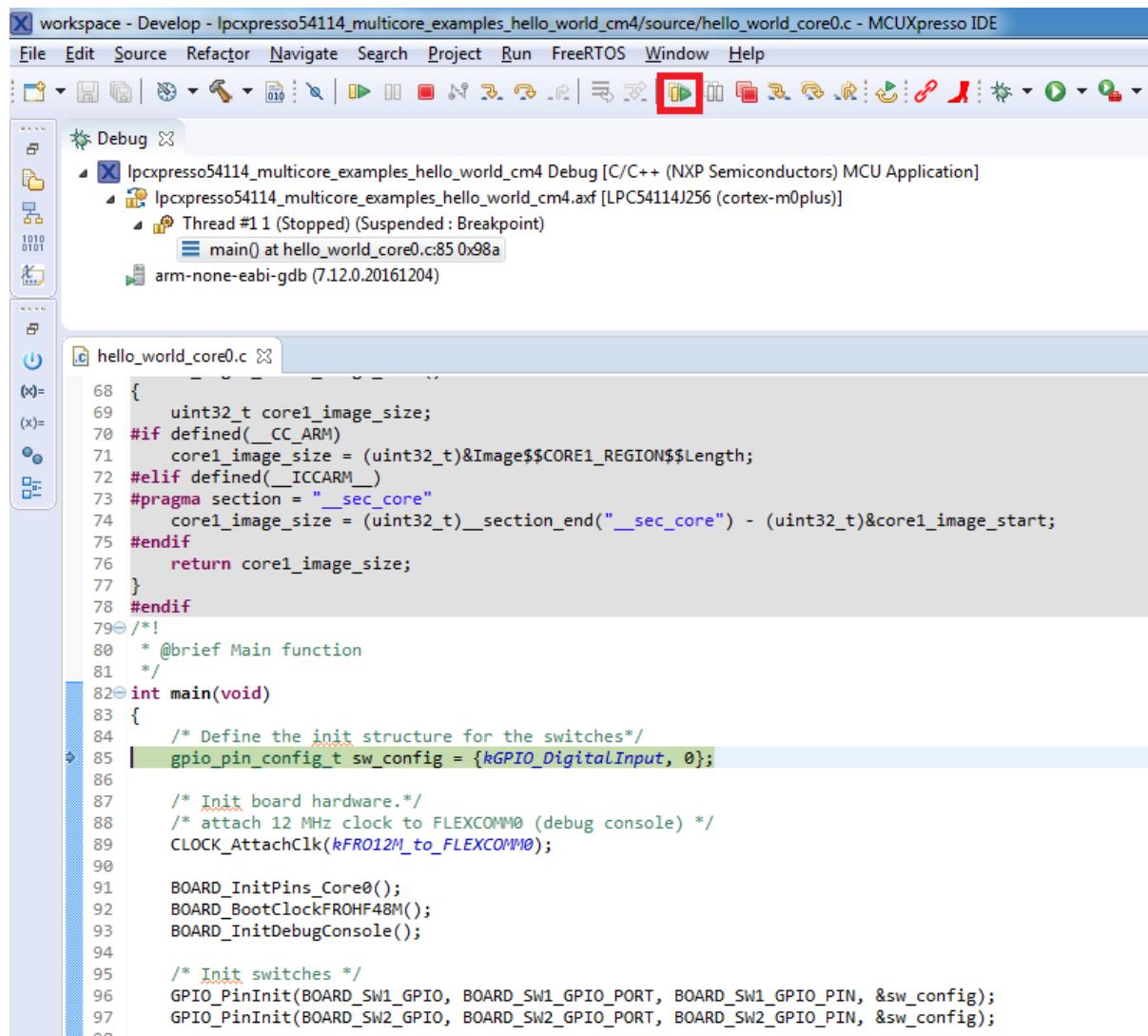

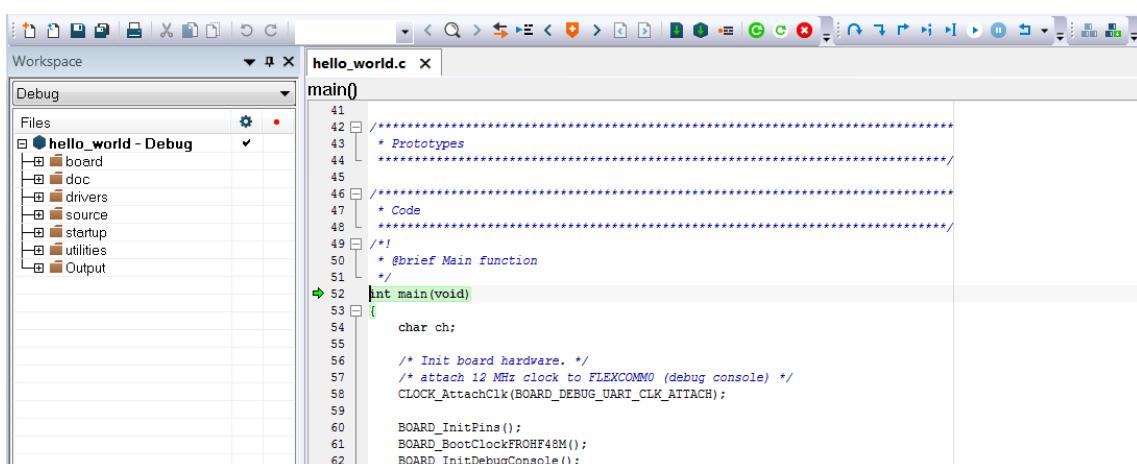

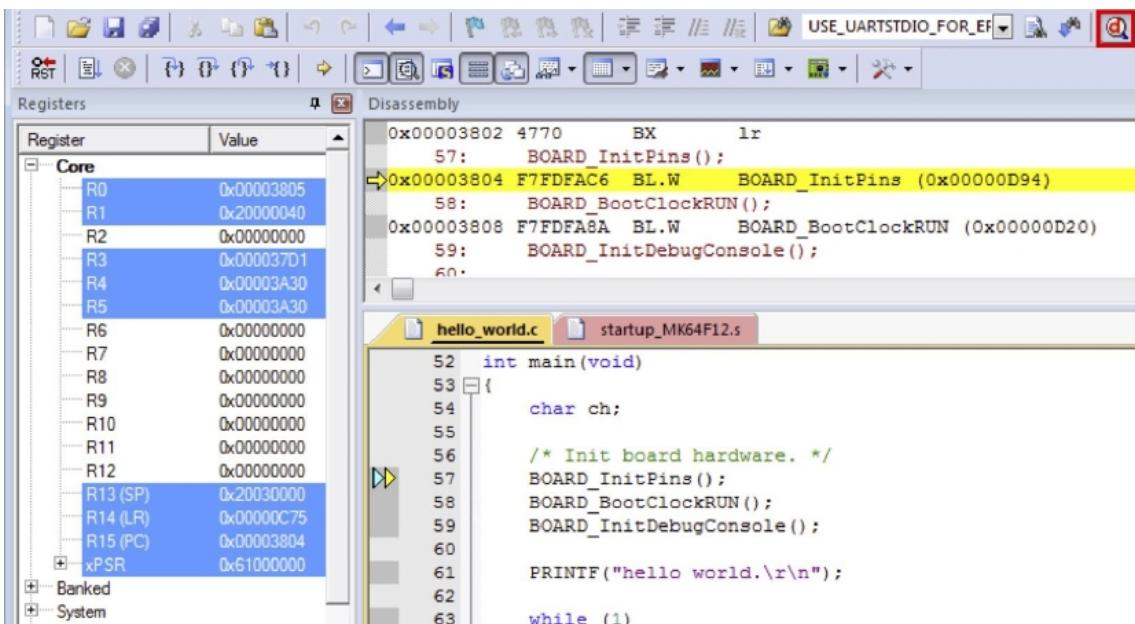

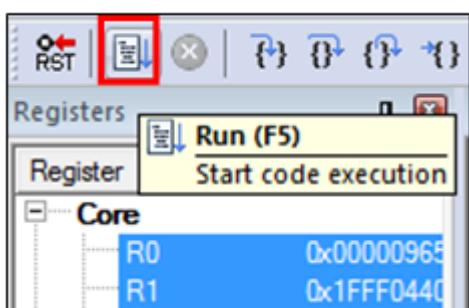

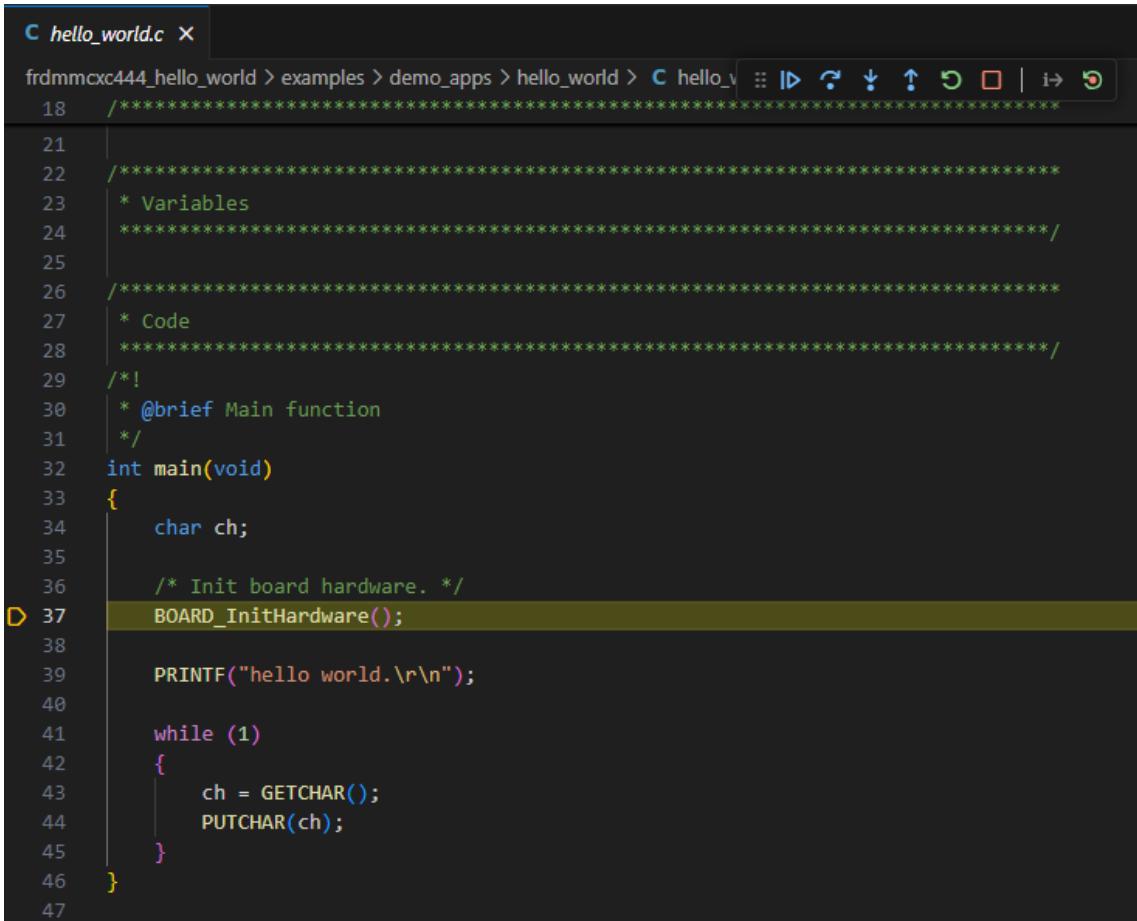

6. The application is downloaded to the target and automatically runs to `main()`.

7. Start the application by clicking **Resume**.

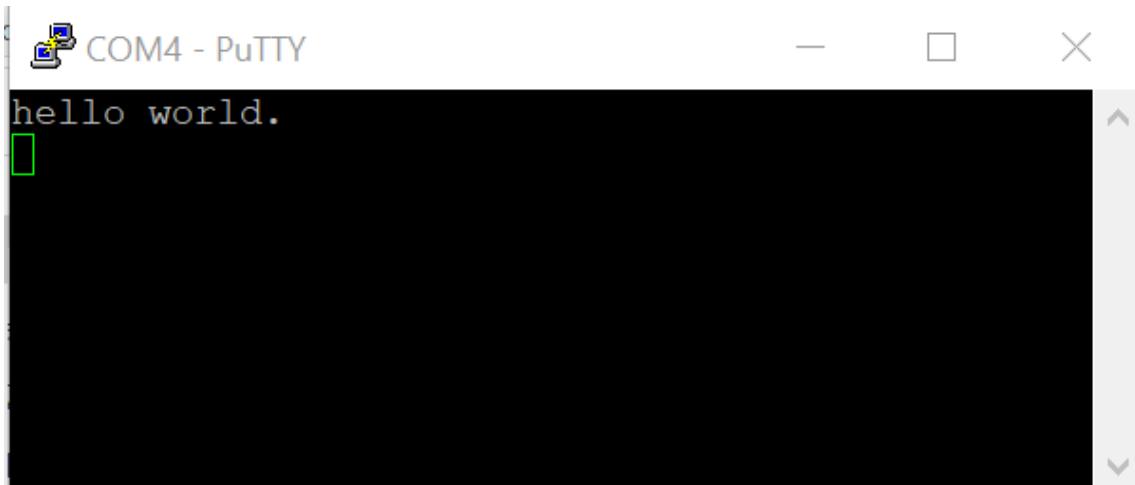

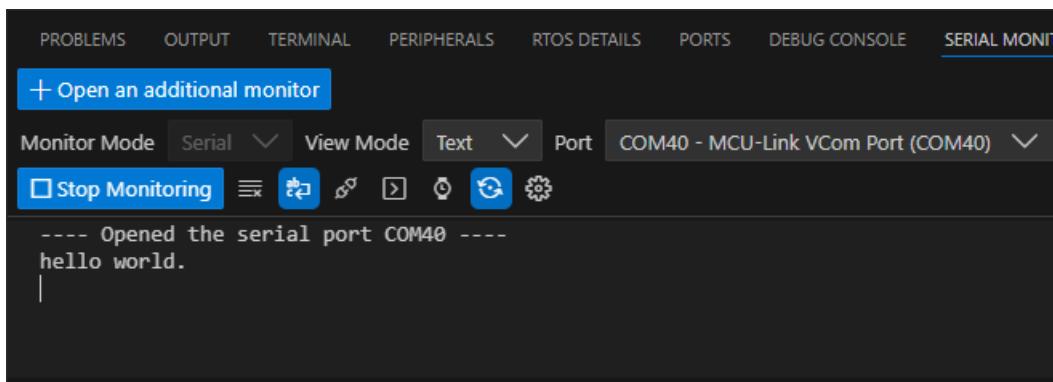

The `hello_world` application is now running and a banner is displayed on the terminal. If not, check your terminal settings and connections.

A screenshot of a PuTTY terminal window. The title bar says 'COM4 - PuTTY'. The main window is black with white text. It displays the message 'hello world.' followed by a small green square icon. There are scroll bars on the right side of the window.

**Build a multicore example application** This section describes the steps required to configure MCUXpresso IDE to build, run, and debug multicore example applications. The following steps can be applied to any multicore example application in the MCUXpresso SDK. Here, the dual-core version of hello\_world example application targeted for the LPCXpresso54114 hardware platform is used as an example.

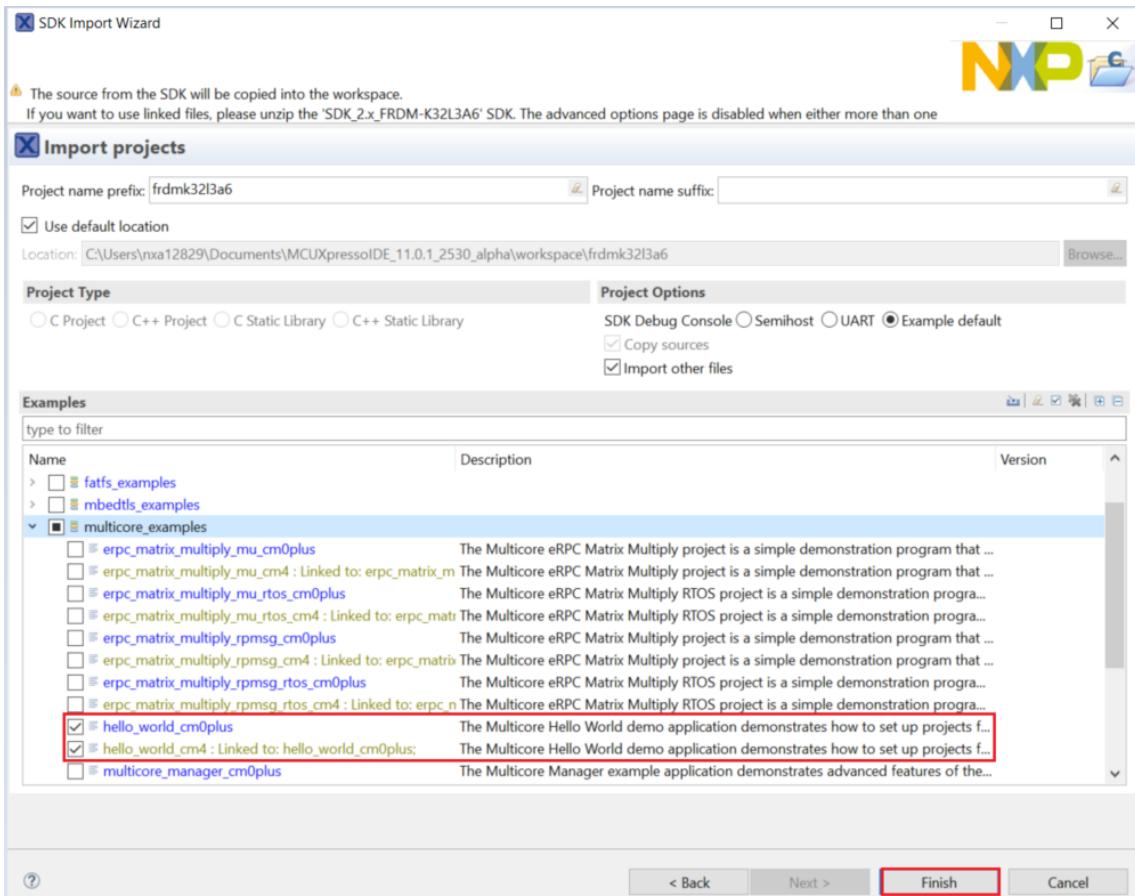

1. Multicore examples are imported into the workspace in a similar way as single core applications, explained in **Build an example application**. When the SDK zip package for LPCXpresso54114 is installed and available in the **Installed SDKs** view, click **Import SDK example(s)...** on the Quickstart Panel. In the window that appears, expand the **LPCxx** folder and select **LPC54114J256**. Then, select **lpcxpresso54114** and click **Next**.

2. Expand the multicore\_examples/hello\_world folder and select **cm4**. The cm0plus counterpart project is automatically imported with the cm4 project, because the multicore examples are linked together and there is no need to select it explicitly. Click **Finish**.

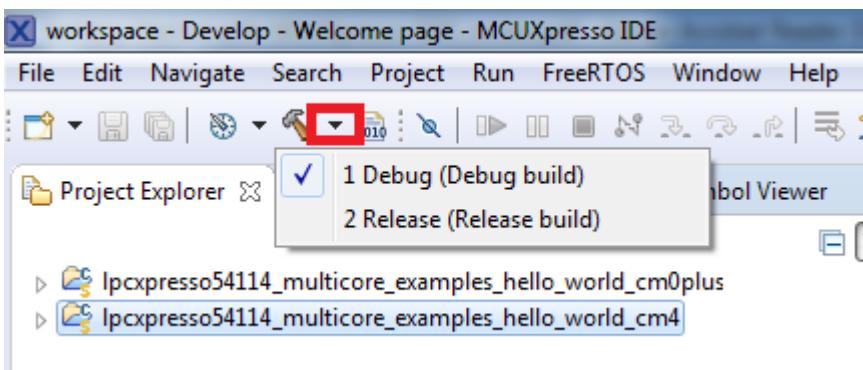

3. Now, two projects should be imported into the workspace. To start building the multicore application, highlight the `lpcxpresso54114_multicore_examples_hello_world_cm4` project (multicore master project) in the Project Explorer. Then choose the appropriate build target, **Debug** or **Release**, by clicking the downward facing arrow next to the hammer icon, as shown in the figure. For this example, select **Debug**.

The project starts building after the build target is selected. Because of the project reference settings in multicore projects, triggering the build of the primary core application (cm4) also causes the referenced auxiliary core application (cm0plus) to build.

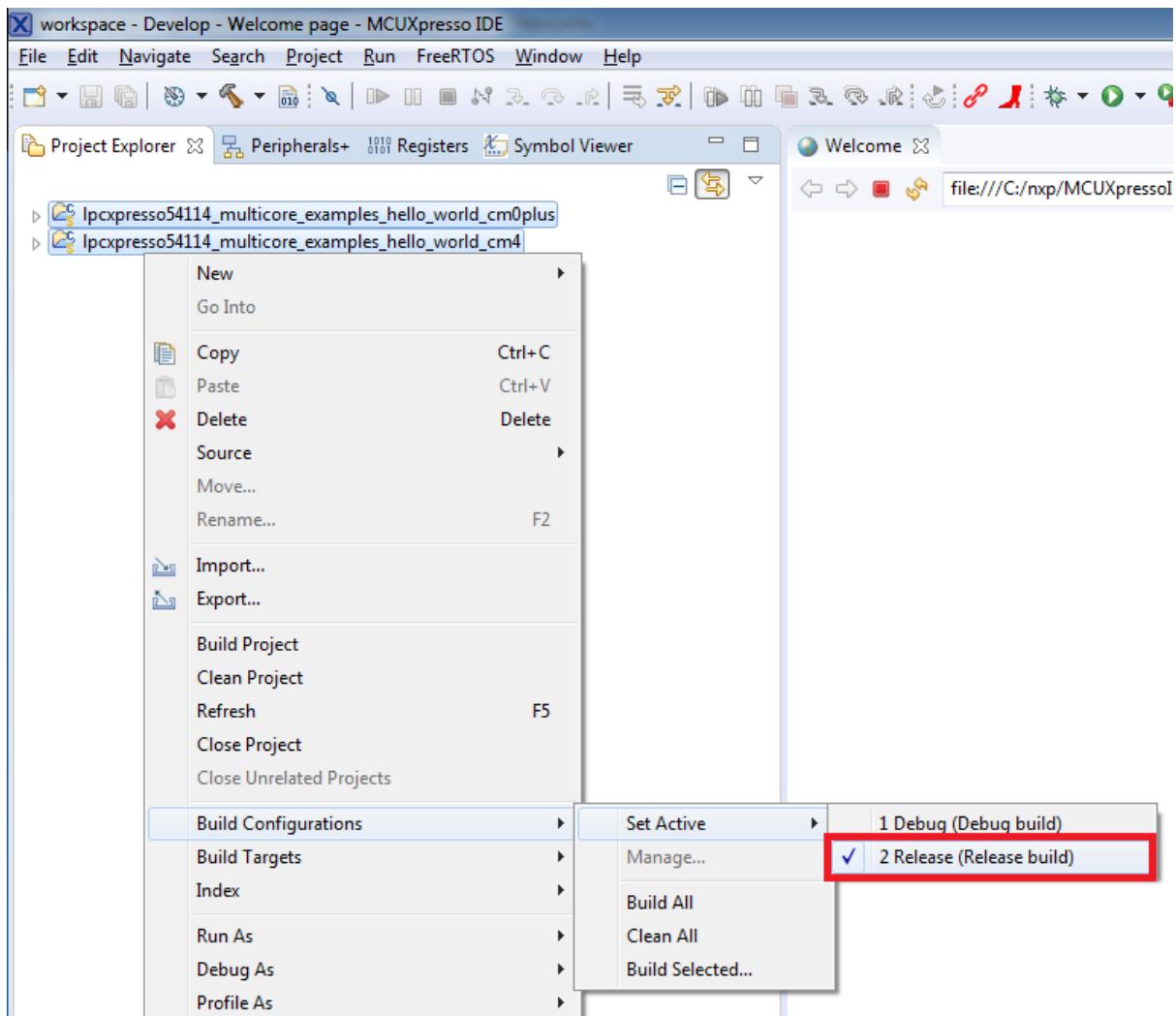

**Note:** When the **Release** build is requested, it is necessary to change the build configuration of both the primary and auxiliary core application projects first. To do this, select both projects in the Project Explorer view and then right click which displays the context-sensitive menu. Select **Build Configurations -> Set Active -> Release**. This alternate navigation using the menu item is **Project -> Build Configuration -> Set Active -> Release**. After switching to the **Release** build configuration, the build of the multicore example can be started by triggering the primary core application (cm4) build.

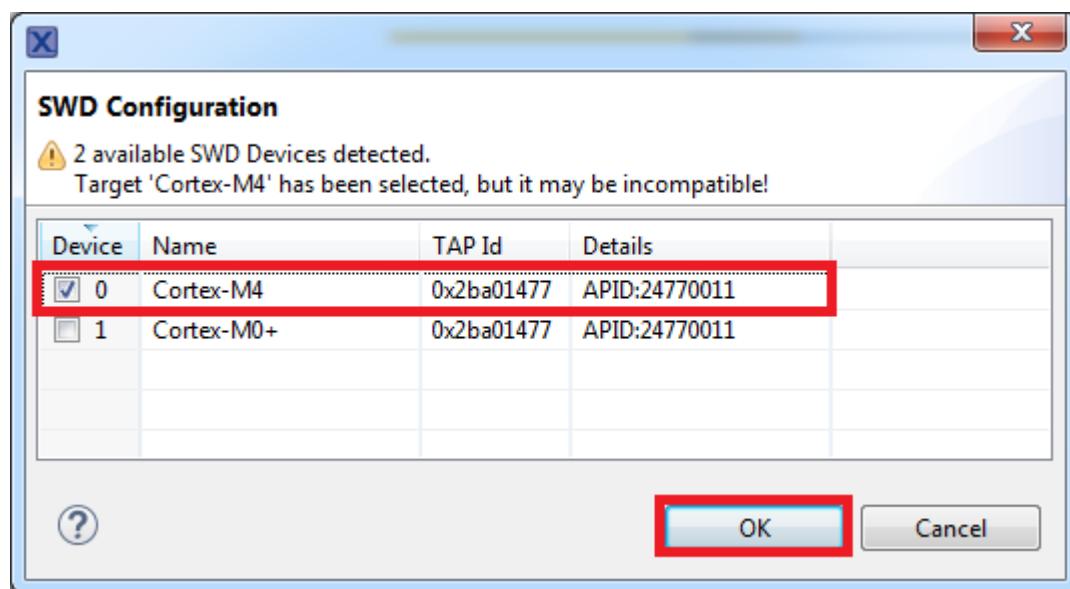

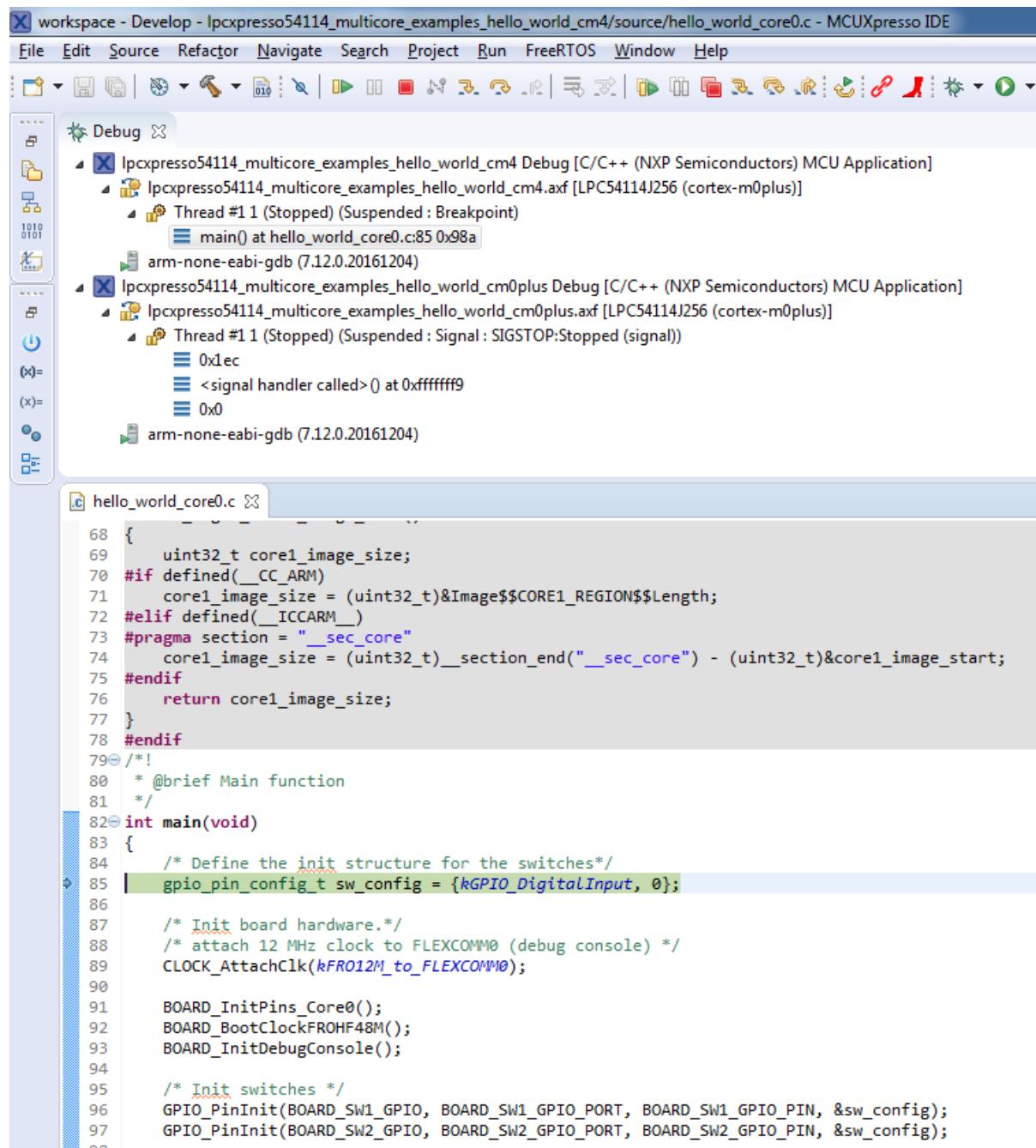

**Run a multicore example application** The primary core debugger handles flashing of both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform all steps as described in **Run an example application**. These steps are common for both single-core applications and the primary side of dual-core applications, ensuring both sides of the multicore application are properly loaded and started. However, there is one additional dialogue that is specific to multicore examples which requires selecting the target core. See the following figures as reference.

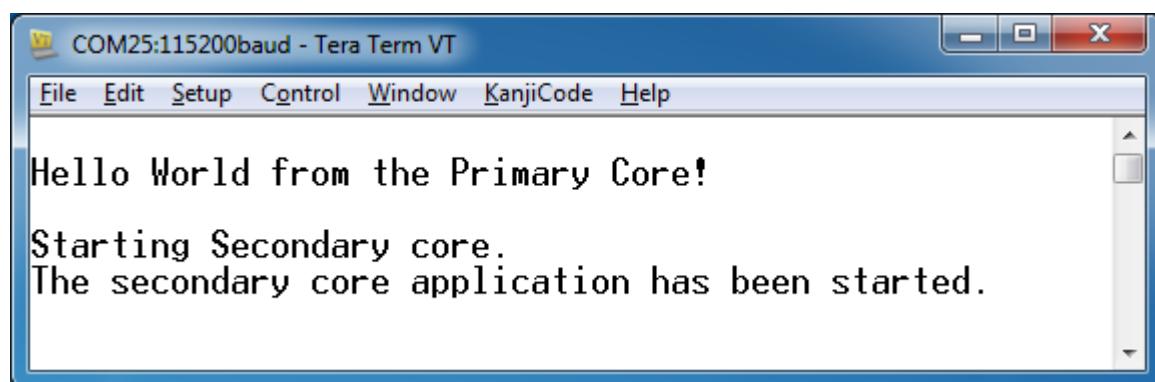

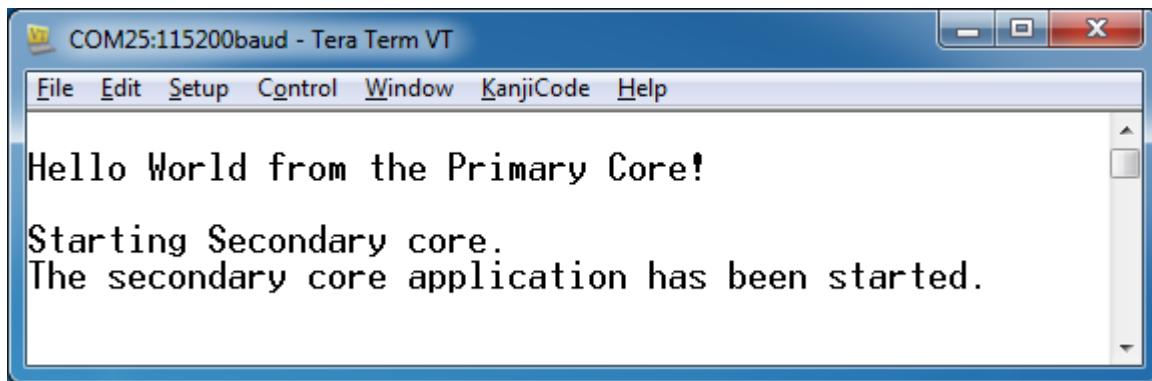

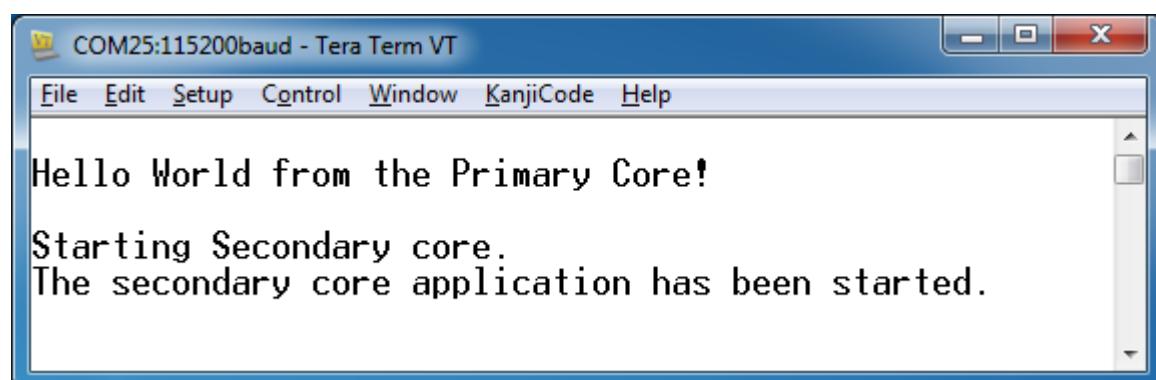

After clicking the “Resume All Debug sessions” button, the hello\_world multicore application runs and a banner is displayed on the terminal. If this is not the case, check your terminal settings and connections.

An LED controlled by the auxiliary core starts flashing, indicating that the auxiliary core has been released from the reset and running correctly. It is also possible to debug both sides of the multicore application in parallel. After creating the debug session for the primary core, perform same steps also for the auxiliary core application. Highlight the "lpcxpresso54114\_multicore\_examples\_hello\_world\_cm0plus" project (multicore slave project) in the Project Explorer. On the Quickstart Panel, click “Debug ‘lpcxpresso54114\_multicore\_examples\_hello\_world\_cm0plus’ [Debug]” to launch the second debug

session.

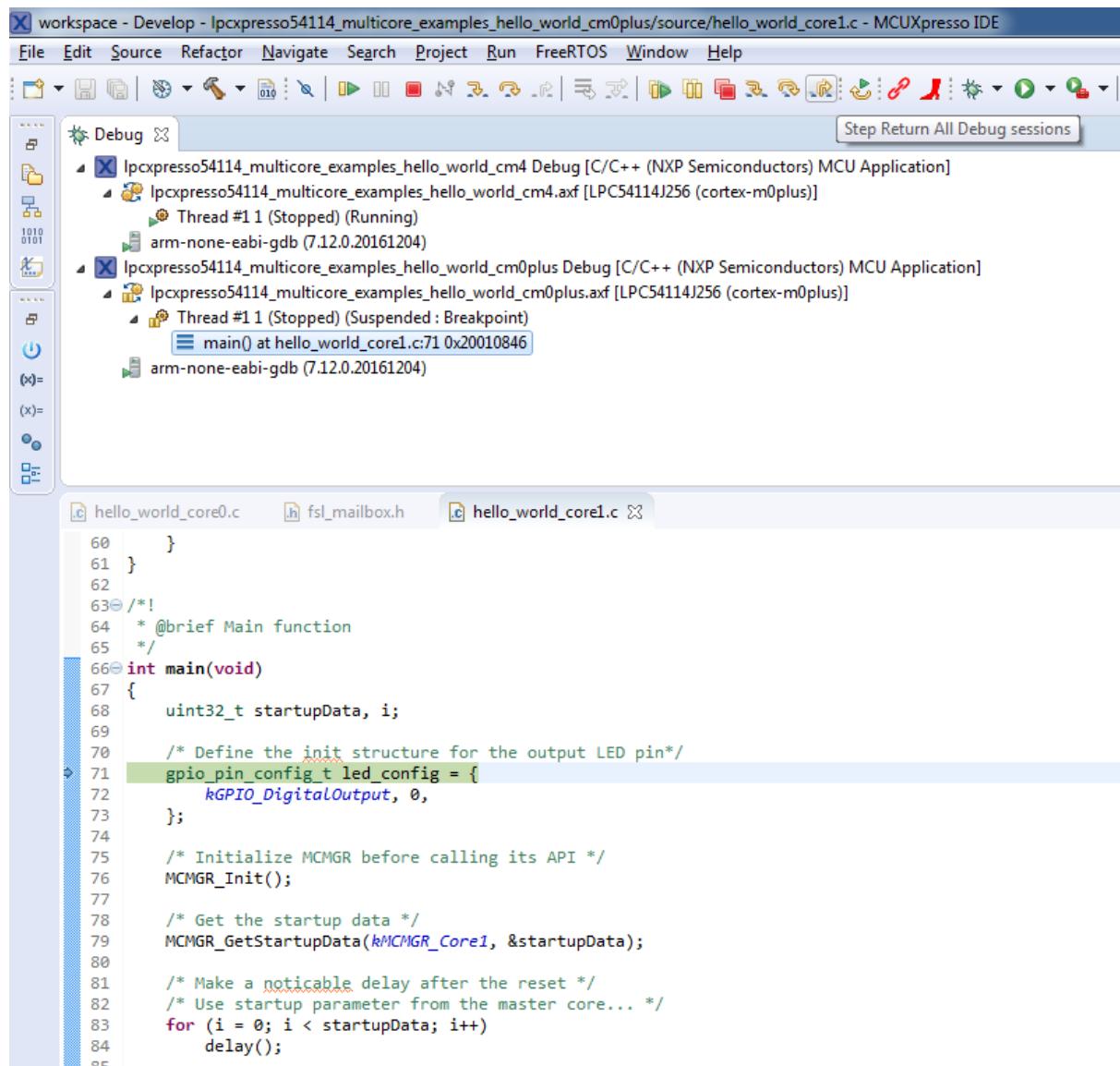

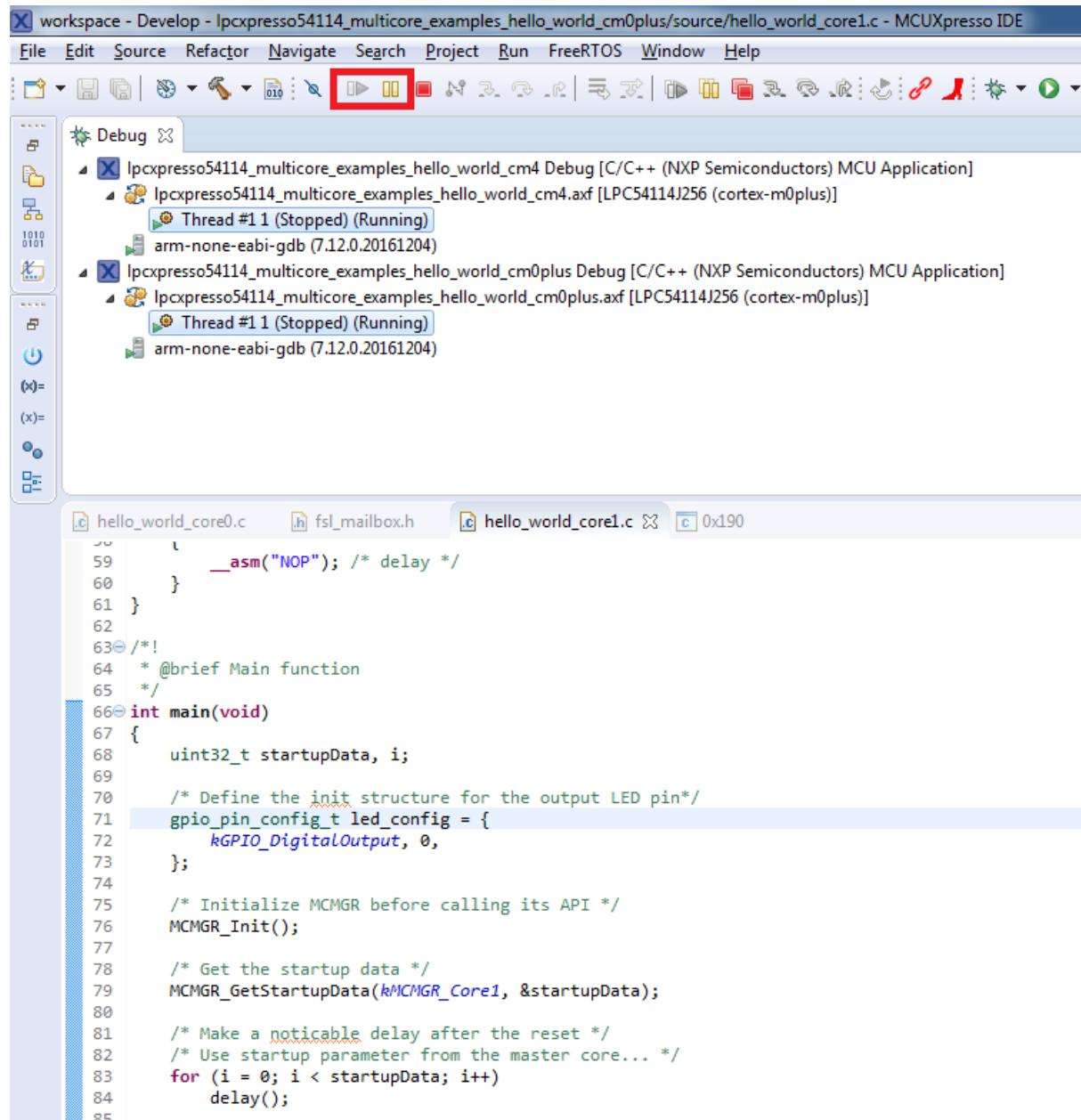

Now, the two debug sessions should be opened, and the debug controls can be used for both debug sessions depending on the debug session selection. Keep the primary core debug session selected by clicking the “Resume” button. The hello\_world multicore application then starts running. The primary core application starts the auxiliary core application during runtime, and the auxiliary core application stops at the beginning of the main() function. The debug session of the auxiliary core application is highlighted. After clicking the “Resume” button, it is applied to the auxiliary core debug session. Therefore, the auxiliary core application continues its execution.

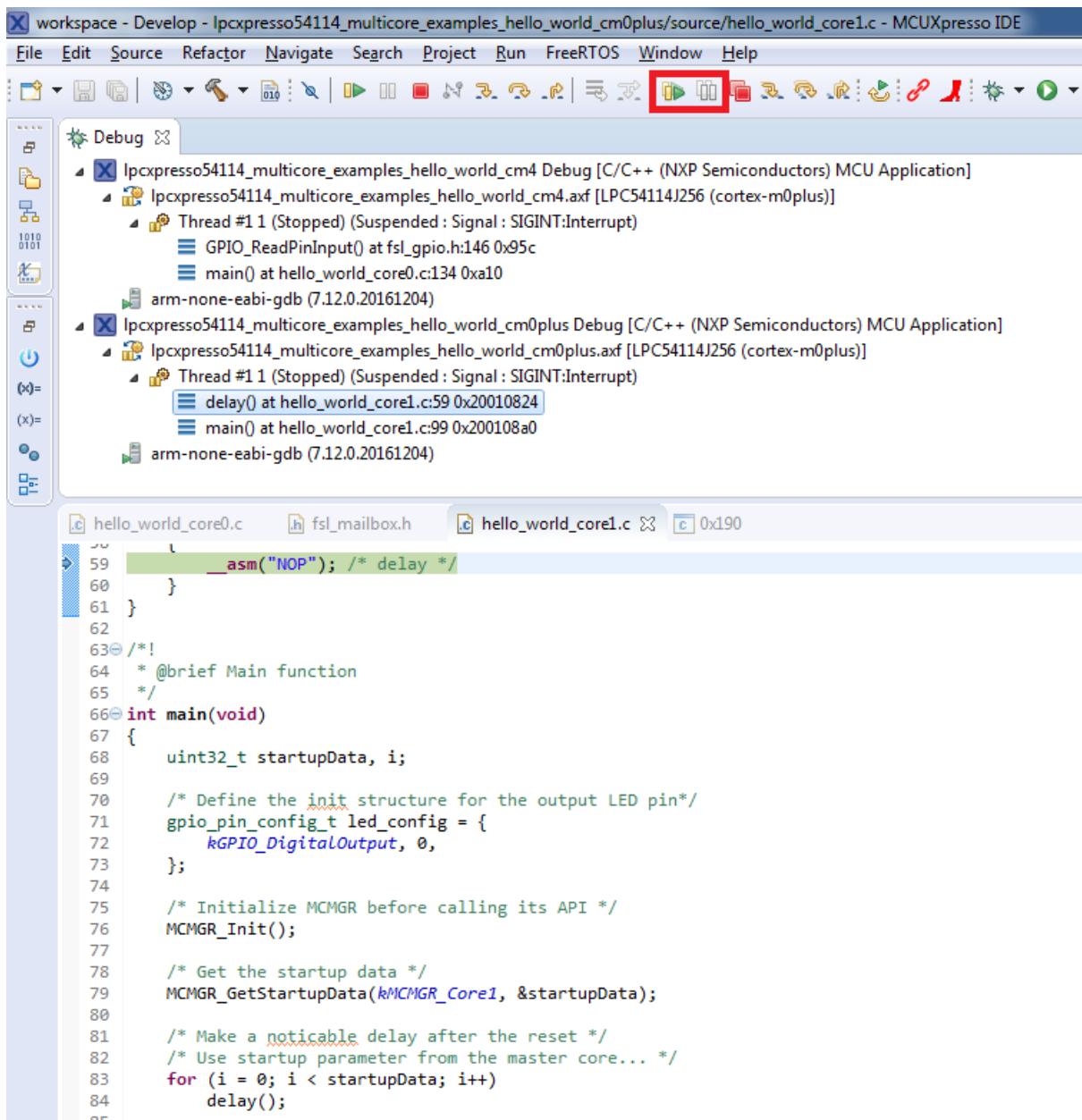

At this point, it is possible to suspend and resume individual cores independently. It is also possible to make synchronous suspension and resumption of both the cores. This is done either by selecting both opened debug sessions (multiple selections) and clicking the “Suspend” / “Resume” control button, or just using the “Suspend All Debug sessions” and the “Resume All Debug sessions” buttons.

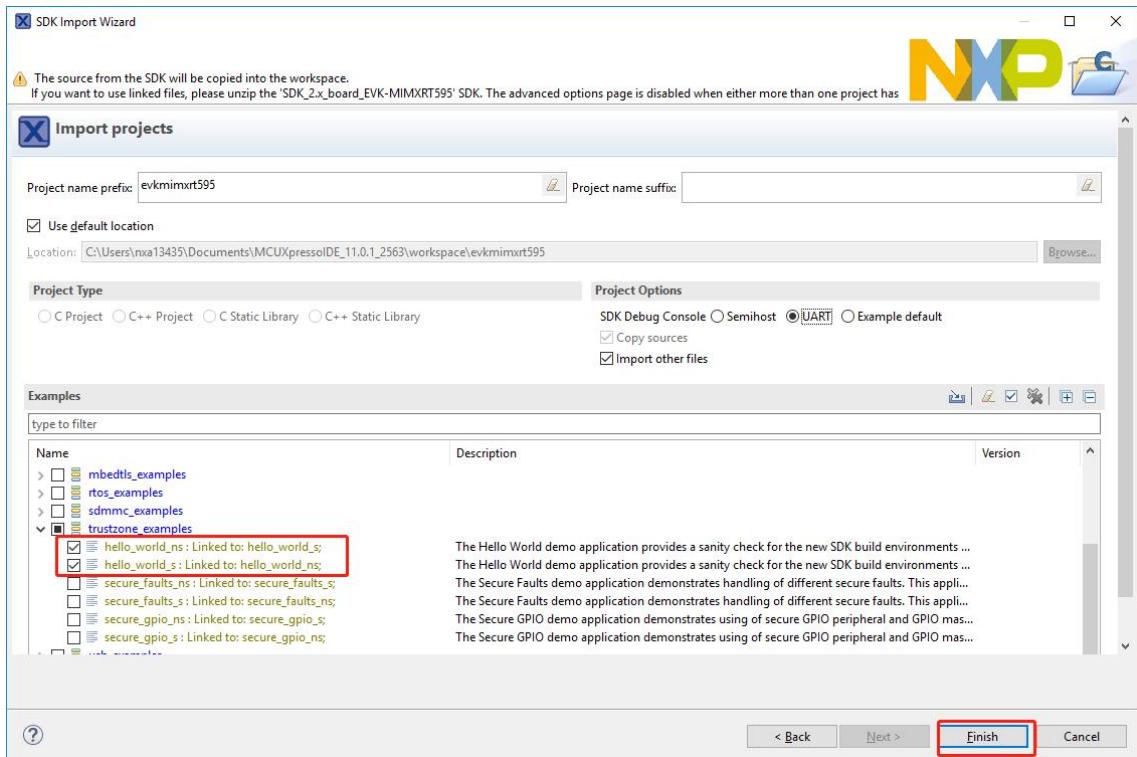

**Build a TrustZone example application** This section describes the steps required to configure MCUXpresso IDE to build, run, and debug TrustZone example applications. The TrustZone version of the hello\_world example application targeted for the MIMXRT595-EVK hardware platform is used as an example, though these steps can be applied to any TrustZone example application in the MCUXpresso SDK.

1. TrustZone examples are imported into the workspace in a similar way as single core applications. When the SDK zip package for MIMXRT595-EVK is installed and available in the **Installed SDKs** view, click **Import SDK example(s)...** on the Quickstart Panel. In the window that appears, expand the **MIMXRT500** folder and select **MIMXRT595**. Then, select **evkmimxrt595** and click **Next**.

2. Expand the **trustzone\_examples/** folder and select **hello\_world\_s**. Because TrustZone examples are linked together, the non-secure project is automatically imported with the secure project, and there is no need to select it explicitly. Then, click **Finish**.

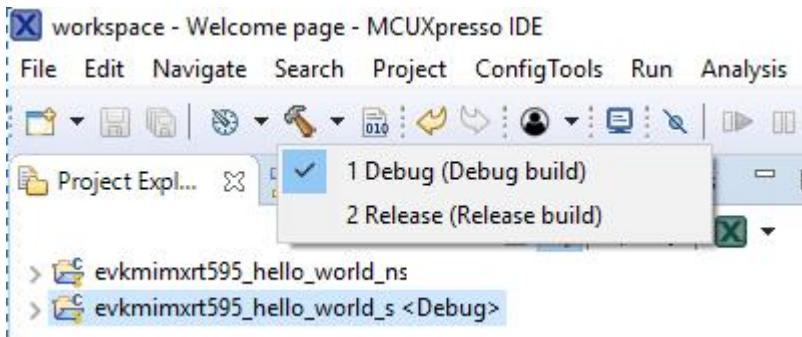

3. Now, two projects should be imported into the workspace. To start building the TrustZone application, highlight the evkmimxrt595\_hello\_world\_s project (TrustZone master project) in the Project Explorer. Then, choose the appropriate build target, **Debug** or **Release**, by clicking the downward facing arrow next to the hammer icon, as shown in following figure. For this example, select the **Debug** target.

The project starts building after the build target is selected. It is requested to build the application for the secure project first, because the non-secure project must know the secure project since CMSE library when running the linker. It is not possible to finish the non-secure project linker when the secure project since CMSE library is not ready.

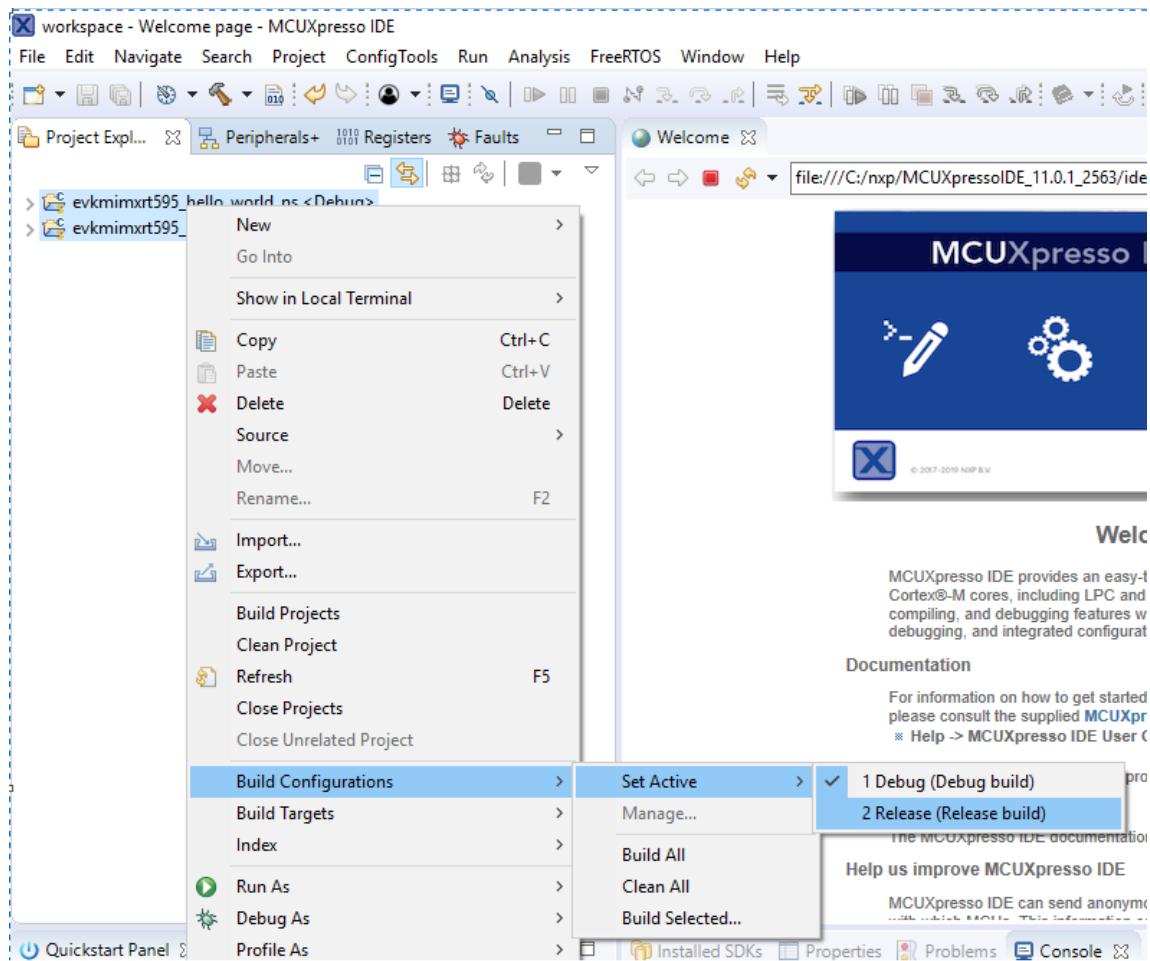

**Note:** When the **Release** build is requested, it is necessary to change the build configuration of both the secure and non-secure application projects first. To do this, select both projects in the Project Explorer view by clicking to select the first project, then using shift-click or control-click to select the second project. Right click in the Project Explorer view to display the context-sensitive menu and select **Build Configurations > Set Active > Release**. This is also possible by using the menu item of **Project > Build Configuration > Set Active > Release**. After switching to the **Release** build configuration. Build the application for the secure project first.

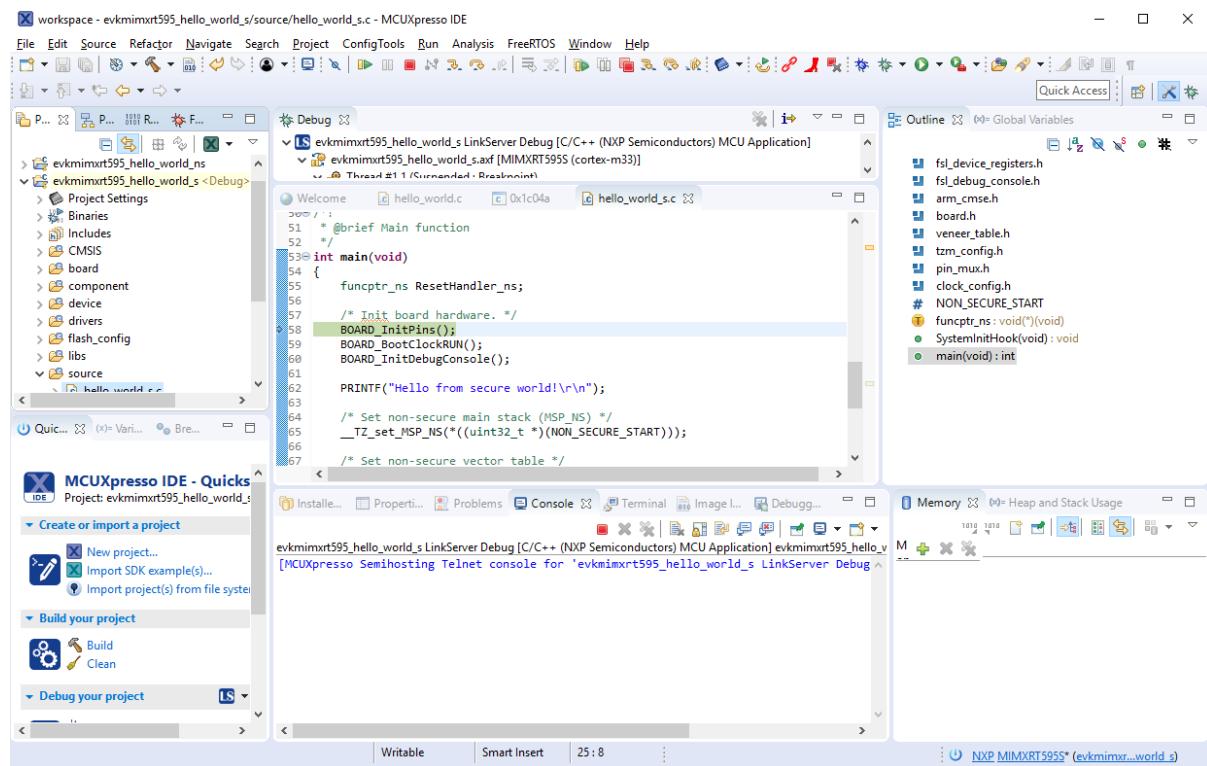

**Run a TrustZone example application** To download and run the application, perform all steps as described in **Run an example application**. These steps are common for single core, and TrustZone applications, ensuring <board\_name>\_hello\_world\_s is selected for debugging.

In the Quickstart Panel, click **Debug** to launch the second debug session.

Now, the TrustZone sessions should be opened. Click **Resume**. The hello\_world TrustZone application then starts running, and the secure application starts the non-secure application during runtime.

## Run a demo application using IAR

This section describes the steps required to build, run, and debug example applications provided in the MCUXpresso SDK.

**Note:** IAR Embedded Workbench for Arm version 8.32.3 is used in the following example, and the IAR toolchain should correspond to the latest supported version, as described in the *MCUXpresso SDK Release Notes*.

**Build an example application** Do the following steps to build the hello\_world example application.

1. Open the desired demo application workspace. Most example application workspace files can be located using the following path:

```

<install_dir>/boards/<board_name>/<example_type>/<application_name>/iar

```

Other example applications may have additional folders in their path.

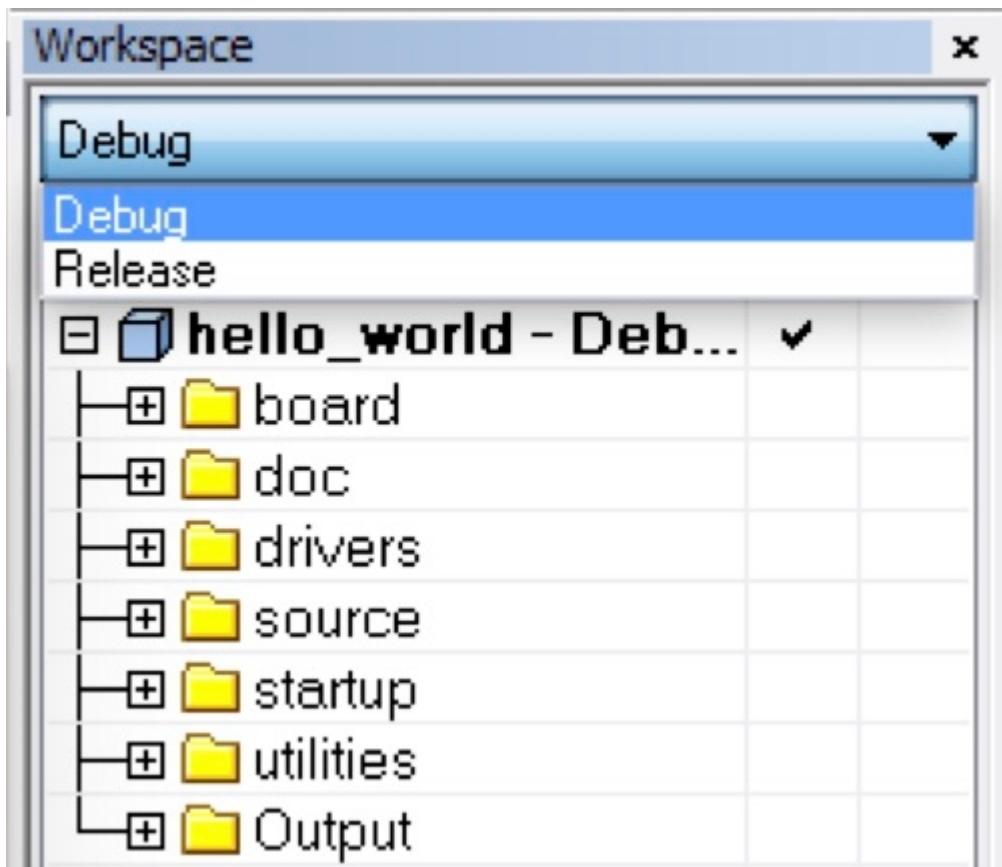

2. Select the desired build target from the drop-down menu.

For this example, select **hello\_world – debug**.

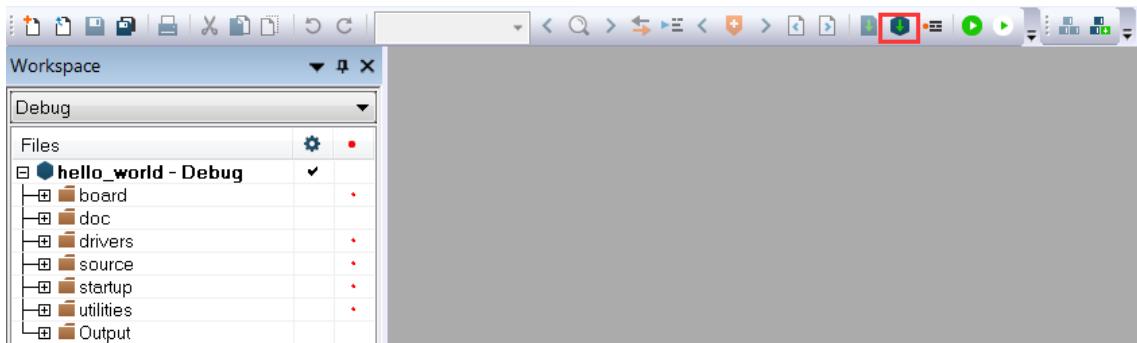

3. To build the demo application, click **Make**, highlighted in red in following figure.

4. The build completes without errors.

**Run an example application** To download and run the application, perform these steps:

1. Ensure the host driver for the debugger firmware has been installed. See [On-board debugger](#).

2. Connect the development platform to your PC via USB cable.

3. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug COM port (to determine the COM port number, see [How to determine COM port](#)). Configure the terminal with these settings:

1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in the board.h file)

2. No parity

3. 8 data bits

4. In IAR, click the **Download and Debug** button to download the application to the target.

5. The application is then downloaded to the target and automatically runs to the main() function.

6. Run the code by clicking the **Go** button.

7. The hello\_world application is now running and a banner is displayed on the terminal. If it does not appear, check your terminal settings and connections.

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo applications workspace files are located in this folder:

```

<install_dir>/boards/<board_name>/multicore_examples/<application_name>/<core_type>/iar

```

Begin with a simple dual-core version of the Hello World application. The multicore Hello World IAR workspaces are located in this folder:

```

<install_dir>/boards/lpcexpresso54114/multicore_examples/hello_world/cm0plus/iar/hello_world_cm0plus.eww

```

```

<install_dir>/boards/lpcexpresso54114/multicore_examples/hello_world/cm4/iar/hello_world_cm4.eww

```

Build both applications separately by clicking the **Make** button. Build the application for the auxiliary core (cm0plus) first, because the primary core application project (cm4) must know the auxiliary core application binary when running the linker. It is not possible to finish the primary core linker when the auxiliary core application binary is not ready.

**Run a multicore example application** The primary core debugger handles flashing both primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1 – 4 as described in **Run an example application**. These steps are common for both single core and dual-core applications in IAR.

After clicking the “Download and Debug” button, the auxiliary core project is opened in the separate EWARM instance. Both the primary and auxiliary images are loaded into the device flash memory and the primary core application is executed. It stops at the default C language entry point in the `*main()*`function.

Run both cores by clicking the “Start all cores” button to start the multicore application.

During the primary core code execution, the auxiliary core is released from the reset. The hello\_world multicore application is now running and a banner is displayed on the terminal. If this does not appear, check the terminal settings and connections.

An LED controlled by the auxiliary core starts flashing, indicating that the auxiliary core has been released from the reset and is running correctly. When both cores are running, use the “Stop all cores”, and “Start all cores” control buttons to stop or run both cores simultaneously.

**Build a TrustZone example application** This section describes the particular steps that must be done in order to build and run a TrustZone application. The demo applications workspace files are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/[<core_type>]/iar/

↪<application_name>_ns/iar

```

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/[<core_type>]/iar/

↪<application_name>_s/iar

```

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World IAR workspaces are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_ns/iar/hello_world_

↪ns.eww

```

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_s/iar/hello_world_s.

↪eww

```

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_s/iar/hello_world.eww

```

This project hello\_world.eww contains both secure and non-secure projects in one workspace and it allows the user to easily transition from one project to another. Build both applications separately by clicking **Make**. It is requested to build the application for the secure project first, because the non-secure project must know the secure project, since the CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project since CMSE library is not ready.

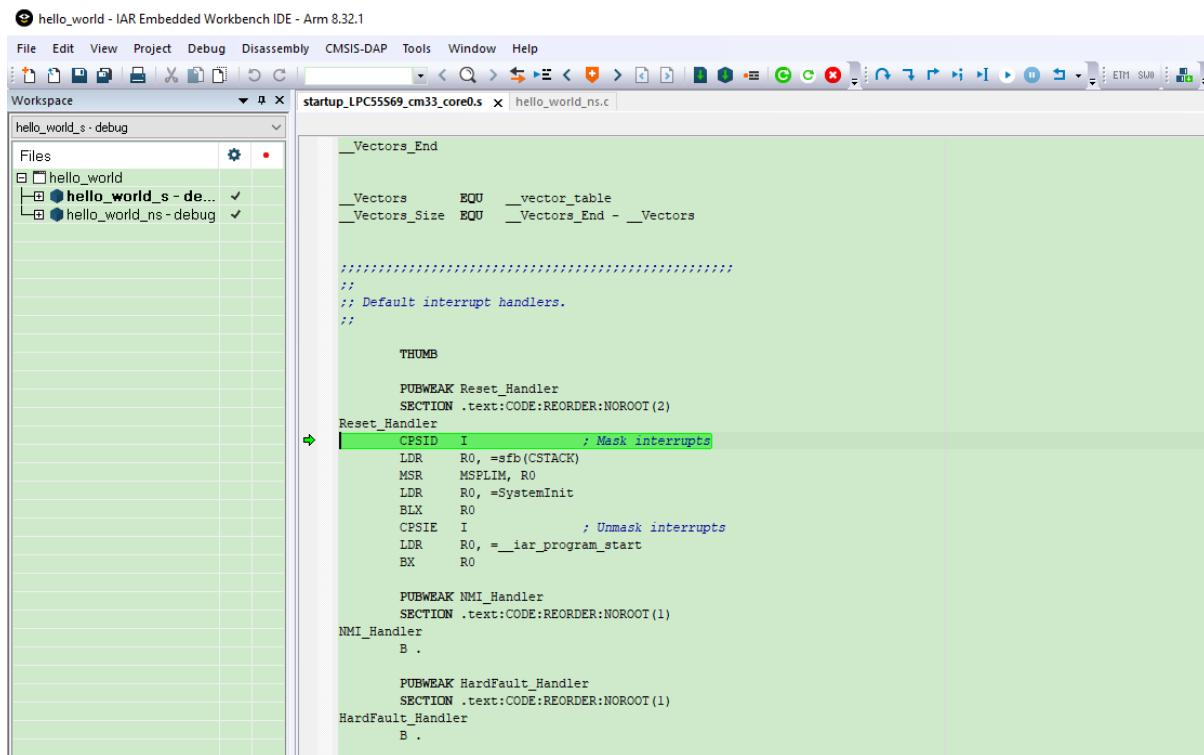

**Run a TrustZone example application** The secure project is configured to download both secure and non-secure output files, so debugging can be fully managed from the secure project. To download and run the TrustZone application, switch to the secure application project and perform steps 1 – 4 as described in **Run an example application**. These steps are common for both single core, and TrustZone applications in IAR. After clicking **Download and Debug**, both the secure and non-secure images are loaded into the device memory, and the secure application is executed. It stops at the `Reset_Handler` function.

```

__Vectors_End

__Vectors EQU __vector_table

__Vectors_Size EQU __Vectors_End - __Vectors

;;;;; Default interrupt handlers.

THUMB

PUBWEAK Reset_Handler

SECTION .text:CODE:REORDER:NOROOT(2)

Reset_Handler

CPSID I ; Mask interrupts

LDR R0, =sfb(CSTACK)

MSR MSPLIM, R0

LDR R0, =SystemInit

BLX R0

CPSIE I ; Unmask interrupts

LDR R0, =_iar_program_start

BX R0

PUBWEAK NMI_Handler

SECTION .text:CODE:REORDER:NOROOT(1)

NMI_Handler

B .

PUBWEAK HardFault_Handler

SECTION .text:CODE:REORDER:NOROOT(1)

HardFault_Handler

B .

```

Run the code by clicking **Go** to start the application.

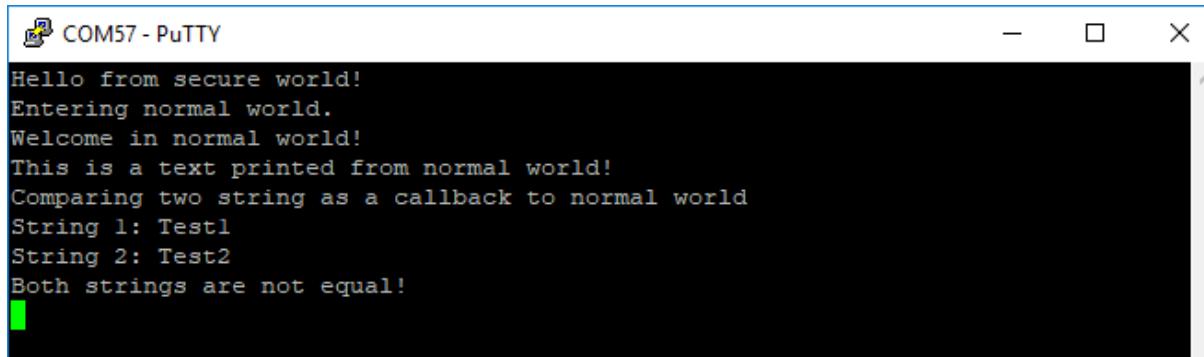

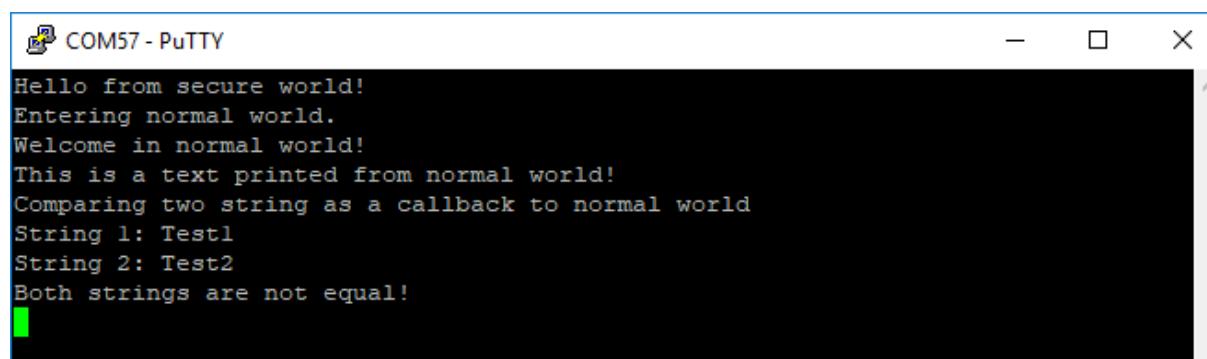

The TrustZone hello\_world application is now running and a banner is displayed on the terminal. If this is not true, check your terminal settings and connections.

```

Hello from secure world!

Entering normal world.

Welcome in normal world!

This is a text printed from normal world!

Comparing two string as a callback to normal world

String 1: Test1

String 2: Test2

Both strings are not equal!

```

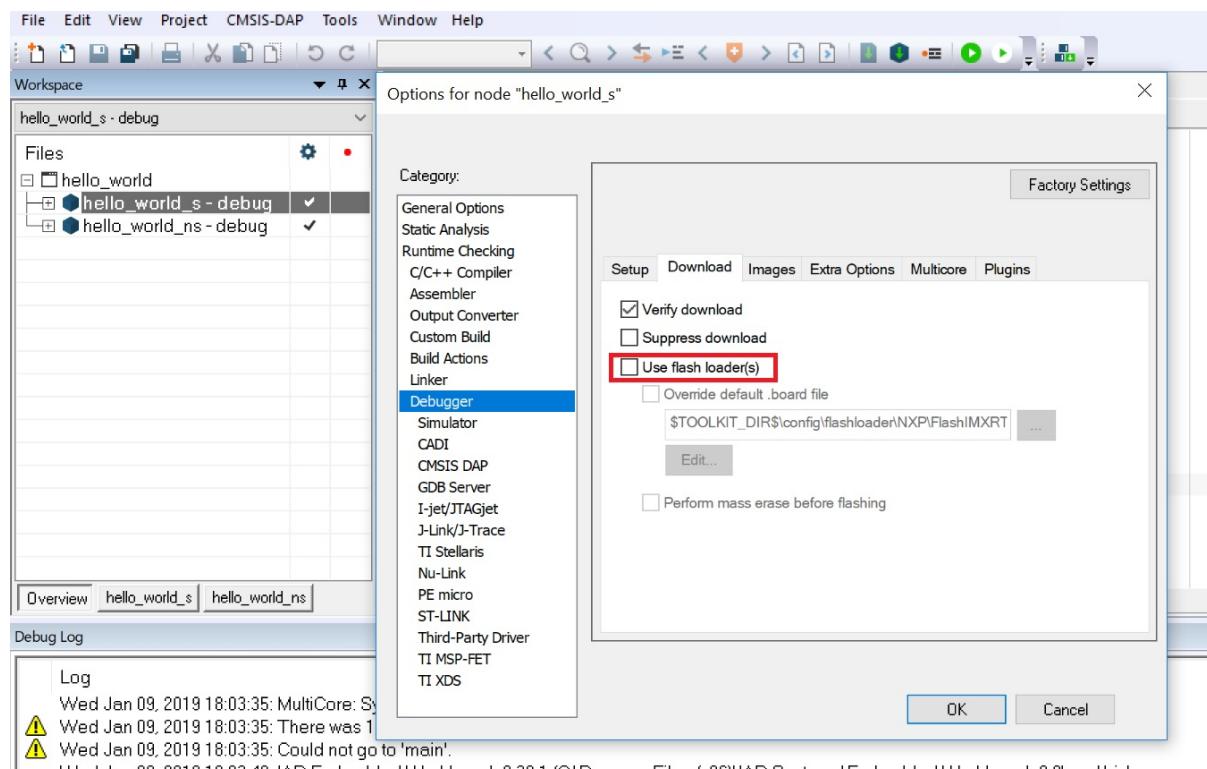

**Note:** If the application is running in RAM (debug/release build target), in **Options**\*\*>\*\***Debugger** > **Download** tab, disable **Use flash loader(s)**. This can avoid the `_ns` download issue on i.MXRT500.

## Run a demo using Keil MDK/μVision

This section describes the steps required to build, run, and debug example applications provided in the MCUXpresso SDK.

**Install CMSIS device pack** After the MDK tools are installed, Cortex Microcontroller Software Interface Standard (CMSIS) device packs must be installed to fully support the device from a debug perspective. These packs include things such as memory map information, register definitions, and flash programming algorithms. Follow these steps to install the appropriate CMSIS pack.

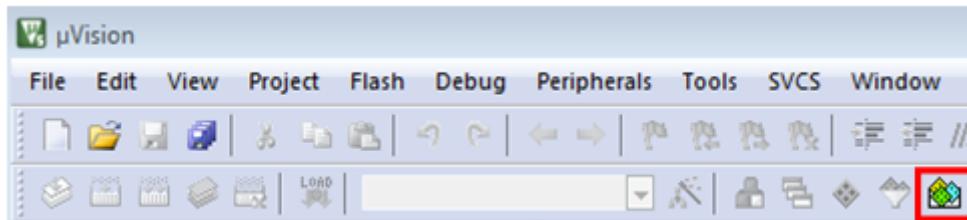

1. Open the MDK IDE, which is called μVision. In the IDE, select the **Pack Installer** icon.

2. After the installation finishes, close the Pack Installer window and return to the μVision IDE.

## Build an example application

1. Open the desired example application workspace in:

```

<install_dir>/boards/<board_name>/<example_type>/<application_name>/mdk

```

The workspace file is named as <demo\_name>.uvmpw. For this specific example, the actual path is:

2. To build the demo project, select **Rebuild**, highlighted in red.

3. The build completes without errors.

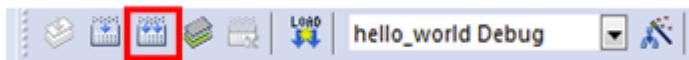

**Run an example application** To download and run the application, perform these steps:

1. Ensure the host driver for the debugger firmware has been installed. See [On-board debugger](#).

2. Connect the development platform to your PC via USB cable using USB connector.

3. Open the terminal application on the PC, such as PuTTY or TeraTerm and connect to the debug serial port number (to determine the COM port number, see [How to determine COM port](#)). Configure the terminal with these settings:

1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in the board.h file)

2. No parity

3. 8 data bits

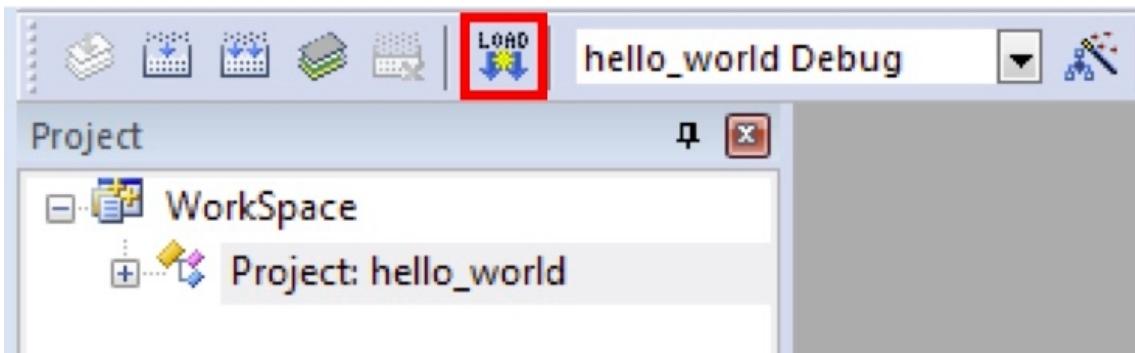

4. In μVision, after the application is built, click the **Download** button to download the application to the target.

5. After clicking the **Download** button, the application downloads to the target and is running. To debug the application, click the **Start/Stop Debug Session** button, highlighted in red.

6. Run the code by clicking the **Run** button to start the application.

The hello\_world application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo applications workspace files are located in this folder:

```

<install_dir>/boards/<board_name>/multicore_examples/<application_name>/<core_type>/mdk

```

Begin with a simple dual-core version of the Hello World application. The multicore Hello World Keil MSDK/μVision workspaces are located in this folder:

```

<install_dir>/boards/lpcxpresso54114/multicore_examples/hello_world/cm0plus/mdk/hello_world_

→cm0plus.uvmpw

```

```

<install_dir>/boards/lpcxpresso54114/multicore_examples/hello_world/cm4/mdk/hello_world_cm4.uvmpw

```

Build both applications separately by clicking the **Rebuild** button. Build the application for the auxiliary core (cm0plus) first because the primary core application project (cm4) must know the auxiliary core application binary when running the linker. It is not possible to finish the primary core linker when the auxiliary core application binary is not ready.

**Run a multicore example application** The primary core debugger flashes both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1 – 5 as described in **Run an example application**. These steps are common for both single-core and dual-core applications in μVision.

Both the primary and the auxiliary image is loaded into the device flash memory. After clicking the “Run” button, the primary core application is executed. During the primary core code execution, the auxiliary core is released from the reset. The hello\_world multicore application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

An LED controlled by the auxiliary core starts flashing indicating that the auxiliary core has been released from the reset and is running correctly.

Attach the running application of the auxiliary core by opening the auxiliary core project in the second µVision instance and clicking the “Start/Stop Debug Session” button. After this, the second debug session is opened and the auxiliary core application can be debugged.

Arm describes multicore debugging using the NXP LPC54114 Cortex-M4/M0+ dual-core processor and Keil uVision IDE in Application Note 318 at [www.keil.com/appnotes/docs/apnt\\_318.asp](http://www.keil.com/appnotes/docs/apnt_318.asp). The associated video can be found [here](#).

**Build a TrustZone example application** This section describes the particular steps that must be done in order to build and run a TrustZone application. The demo applications workspace files are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/<application_name>_ns/

↳ mdk

```

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/<application_name>_s/

↳ mdk

```

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World Keil MSDK/µVision workspaces are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_ns/mdk/hello_world_-

↳ ns.uvmpw

```

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_s/mdk/hello_world_-

↳ uvmpw

```

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_s/mdk/hello_world.uvmpw

```

This project hello\_world.uvmpw contains both secure and non-secure projects in one workspace and it allows the user to easily transition from one project to another.

Build both applications separately by clicking **Rebuild**. It is requested to build the application for the secure project first, because the non-secure project must know the secure project since CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project because CMSE library is not ready.

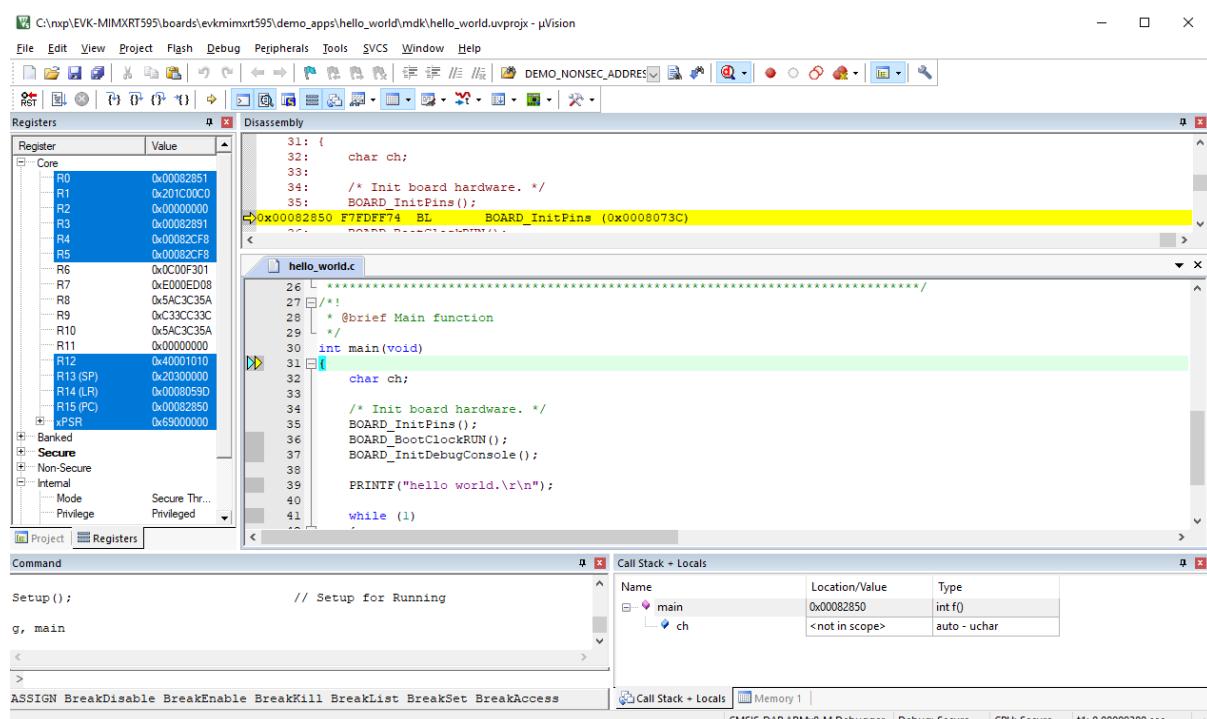

**Run a TrustZone example application** The secure project is configured to download both secure and non-secure output files so debugging can be fully managed from the secure project.

To download and run the TrustZone application, switch to the secure application project and perform steps as described in **Run an example application**. These steps are common for single core, dual-core, and TrustZone applications in  $\mu$ Vision. After clicking **Download and Debug**, both the secure and non-secure images are loaded into the device flash memory, and the secure application is executed. It stops at the main() function.

Run the code by clicking **Run** to start the application.

The hello\_world application is now running and a banner is displayed on the terminal. If not, check your terminal settings and connections.

## Run a demo using Arm GCC

This section describes the steps to configure the command-line Arm GCC tools to build, run, and debug demo applications and necessary driver libraries provided in the MCUXpresso SDK. The hello\_world demo application is targeted which is used as an example.

**Set up toolchain** This section contains the steps to install the necessary components required to build and run an MCUXpresso SDK demo application with the Arm GCC toolchain, as supported by the MCUXpresso SDK. There are many ways to use Arm GCC tools, but this example focuses on a Windows operating system environment.

**Install GCC Arm Embedded tool chain** Download and run the installer from GNU Arm Embedded Toolchain. This is the actual toolset (in other words, compiler, linker, and so on). The GCC toolchain should correspond to the latest supported version, as described in [MCUXpresso SDK Release Notes](#).

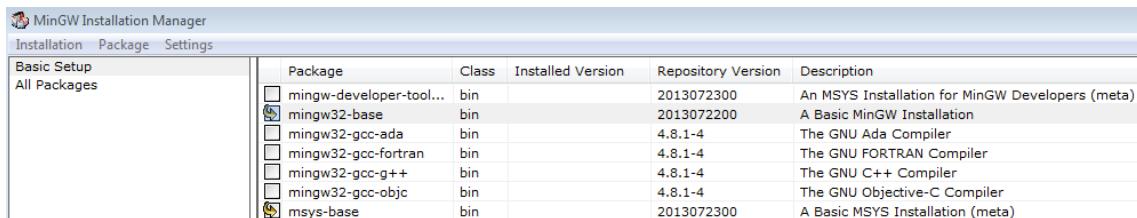

**Install MinGW (only required on Windows OS)** The Minimalist GNU for Windows (MinGW) development tools provide a set of tools that are not dependent on third-party C-Runtime DLLs (such as Cygwin). The build environment used by the MCUXpresso SDK does not use the MinGW build tools, but does leverage the base install of both MinGW and MSYS. MSYS provides a basic shell with a Unix-like interface and tools.

1. Download the latest MinGW mingw-get-setup installer from [MinGW](#).

2. Run the installer. The recommended installation path is C:\MinGW, however, you may install to any location.

**Note:** The installation path cannot contain any spaces.

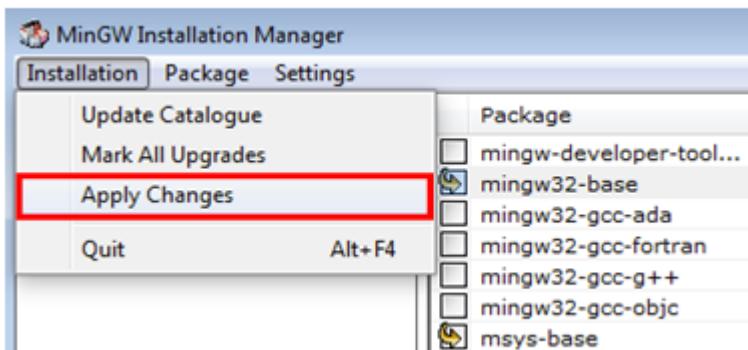

3. Ensure that the **mingw32-base** and **msys-base** are selected under **Basic Setup**.

4. In the **Installation** menu, click **Apply Changes** and follow the remaining instructions to complete the installation.

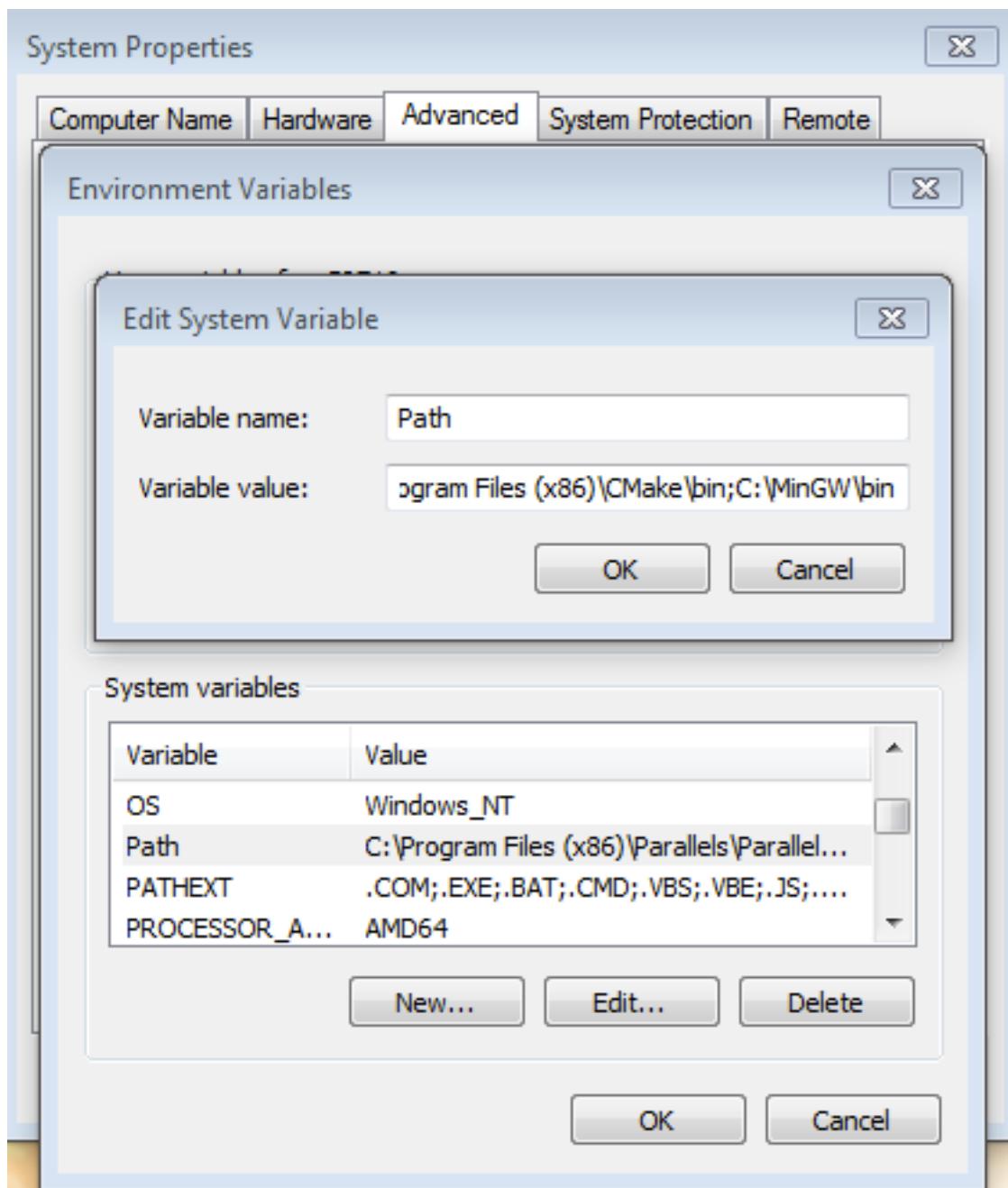

5. Add the appropriate item to the Windows operating system path environment variable. It can be found under **Control Panel->System and Security->System->Advanced System Settings** in the **Environment Variables...** section. The path is:

<mingw\_install\_dir>\bin

Assuming the default installation path, C:\MinGW, an example is shown below. If the path is not set correctly, the toolchain will not work.

**Note:** If you have C:\MinGW\msys\x.x\bin in your PATH variable (as required by Kinetis SDK 1.0.0), remove it to ensure that the new GCC build system works correctly.

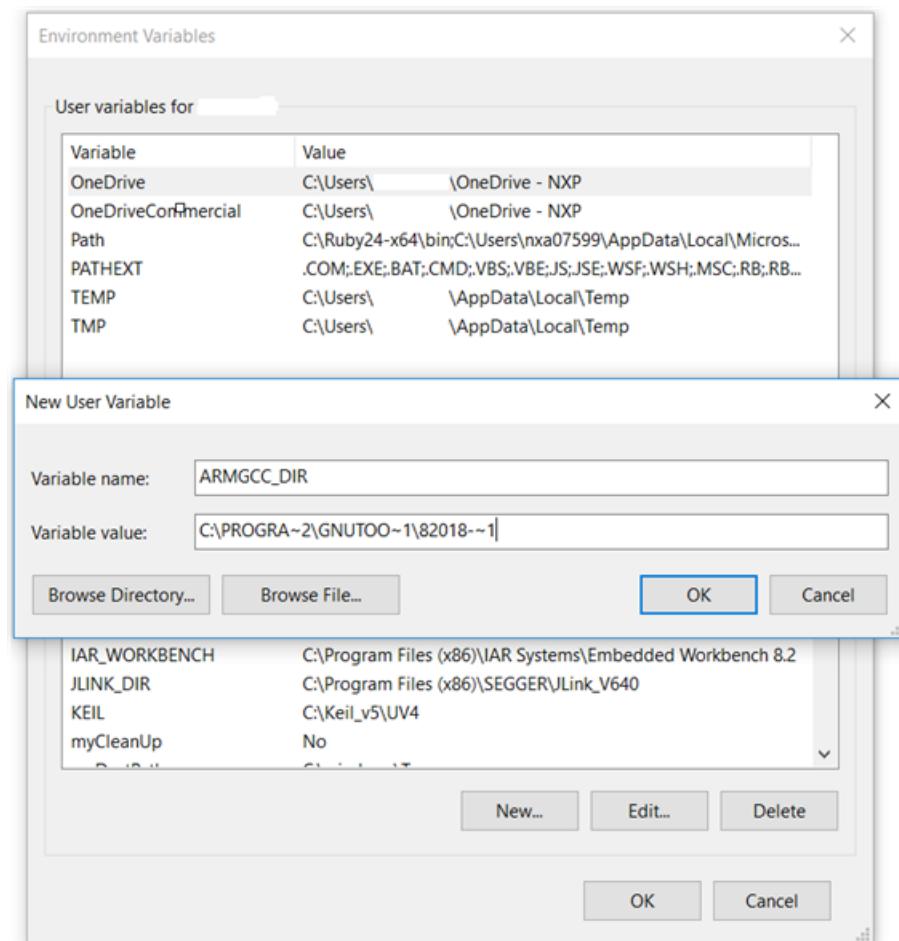

**Add a new system environment variable for ARMGCC\_DIR** Create a new *system* environment variable and name it as ARMGCC\_DIR. The value of this variable should point to the Arm GCC Embedded tool chain installation path. For this example, the path is:

C:\Program Files (x86)\GNU Tools\Arm Embedded\8 2018-q4-major

See the installation folder of the GNU Arm GCC Embedded tools for the exact pathname of your installation.

Short path should be used for path setting, you could convert the path to short path by running command for %I in (.) do echo %~sI in above path.

```

C:\Program Files (x86)\GNU Tools Arm Embedded\8 2018-q4-major>for %I in (.) do echo %~sI

C:\Program Files (x86)\GNU Tools Arm Embedded\8 2018-q4-major>echo C:\PROGRA~2\GNUTOO~1\82018~1

```

## Install CMake

### Windows OS

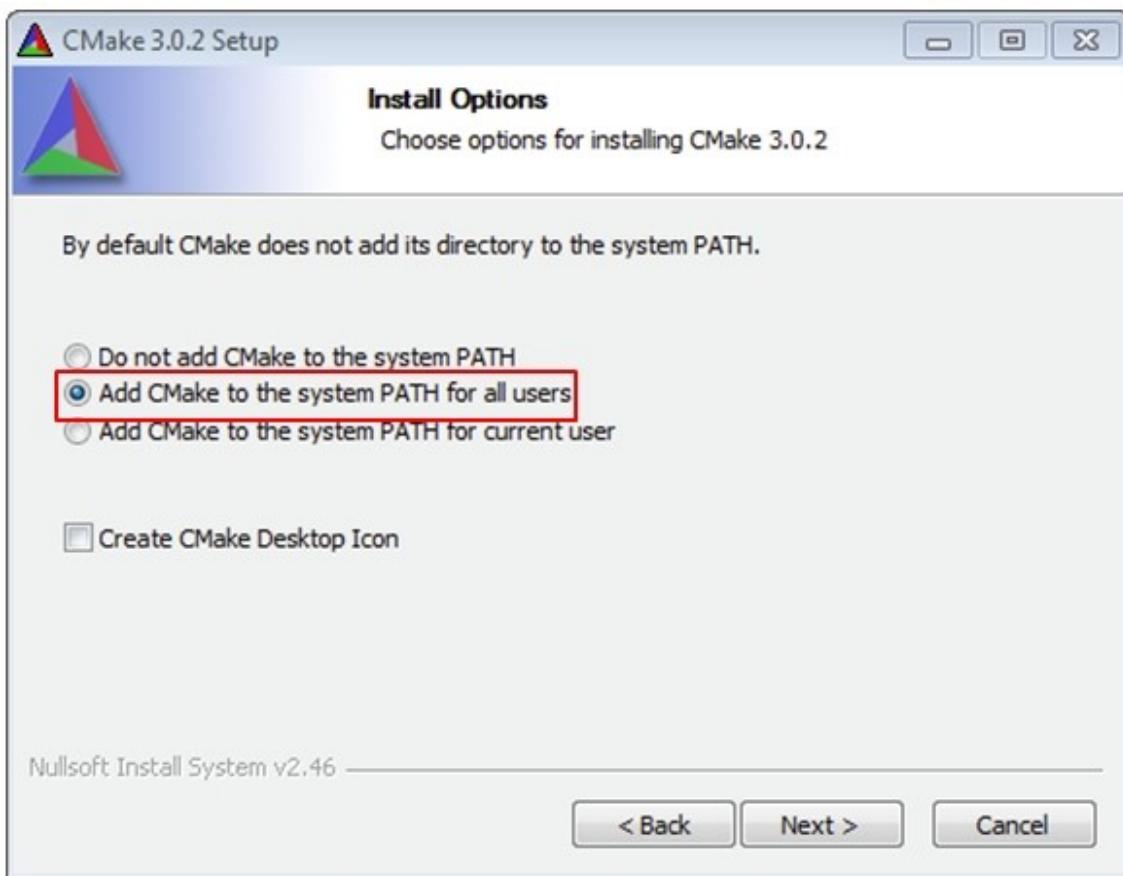

1. Download CMake 3.0.x from [www.cmake.org/cmake/resources/software.html](http://www.cmake.org/cmake/resources/software.html).

2. Install CMake, ensuring that the option **Add CMake to system PATH** is selected when installing. The user chooses to select whether it is installed into the PATH for all users or just the current user. In this example, it is installed for all users.

3. Follow the remaining instructions of the installer.

4. You may need to reboot your system for the PATH changes to take effect.

5. Make sure sh.exe is not in the Environment Variable PATH. This is a limitation of mingw32-make.

**Linux OS** It depends on the distributions of Linux Operation System. Here we use Ubuntu as an example.

Open shell and use following commands to install cmake and its version. Ensure the cmake version is above 3.0.x.

```

$ sudo apt-get install cmake

$ cmake --version

```

**Build an example application** To build an example application, follow these steps.

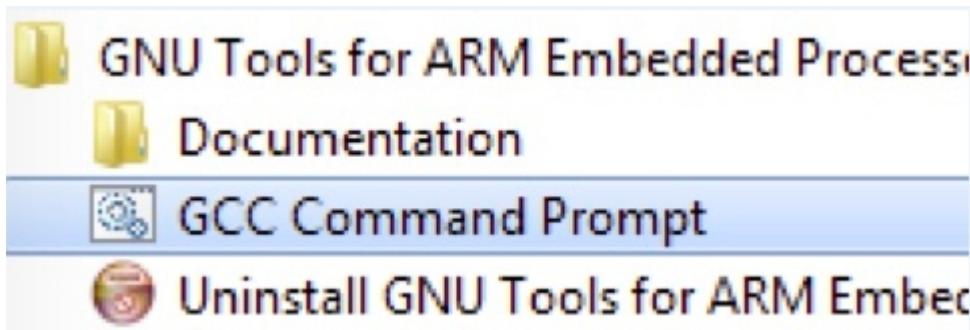

1. Open a GCC Arm Embedded tool chain command window. To launch the window, from the Windows operating system **Start** menu, go to **Programs > GNU Tools Arm Embedded <version>** and select **GCC Command Prompt**.

2. Change the directory to the example application project directory which has a path similar to the following:

```

<install_dir>/boards/<board_name>/<example_type>/<application_name>/armgcc

```

For this example, the exact path is:

**Note:** To change directories, use the `cd` command.

3. Type `build_debug.bat` on the command line or double click on `build_debug.bat` file in Windows Explorer to build it. The output is as shown in following figure.

```

[ 84%] Building C object CMakeFiles/hello_world.elf.dir/C:/nxp/SDK_2.0_FRDM-K64F/devices/MK64F12/drivers/fsl_smc.c.obj

[ 92%] Building C object CMakeFiles/hello_world.elf.dir/C:/nxp/SDK_2.0_FRDM-K64F/devices/MK64F12/drivers/fsl_clock.c.obj

[100%] Linking C executable debug\hello_world.elf

[100%] Built target hello_world.elf

C:\nxp\SDK_2.0_FRDM-K64F\boards\frdmk64f\demo_apps\hello_world\armgcc>IF "" == ""

"pause"

Press any key to continue . . .

```

**Run an example application** This section describes steps to run a demo application using J-Link GDB Server application. To install J-Link host driver and update the on-board debugger firmware to Jlink firmware, see [On-board debugger](#).

After the J-Link interface is configured and connected, follow these steps to download and run the demo applications:

1. Connect the development platform to your PC via USB cable between the on-board debugger USB connector and the PC USB connector. If using a standalone J-Link debug pod, connect it to the SWD/JTAG connector of the board.

2. Open the terminal application on the PC, such as PuTTY or TeraTerm, and connect to the debug serial port number (to determine the COM port number, see [How to determine COM port](#)). Configure the terminal with these settings:

1. 115200 or 9600 baud rate, depending on your board (reference BOARD\_DEBUG\_UART\_BAUDRATE variable in board.h file)

2. No parity

3. 8 data bits

4. 1 stop bit

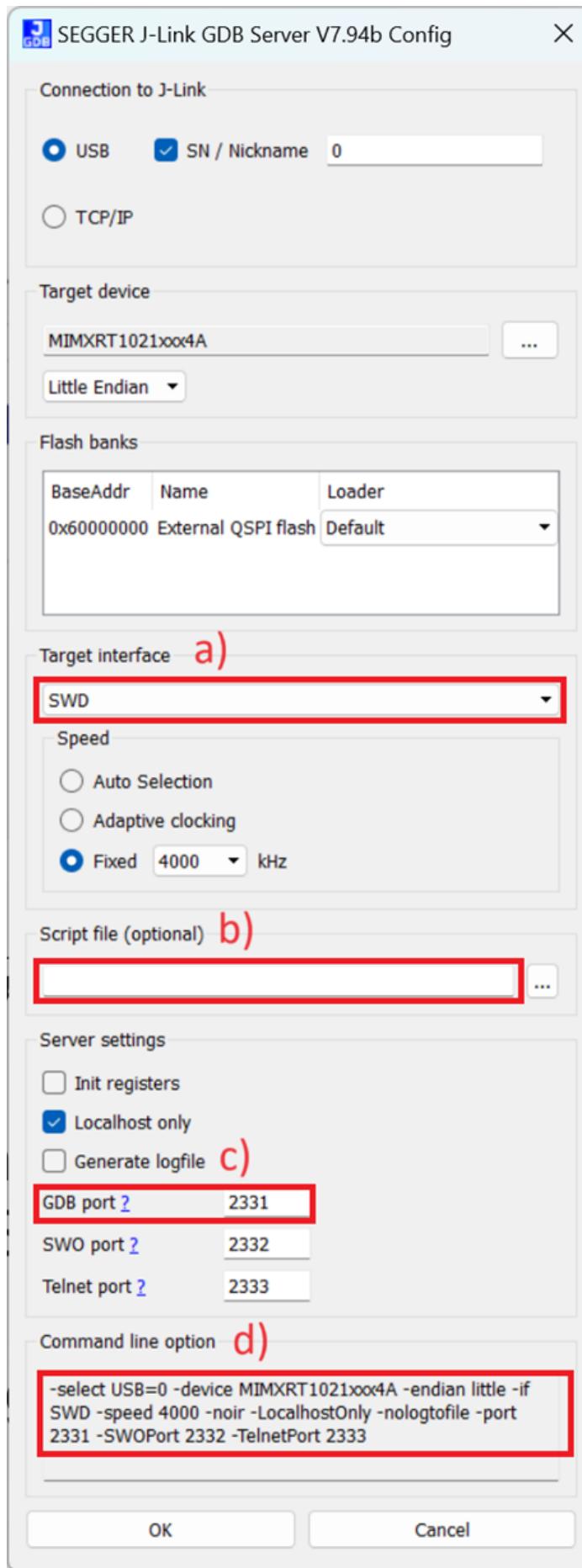

3. To launch the application, open the Windows **Start** menu and select **Programs > SEGGER > J-Link <version> J-Link GDB Server**.

**Note:** It is assumed that the J-Link software is already installed.

The **SEGGER J-Link GDB Server Config** settings dialog appears.

4. Make sure to check the following options.

1. **Target interface:** The debug connection on board uses internal SWD signaling. In case of a wrong setting J-Link is unable to communicate with device under test.

2. **Script file:** If required, a J-Link init script file can be used for board initialization. The file with the “.jlinkscript” file extension is located in the <install\_dir>/boards/<board\_name>/ directory.

3. Under the **Server settings**, check the GDB port for connection with the gdb target remote command. For more information, see step 9.

4. There is a command line version of J-Link GDB server “JLinkGDBServerCL.exe”. Typical path is C:\Program Files\SEGGER\JLink\. To start the J-Link GDB server with the same settings as are selected in the UI, you can use these command line options.

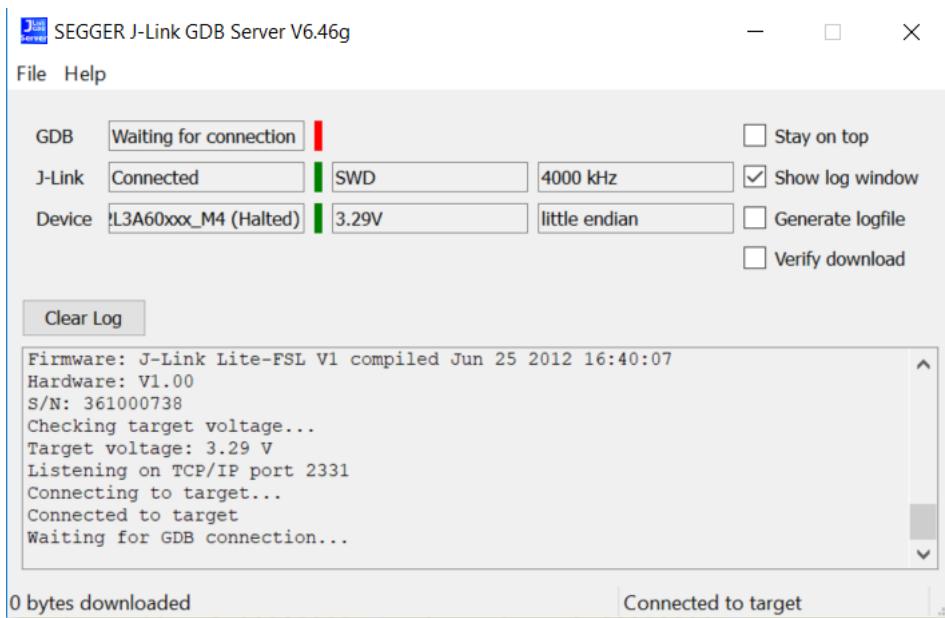

5. After it is connected, the screen should look like this figure:

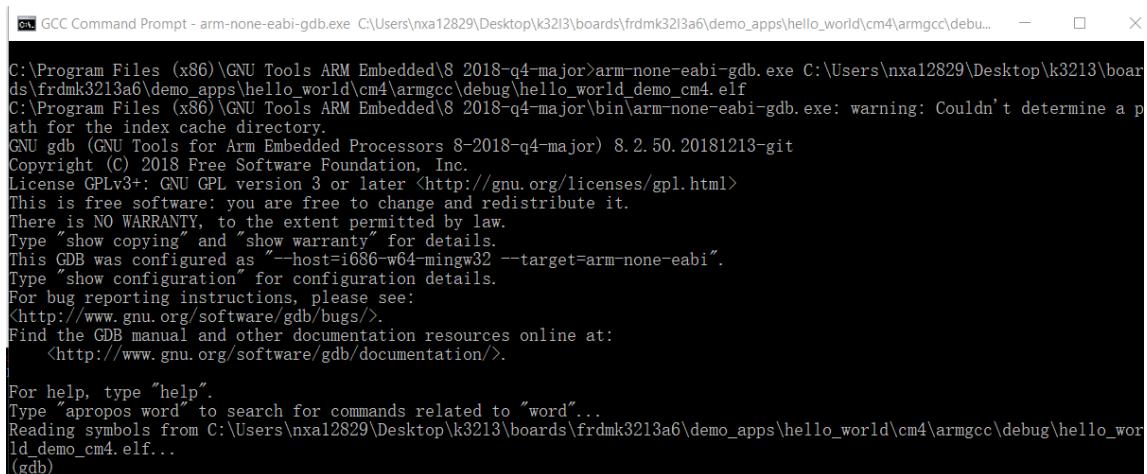

6. If not already running, open a GCC Arm Embedded tool chain command window. To launch the window, from the Windows operating system Start menu, go to **Programs - GNU Tools Arm Embedded <version>** and select **GCC Command Prompt**.

7. Change to the directory that contains the example application output. The output can be found in using one of these paths, depending on the build target selected:

<install\_dir>/boards/<board\_name>/<example\_type>/<application\_name>/armgcc/debug

<install\_dir>/boards/<board\_name>/<example\_type>/<application\_name>/armgcc/release

8. Run the `arm-none-eabi-gdb.exe <application_name>.elf` command. For this example, it is `arm-none-eabi-gdb.exe hello_world.elf`.

```

— □ ×

GCC Command Prompt - arm-none-eabi-gdb.exe C:\Users\nxa12829\Desktop\k3213\boards\frdmk3213a6\demo_apps\hello_world\cm4\armgcc\debug\hello_world_demo_cm4.elf

C:\Program Files (x86)\GNU Tools ARM Embedded\8 2018-q4-major>arm-none-eabi-gdb.exe C:\Users\nxa12829\Desktop\k3213\boards\frdmk3213a6\demo_apps\hello_world\cm4\armgcc\debug\hello_world_demo_cm4.elf

C:\Program Files (x86)\GNU Tools ARM Embedded\8 2018-q4-major\bin\arm-none-eabi-gdb.exe: warning: Couldn't determine a path for the index cache directory.

GNU gdb (GNU Tools for Arm Embedded Processors 8-2018-q4-major) 8.2.50.20181213-git

Copyright (C) 2018 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law.

Type "show copying" and "show warranty" for details.

This GDB was configured as "--host=i686-w64-mingw32 --target=arm-none-eabi".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

<http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word"...

Reading symbols from C:\Users\nxa12829\Desktop\k3213\boards\frdmk3213a6\demo_apps\hello_world\cm4\armgcc\debug\hello_world_demo_cm4.elf...

(gdb)

```

### 9. Run these commands:

1. target remote localhost:2331

2. monitor reset

3. monitor halt

4. load

5. monitor reset

### 10. The application is now downloaded and halted. Execute the monitor go command to start the demo application.

The hello\_world application is now running and a banner is displayed on the terminal. If this does not appear, check your terminal settings and connections.

```

— □ ×

COM4 - PuTTY

hello world.

█

```

**Build a multicore example application** This section describes the steps to build and run a dual-core application. The demo application build scripts are located in this folder:

```

<install_dir>/boards/<board_name>/multicore_examples/<application_name>/<core_type>/armgcc

```

Begin with a simple dual-core version of the Hello World application. The multicore Hello World GCC build scripts are located in this folder:

```

<install_dir>/boards/lpcxpresso54114/multicore_examples/hello_world/cm0plus/armgcc/build_debug.bat

```

```

<install_dir>/boards/lpcxpresso54114/multicore_examples/hello_world/cm4/armgcc/build_debug.bat

```

Build both applications separately following steps for single core examples as described in **Build an example application**.

```

ca: GCC Command Prompt - build_debug.bat

[ 47%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/drivers/fsl_common.c.obj

[ 52%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/drivers/fsl_msmc.c.obj

[ 56%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/debug_console/fsl_debug_console.c.obj

[ 60%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/fsl_assert.c.obj

[ 65%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/str/fsl_str.c.obj

[ 69%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/uart/lpuart_adapter.c.obj

[ 73%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/serial_manager/serial_manager.c.obj

[ 78%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/serial_manager/serial_port_uart.c.obj

[ 82%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/lists/generic_list.c.obj

[ 86%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/system_K32L3A60_cm0plus.c.obj

[ 91%] Building ASM object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/gcc/startup_K32L3A60_cm0plus.S.obj

[ 95%] Building C object CMakeFiles/hello_world_cm0plus.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/middleware/multicore/mcmgr/src/mcmgr.c.obj

[100%] Linking C executable debug\hello_world_cm0plus.elf

[100%] Built target hello_world_cm0plus.elf

c:\packages\SDK_2.6.0_FRDM-K32L3A6_RC1\boards\frdmk32l3a6\multicore_examples\hello_world\cm0plus\armgcc>IF "" == "" (pause)

Press any key to continue . . .

```

```

ca: GCC Command Prompt - build_debug.bat

[ 50%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/drivers/fsl_lpuart.c.obj

[ 54%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/drivers/fsl_common.c.obj

[ 58%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/drivers/fsl_msmc.c.obj

[ 62%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/str/fsl_str.c.obj

[ 66%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/fsl_assert.c.obj

[ 70%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/utilities/debug_console/fsl_debug_console.c.obj

[ 75%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/uart/lpuart_adapter.c.obj

[ 79%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/serial_manager/serial_port_uart.c.obj

[ 83%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/serial_manager/serial_manager.c.obj

[ 87%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/components/lists/generic_list.c.obj

[ 91%] Building C object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/system_K32L3A60_cm4.c.obj

[ 95%] Building ASM object CMakeFiles/hello_world_cm4.elf.dir/C:/packages/SDK_2.6.0_FRDM-K32L3A6_RC1/devices/K32L3A60/gcc/startup_K32L3A60_cm4.S.obj

[100%] Linking C executable debug\hello_world_cm4.elf

[100%] Built target hello_world_cm4.elf

c:\packages\SDK_2.6.0_FRDM-K32L3A6_RC1\boards\frdmk32l3a6\multicore_examples\hello_world\cm4\armgcc>IF "" == "" (pause)

Press any key to continue . . .

```

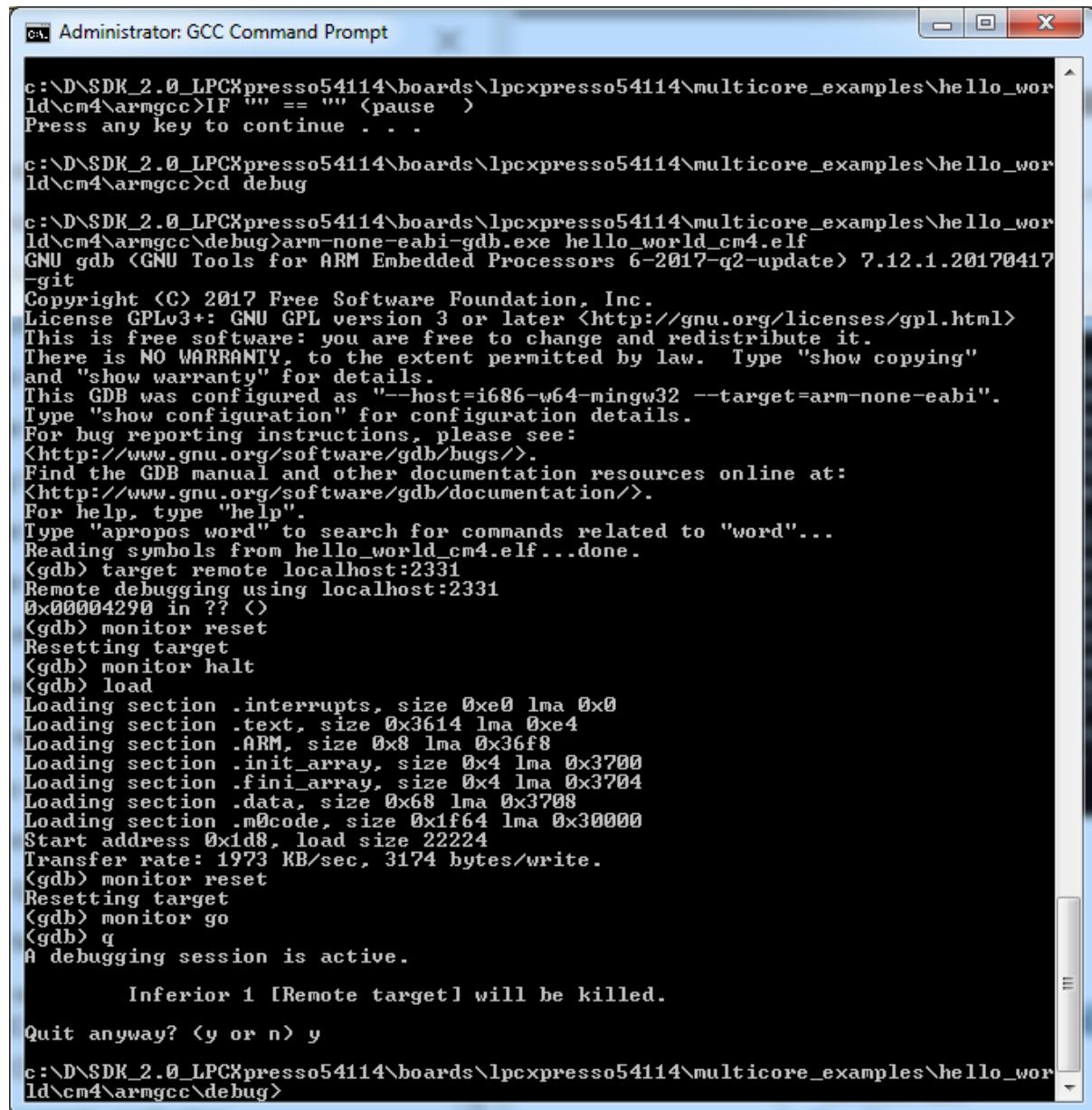

**Run a multicore example application** When running a multicore application, the same prerequisites for J-Link/J-Link OpenSDA firmware, and the serial console as for the single-core application, applies, as described in **Run an example application**.

The primary core debugger handles flashing of both the primary and the auxiliary core applications into the SoC flash memory. To download and run the multicore application, switch to the primary core application project and perform steps 1 to 10, as described in **Run an example application**. These steps are common for both single-core and dual-core applications in Arm GCC.

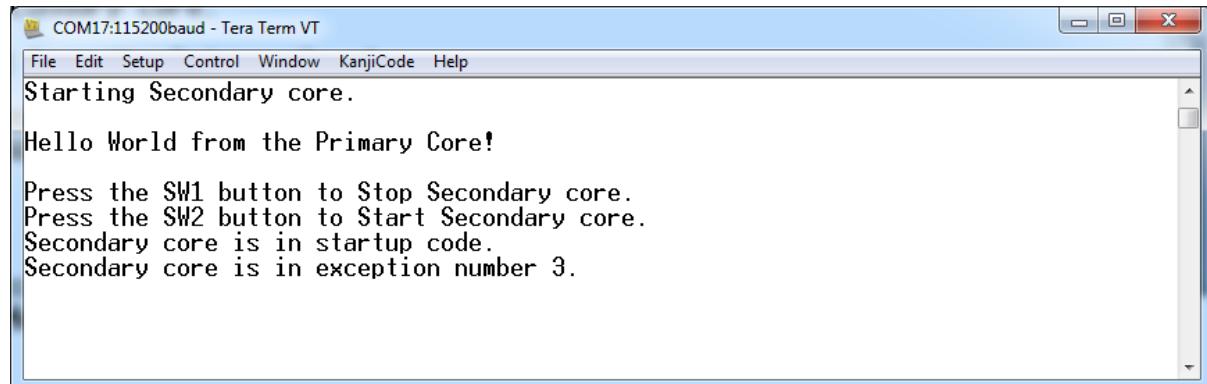

Both the primary and the auxiliary image is loaded into the SPI flash memory. After execution of the monitor go command, the primary core application is executed. During the primary core code execution, the auxiliary core code is reallocated from the flash memory to the RAM, and the auxiliary core is released from the reset. The hello\_world multicore application is now running

and a banner is displayed on the terminal. If this is not true, check your terminal settings and connections.

```

Administrator: GCC Command Prompt

c:\D\SDK_2.0_LPCXpresso54114\boards\lpcxpresso54114\multicore_examples\hello_world\cm4\armgcc>IF "" == "" <pause>

Press any key to continue . . .

c:\D\SDK_2.0_LPCXpresso54114\boards\lpcxpresso54114\multicore_examples\hello_world\cm4\armgcc>cd debug

c:\D\SDK_2.0_LPCXpresso54114\boards\lpcxpresso54114\multicore_examples\hello_world\cm4\armgcc\debug>arm-none-eabi-gdb.exe hello_world_cm4.elf

GNU gdb (GNU Tools for ARM Embedded Processors 6-2017-q2-update) 7.12.1.20170417-git

Copyright (C) 2017 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law. Type "show copying"

and "show warranty" for details.

This GDB was configured as "--host=i686-w64-mingw32 --target=arm-none-eabi".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

<http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word"...

Reading symbols from hello_world_cm4.elf...done.

(gdb) target remote localhost:2331

Remote debugging using localhost:2331

0x00004290 in ?? { }

(gdb) monitor reset

Resetting target

(gdb) monitor halt

(gdb) load

Loading section .interrupts, size 0xe0 lma 0x0

Loading section .text, size 0x3614 lma 0xe4

Loading section .ARM, size 0x8 lma 0x36f8

Loading section .init_array, size 0x4 lma 0x3700

Loading section .fini_array, size 0x4 lma 0x3704

Loading section .data, size 0x68 lma 0x3708

Loading section .m0code, size 0x1f64 lma 0x30000

Start address 0x1d8, load size 22224

Transfer rate: 1973 KB/sec, 3174 bytes/write.

(gdb) monitor reset

Resetting target

(gdb) monitor go

(gdb) q

A debugging session is active.

Inferior 1 [Remote target] will be killed.

Quit anyway? <y or n> y

c:\D\SDK_2.0_LPCXpresso54114\boards\lpcxpresso54114\multicore_examples\hello_world\cm4\armgcc\debug>

```

```

COM17:115200baud - Tera Term VT

File Edit Setup Control Window KanjiCode Help

Starting Secondary core.

Hello World from the Primary Core!

Press the SW1 button to Stop Secondary core.

Press the SW2 button to Start Secondary core.

Secondary core is in startup code.

Secondary core is in exception number 3.

```

**Build a TrustZone example application** This section describes the steps to build and run a TrustZone application. The demo application build scripts are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/[<core_type>]/

→<application_name>_ns/armgcc

```

```

<install_dir>/boards/<board_name>/trustzone_examples/<application_name>/[<core_type>]/

→<application_name>_s/armgcc

```

Begin with a simple TrustZone version of the Hello World application. The TrustZone Hello World GCC build scripts are located in this folder:

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_ns/armgcc/build_

→debug.bat

```

```

<install_dir>/boards/<board_name>/trustzone_examples/hello_world/hello_world_s/armgcc/build_

→debug.bat

```

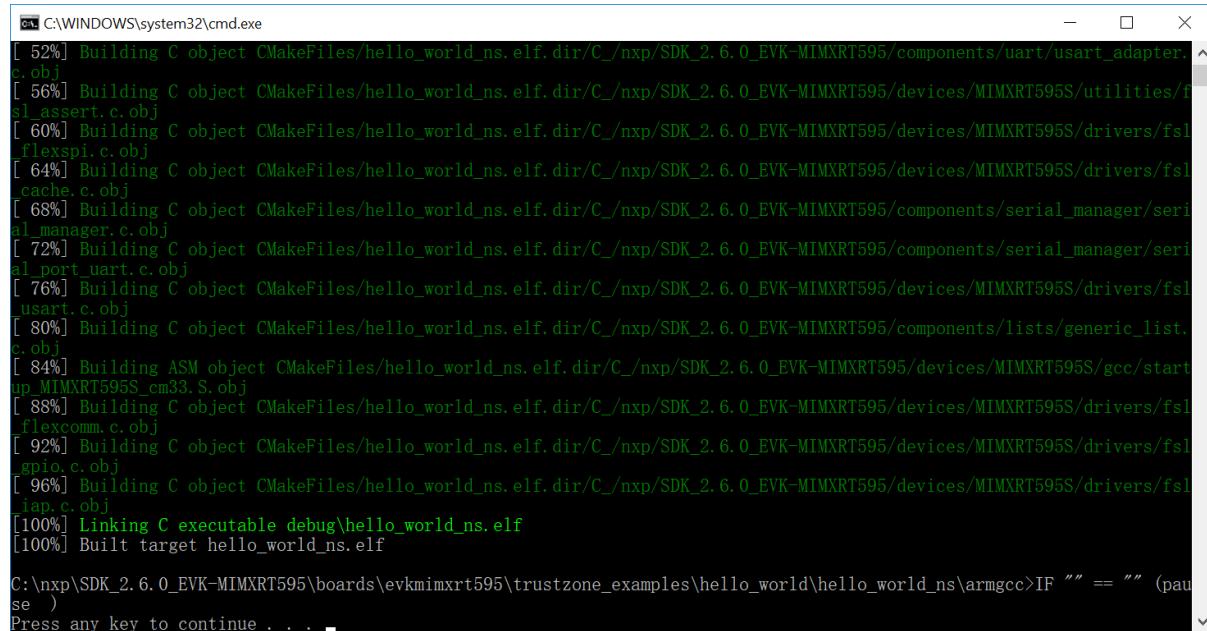

Build both applications separately, following steps for single core examples as described in **Build an example application**. It is requested to build the application for the secure project first, because the non-secure project must know the secure project, since CMSE library is running the linker. It is not possible to finish the non-secure project linker with the secure project because the CMSE library is not ready.

```

C:\WINDOWS\system32\cmd.exe

[ 55%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/utilities/fs...

l_assert.c.obj

[ 59%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/uart/usart_adapter.c...

.obj

[ 62%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

flexspi.c.obj

[ 66%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

cache.c.obj

[ 70%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/serial_manager/seria...

l_manager.c.obj

[ 74%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/serial_manager/seria...

l_port_uart.c.obj

[ 77%] Building ASM object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/gcc/startu...

p_MIMXRT595S_cm33.S.obj

[ 81%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/lists/generic_list.c...

.obj

[ 85%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

usart.c.obj

[ 88%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

flexcomm.c.obj

[ 92%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

gpio.c.obj

[ 96%] Building C object CMakeFiles/hello_world_s.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl...

iap.c.obj

[100%] Linking C executable debug\hello_world_s.elf

[100%] Built target hello_world_s.elf

C:\nxp\SDK_2.6.0_EVK-MIMXRT595\boards\evkmimxrt595\trustzone_examples\hello_world\hello_world_s\armgcc>IF "" == "" (pause)

Press any key to continue . . .

```

```

C:\WINDOWS\system32\cmd.exe

[ 52%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/uart/usart_adapter.c.obj

[ 56%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/utilities/fsi_assert.c.obj

[ 60%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_flexspi.c.obj

[ 64%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_cache.c.obj

[ 68%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/serial_manager/serial_manager.c.obj

[ 72%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/serial_manager/serial_port_uart.c.obj

[ 76%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_usart.c.obj

[ 80%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/components/lists/generic_list.c.obj

[ 84%] Building ASM object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/gcc/startup_MIMXRT595S_cm33.S.obj

[ 88%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_flexcomm.c.obj

[ 92%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_gpio.c.obj

[ 96%] Building C object CMakeFiles/hello_world_ns.elf.dir/C_nxp/SDK_2.6.0_EVK-MIMXRT595/devices/MIMXRT595S/drivers/fsl_iap.c.obj

[100%] Linking C executable debug\hello_world_ns.elf

[100%] Built target hello_world_ns.elf

C:\nxp/SDK_2.6.0_EVK-MIMXRT595\boards\evkmimxrt595\trustzone_examples\hello_world\hello_world_ns\armgcc>IF "" == "" (pause)

Press any key to continue . . .

```

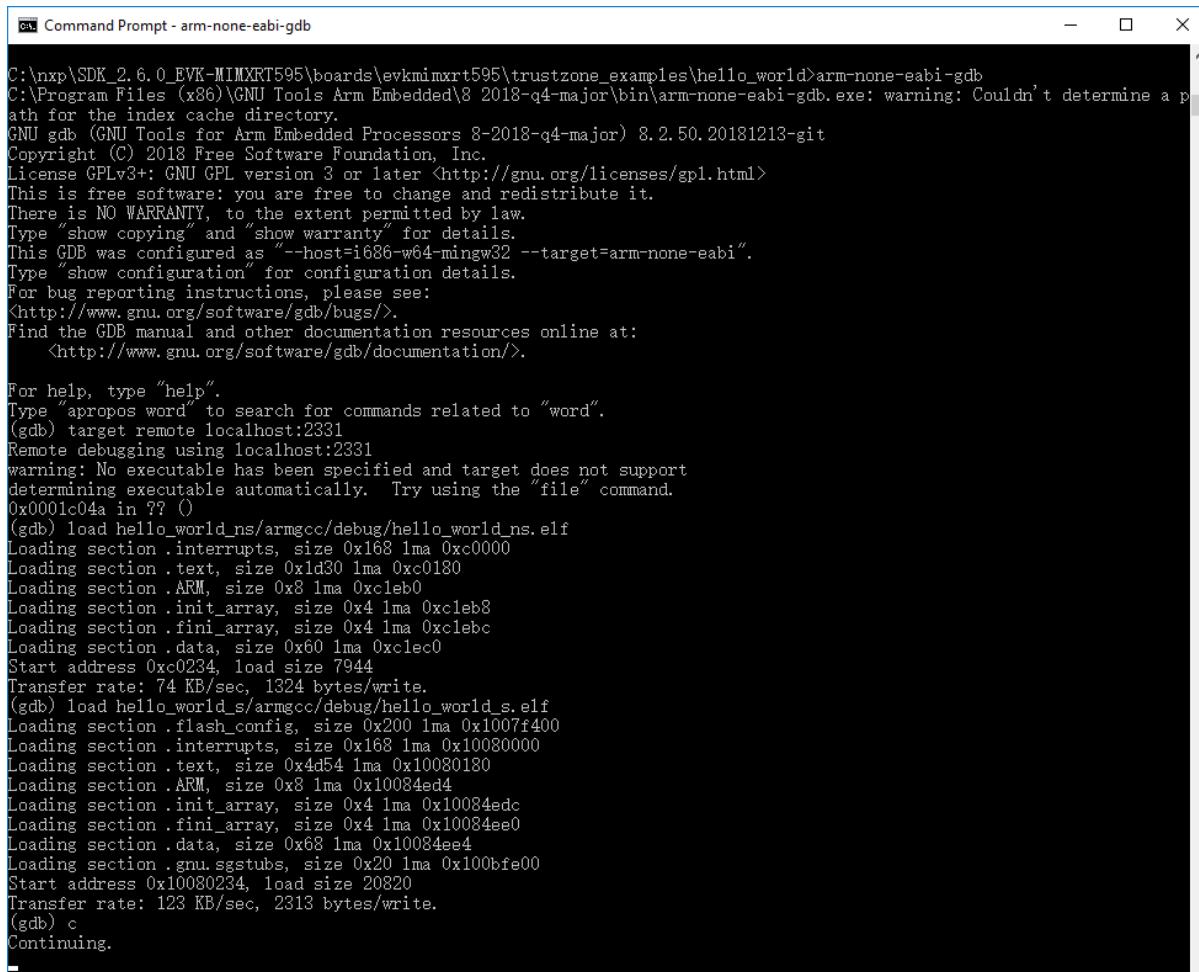

**Run a TrustZone example application** When running a TrustZone application, the same prerequisites for J-Link/J-Link OpenSDA firmware, and the serial console as for the single core application, apply, as described in [Run an example application](#).

To download and run the TrustZone application, perform steps 1 to 10, as described in [Run an example application](#). These steps are common for both single core and TrustZone applications in Arm GCC.

Then, run these commands:

1. arm-none-eabi-gdb.exe

2. target remote localhost:2331

3. monitor reset

4. monitor halt

5. monitor exec SetFlashDLNoRMWThreshold = 0x20000

6. load <install\_dir>/boards/evkmimxrt595/trustzone\_examples/hello\_world/hello\_world\_ns/armgcc/debug/hello\_world\_ns.elf

7. load <install\_dir>/boards/evkmimxrt595/trustzone\_examples/hello\_world/hello\_world\_s/armgcc/debug/hello\_world\_s.elf

8. monitor reset

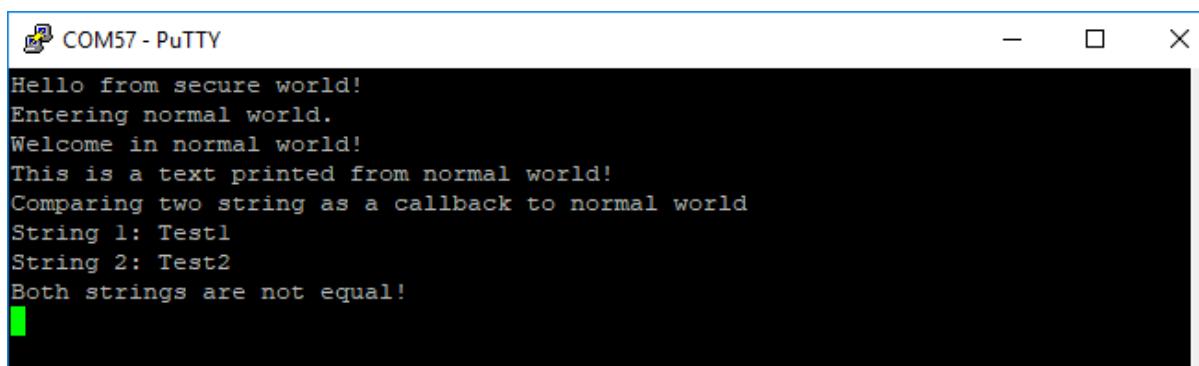

The application is now downloaded and halted. Execute the `c` command to start the demo application.

```

C:\npx\SDK_2.6.0_EVK-MIMXRT595\boards\evkmmimxrt595\trustzone_examples\hello_world\arm-none-eabi-gdb

C:\Program Files (x86)\GNU Tools Arm Embedded\8 2018-q4-major\bin\arm-none-eabi-gdb.exe: warning: Couldn't determine a path for the index cache directory.

GNU gdb (GNU Tools for Arm Embedded Processors 8-2018-q4-major) 8.2.50.20181213-git

Copyright (C) 2018 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law.

Type "show copying" and "show warranty" for details.

This GDB was configured as "--host=i686-w64-mingw32 --target=arm-none-eabi".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

<http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word".

(gdb) target remote localhost:2331

Remote debugging using localhost:2331

warning: No executable has been specified and target does not support

determining executable automatically. Try using the "file" command.

0x0001c04a in ?? ()

(gdb) load hello_world_ns/armgcc/debug/hello_world_ns.elf

Loading section .interrupts, size 0x168 lma 0xc0000

Loading section .text, size 0x1d30 lma 0xc0180

Loading section .ARM, size 0x8 lma 0xc1eb0

Loading section .init_array, size 0x4 lma 0xc1eb8

Loading section .fini_array, size 0x4 lma 0xc1ebc

Loading section .data, size 0x60 lma 0xc1ec0

Start address 0xc0234, load size 7944

Transfer rate: 74 KB/sec, 1324 bytes/write.

(gdb) load hello_world_s/armgcc/debug/hello_world.s.elf

Loading section .flash_config, size 0x200 lma 0x1007f400

Loading section .interrupts, size 0x168 lma 0x10080000

Loading section .text, size 0x4d54 lma 0x10080180

Loading section .ARM, size 0x8 lma 0x10084ed4

Loading section .init_array, size 0x4 lma 0x10084edc

Loading section .fini_array, size 0x4 lma 0x10084ee0

Loading section .data, size 0x68 lma 0x10084ee4

Loading section .gnu.sgstubs, size 0x20 lma 0x100bfe00

Start address 0x10080234, load size 20820

Transfer rate: 123 KB/sec, 2313 bytes/write.

(gdb) c

Continuing.

```

```

Hello from secure world!

Entering normal world.

Welcome in normal world!

This is a text printed from normal world!

Comparing two string as a callback to normal world

String 1: Test1

String 2: Test2

Both strings are not equal!

```

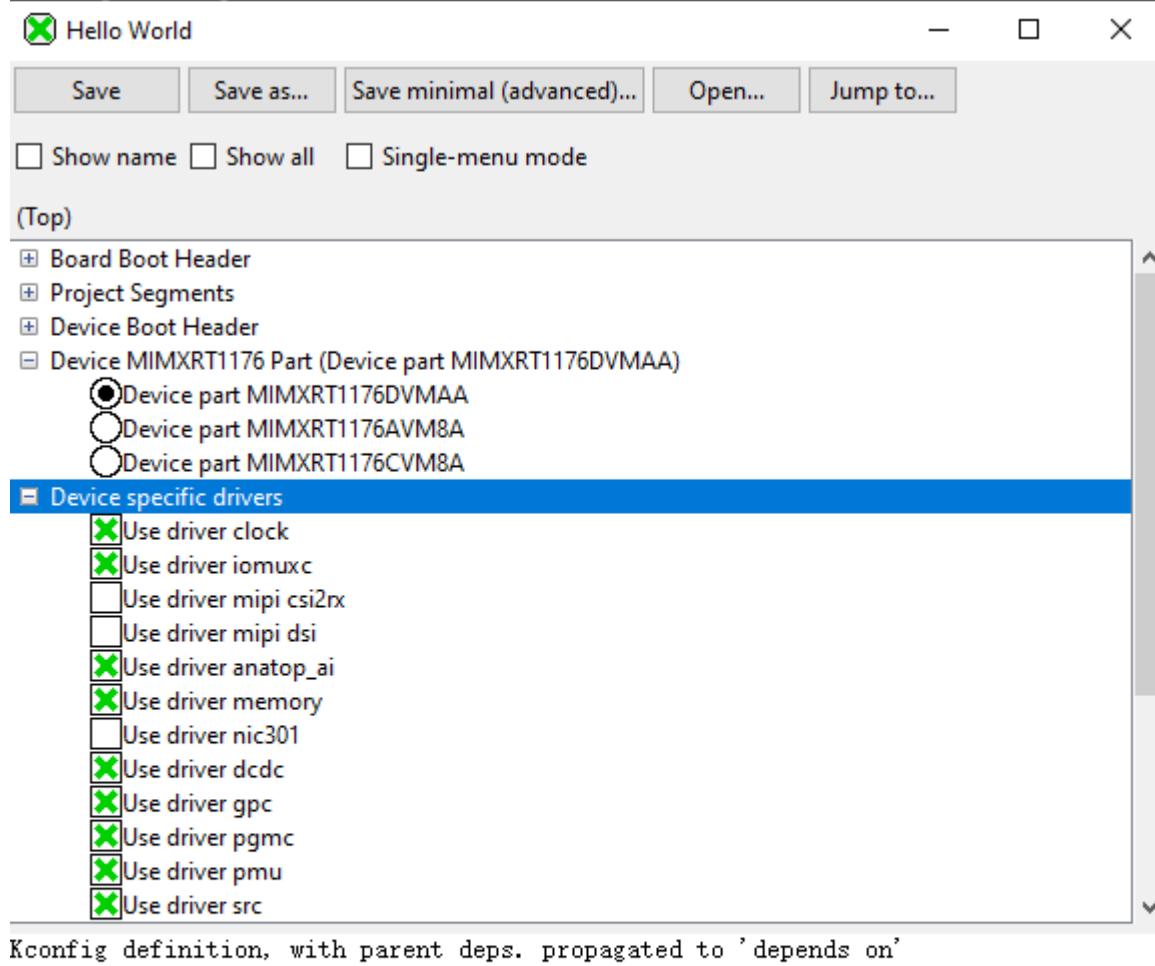

## MCUXpresso Config Tools

MCUXpresso Config Tools can help configure the processor and generate initialization code for the on chip peripherals. The tools are able to modify any existing example project, or create a new configuration for the selected board or processor. The generated code is designed to be used with MCUXpresso SDK version 24.12.00 or later.

Following table describes the tools included in the MCUXpresso Config Tools.

| Config Tool                      | Description                                                                                                                                                                    | Image                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <b>Pins tool</b>                 | For configuration of pin routing and pin electrical properties.                                                                                                                |  |

| <b>Clock tool</b>                | For system clock configuration                                                                                                                                                 |  |

| <b>Peripherals tools</b>         | For configuration of other peripherals                                                                                                                                         |  |

| <b>TEE tool</b>                  | Configures access policies for memory area and peripherals helping to protect and isolate sensitive parts of the application.                                                  |  |

| <b>Device Configuration tool</b> | Configures Device Configuration Data (DCD) contained in the program image that the Boot ROM code interprets to set up various on-chip peripherals prior to the program launch. |  |

MCUXpresso Config Tools can be accessed in the following products:

- **Integrated** in the MCUXpresso IDE. Config tools are integrated with both compiler and debugger which makes it the easiest way to begin the development.

- **Standalone version** available for download from [www.nxp.com/mcuxpresso](http://www.nxp.com/mcuxpresso). Recommended for customers using IAR Embedded Workbench, Keil MDK µVision, or Arm GCC.

- **Online version** available on [mcuxpresso.nxp.com](http://mcuxpresso.nxp.com). Recommended doing a quick evaluation of the processor or use the tool without installation.

Each version of the product contains a specific *Quick Start Guide* document MCUXpresso IDE Config Tools installation folder that can help start your work.

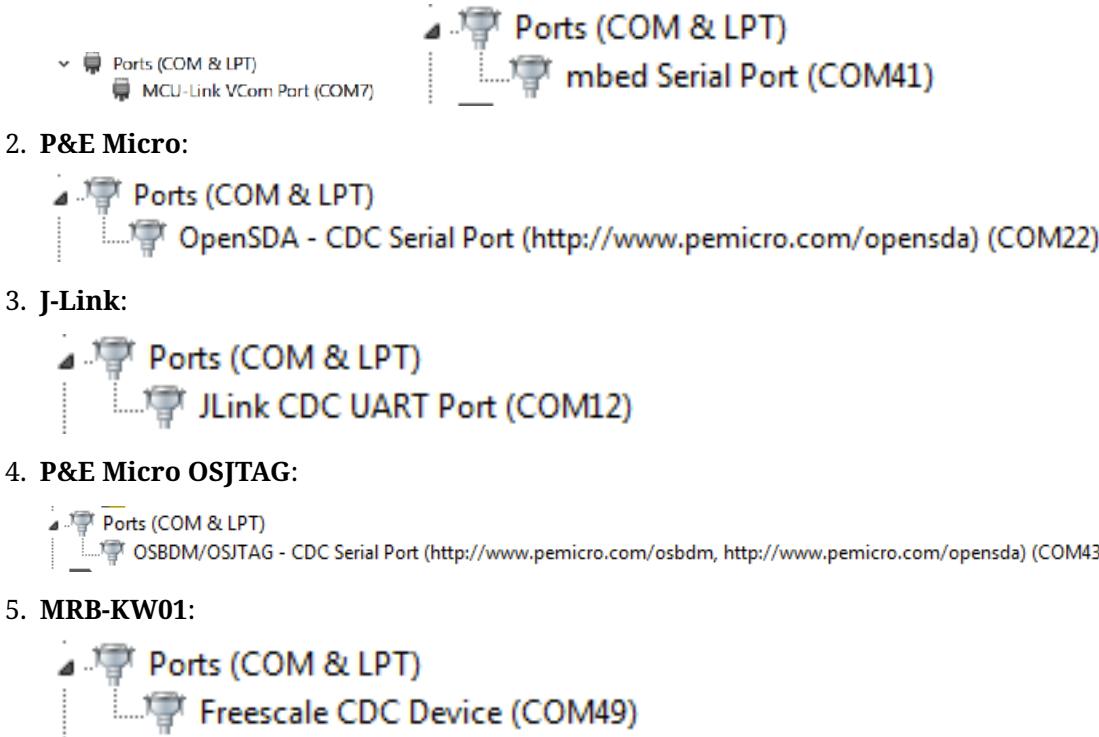

## How to determine COM port

This section describes the steps necessary to determine the debug COM port number of your NXP hardware development platform. All NXP boards ship with a factory programmed, onboard debug interface, whether it is based on MCU-Link or the legacy OpenSDA, LPC-Link2, P&E Micro OSJTAG interface. To determine what your specific board ships with, see [Default debug interfaces](#).

1. **Linux:** The serial port can be determined by running the following command after the USB Serial is connected to the host:

```

$ dmesg | grep "ttyUSB"

[503175.307873] usb 3-12: cp210x converter now attached to ttyUSB0

[503175.309372] usb 3-12: cp210x converter now attached to ttyUSB1

```

There are two ports, one is for core0 debug console and the other is for core1.

2. **Windows:** To determine the COM port open Device Manager in the Windows operating system. Click the Start menu and type **Device Manager** in the search bar.

In the Device Manager, expand the **Ports (COM & LPT)** section to view the available ports. The COM port names are different for all the NXP boards.

1. **CMSIS-DAP/mbed/DAPLink interface:**

## On-board Debugger

This section describes the on-board debuggers used on NXP development boards.

**On-board debugger MCU-Link** MCU-Link is a powerful and cost effective debug probe that can be used seamlessly with MCUXpresso IDE, and is also compatible with 3rd party IDEs that support CMSIS-DAP protocol. MCU-Link also includes a USB to UART bridge feature (VCOM) that can be used to provide a serial connection between the target MCU and a host computer. MCU-Link features a high-speed USB interface for high performance debug. MCU-Link is compatible with Windows, MacOS and Linux. A free utility from NXP provides an easy way to install firmware updates.

On-board MCU-Link debugger supports CMSIS-DAP and J-Link firmware. See the table in [Default debug interfaces](#) to determine the default debug interface that comes loaded on your specific hardware platform.

**The corresponding host driver must be installed before debugging.**

- For boards with CMSIS-DAP firmware, visit [developer.mbed.org/handbook/Windows-serial-configuration](http://developer.mbed.org/handbook/Windows-serial-configuration) and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- If using J-Link with either a standalone debug pod or MCU-Link, install the J-Link software (drivers and utilities) from [www.segger.com/jlink-software.html](http://www.segger.com/jlink-software.html).

**Updating MCU-Link firmware** This firmware in this debug interface may be updated using the host computer utility called MCU-Link. This typically used when switching between the default debugger protocol (CMSIS-DAP) to SEGGER J-Link, or for updating this firmware with new releases of these. This section contains the steps to reprogram the debug probe firmware.

**Note:** If MCUXpresso IDE is used and the jumper making DFUlink is installed on the board (JP5 on some boards, but consult the board user manual or schematic for specific jumper number), MCU-Link debug probe boots to DFU mode, and MCUXpresso IDE automatically downloads the

CMSIS-DAP firmware to the probe before flash memory programming (after clicking **Debug**). Using DFU mode ensures that most up-to-date/compatible firmware is used with MCUXpresso IDE.

NXP provides the MCU-Link utility, which is the recommended tool for programming the latest versions of CMSIS-DAP and J-Link firmware onto MCU-Link or NXP boards. The utility can be downloaded from [MCU-Link](#).

These steps show how to update the debugger firmware on your board for Windows operating system.

1. Install the MCU-Link utility.

2. Unplug the board's USB cable.

3. Make the DFU link (install the jumper labeled DFUlink).

4. Connect the probe to the host via USB (use Link USB connector).

5. Open a command shell and call the appropriate script located in the MCU-Link installation directory (<MCU-Link install dir>).

1. To program CMSIS-DAP debug firmware: <MCU-Link install dir>/scripts/program\_CMSIS

2. To program J-Link debug firmware: <MCU-Link install dir>/scripts/program\_JLINK

6. Remove DFU link (remove the jumper installed in Step 3).

7. Repower the board by removing the USB cable and plugging it in again.

**On-board debugger LPC-Link** LPC-Link 2 is an extensible debug probe that can be used seamlessly with MCUXpresso IDE, and is also compatible with 3rd party IDEs that support CMSIS-DAP protocol. MCU-Link also includes a USB to UART bridge feature (VCOM) that can be used to provide a serial connection between the target MCU and a host computer. LPC-Link 2 is compatible with Windows, MacOS and Linux. A free utility from NXP provides an easy way to install firmware updates.

On-board LPC-Link 2 debugger supports CMSIS-DAP and J-Link firmware. See the table in [Default debug interfaces](#) to determine the default debug interface that comes loaded on your specific hardware platform.

**The corresponding host driver must be installed before debugging.**

- For boards with CMSIS-DAP firmware, visit [developer.mbed.org/handbook/Windows-serial-configuration](#) and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- If using J-Link with either a standalone debug pod or MCU-Link, install the J-Link software (drivers and utilities) from [www.segger.com/jlink-software.html](#).

**Updating LPC-Link firmware** The LPCXpresso hardware platform comes with a CMSIS-DAP-compatible debug interface (known as LPC-Link2). This firmware in this debug interface may be updated using the host computer utility called LPCScrypt. This typically used when switching between the default debugger protocol (CMSIS-DAP) to SEGGER J-Link, or for updating this firmware with new releases of these. This section contains the steps to reprogram the debug probe firmware.

**Note:** If MCUXpresso IDE is used and the jumper making DFUlink is installed on the board (JP5 on some boards, but consult the board user manual or schematic for specific jumper number), LPC-Link2 debug probe boots to DFU mode, and MCUXpresso IDE automatically downloads the CMSIS-DAP firmware to the probe before flash memory programming (after clicking **Debug**). Using DFU mode ensures that most up-to-date/compatible firmware is used with MCUXpresso IDE.

NXP provides the LPCScrypt utility, which is the recommended tool for programming the latest versions of CMSIS-DAP and J-Link firmware onto LPC-Link2 or MCUXpresso boards. The utility can be downloaded from [LPCScrypt](#).

These steps show how to update the debugger firmware on your board for Windows operating system. For Linux OS, follow the instructions described in [LPCScrypt user guide](#) ([LPCScrypt](#), select **LPCScrypt**, and then the documentation tab).

1. Install the LPCScript utility.

2. Unplug the board's USB cable.

3. Make the DFU link (install the jumper labeled DFUlink).

4. Connect the probe to the host via USB (use Link USB connector).

5. Open a command shell and call the appropriate script located in the LPCScrypt installation directory (<LPCScrypt install dir>).

1. To program CMSIS-DAP debug firmware: <LPCScrypt install dir>/scripts/program\_CMSIS

2. To program J-Link debug firmware: <LPCScrypt install dir>/scripts/program\_JLINK

6. Remove DFU link (remove the jumper installed in Step 3).

7. Repower the board by removing the USB cable and plugging it in again.

**On-board debugger OpenSDA** OpenSDA/OpenSDAv2 is a serial and debug adapter that is built into several NXP evaluation boards. It provides a bridge between your computer (or other USB host) and the embedded target processor, which can be used for debugging, flash programming, and serial communication, all over a simple USB cable.

The difference is the firmware implementation: OpenSDA: Programmed with the proprietary P&E Micro developed bootloader. P&E Micro is the default debug interface app. OpenSDAv2: Programmed with the open-sourced CMSIS-DAP/mbed bootloader. CMSIS-DAP is the default debug interface app.

See the table in [Default debug interfaces](#) to determine the default debug interface that comes loaded on your specific hardware platform.

**The corresponding host driver must be installed before debugging.**

- For boards with CMSIS-DAP firmware, visit [developer.mbed.org/handbook/Windows-serial-configuration](#) and follow the instructions to install the Windows operating system serial driver. If running on Linux OS, this step is not required.

- For boards with a P&E Micro interface, see [PE micro](#) to download and install the P&E Micro Hardware Interface Drivers package.

**Updating OpenSDA firmware** Any NXP hardware platform that comes with an OpenSDA-compatible debug interface has the ability to update the OpenSDA firmware. This typically means to switch from the default application (either CMSIS-DAP or P&E Micro) to a SEGGER J-Link. This section contains the steps to switch the OpenSDA firmware to a J-Link interface. However, the steps can be applied to restoring the original image also. For reference, OpenSDA firmware files can be found at the links below:

- J-Link: Download appropriate image from [www.segger.com/opensda.html](#). Choose the appropriate J-Link binary based on the table in [Default debug interfaces](#). Any OpenSDA v1.0 interface should use the standard OpenSDA download (in other words, the one with no version). For OpenSDA 2.0 or 2.1, select the corresponding binary.

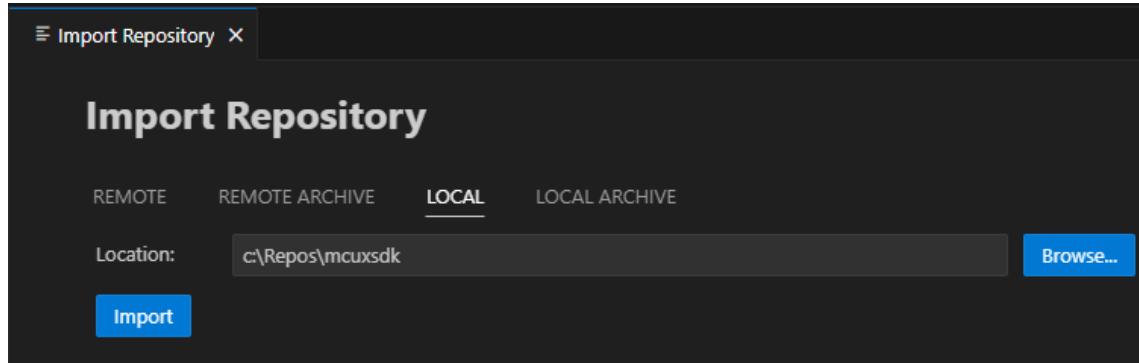

- CMSIS-DAP: CMSIS-DAP OpenSDA firmware is available at [www.nxp.com/opensda](#).